### A Reconfigurable Accelerator Card for High Performance Computing

### Michael James Aitken

Supervisor: Professor Michael Inggs Co-supervisor: Dr Alan Langman

A dissertation submitted to the Department of Electrical Engineering in fulfillment of the requirements for the degree of

Master of Science in Electrical Engineering

at the

UNIVERSITY OF CAPE TOWN

November 2008

The copyright of this thesis vests in the author. No quotation from it or information derived from it is to be published without full acknowledgement of the source. The thesis is to be used for private study or non-commercial research purposes only.

Published by the University of Cape Town (UCT) in terms of the non-exclusive license granted to UCT by the author.

### Declaration

I know the meaning of plagiarism and declare that all the work in this thesis, save for that which is properly acknowledged, is my own. It is being submitted for the degree of Master of Science in Electrical Engineering at the University of Cape Town. It has not been submitted before for any degree or examination in any other university.

Signature of Author.....

Cape Town 25th November 2008

### Abstract

This thesis describes the design, implementation, and testing of a reconfigurable accelerator card. The goal of the project was to provide a hardware platform for future students to carry out research into reconfigurable computing.

Our accelerator design is an expansion card for a traditional Von Neumann host machine, and contains two field-programmable gate arrays. By inserting the card into a host machine, intrinsically parallel processing tasks can be exported to the FPGAs. This is similar to the way in which video game rendering tasks can be exported to the GPU on a graphics accelerator. We show how an FPGA is a suitable processing element, in terms of performance per watt, for many computing tasks.

We set out to design and build a reconfigurable card that harnessed the latest FPGAs and fastest available I/O interfaces. The resultant design is one which can run within a host machine, in an array of host machines, or as a stand-alone processing node. The final design had the following specifications:

Form factor HyperTransport Expansion Card Standard Rev1.1

On-board FPGAs Xilinx Virtex-5 LX110T-FF1136 and LX50-FF676

I/O Capabilities 16-lane HTX connector, 2 × 10GBASE-CX4 connectors

On-board memory 6 × Samsung QDRII+

Power Consumption minimum 7W, maximum 50W

We discuss these design choices in light of our reviews of similar commercial systems. We then explain how Mentor Graphics tools were used to produce a complete design specification which was packaged and sent for layout design at Mechatronics Test Equipment. We simulated the resultant layout in software and found it to be problem free. Fabrication of the PCBs took place in California, whilst component assembly was carried out by a local firm. Various gateware test benches were produced for checking the validity of the on-board interfaces such as the 10GBASE-CX4s and the QDRII+ modules, and we carried out probe tests with an oscilloscope. The assembled boards were found to be entirely functional according to their design specification.

### Acknowledgements

I would like to acknowledge a number of people who helped me considerably during the course of my project.

Firstly, to my supervisors:

I thank Professor Mike Inggs for his endless efforts in organising funding, providing resources, and dishing out wisdom and advice to make the project possible. I am grateful for the way this project was made significant to the new ACE research group. Also, Dr Alan Langman donated much of his time to help flesh out the design issues and was also kind enough to put up with my presence at the SKA/KAT office for many months.

To my fellow masters students at the SKA and the CHPC:

Andrew Woods, Peter McMahon, Jason Manley, Jason Salkinder, Nick Thorne, Jane Hewitson, Michael Gorven and Joe Milburn - thanks for all the laughs and good times over the last two years.

To the engineers and administration staff of the SKA/KAT:

Francois Kapp, David George and Alec Rust - thank you for hours of help and advice on PCBs as well as FPGA related issues. Kim de Boer and Annah Mashemola you made the experience of being a SKA/KAT student a very pleasant one.

To Saira Shaikh of MTE:

Thank you for your very professional work and prompt email responses that helped create a successful layout design.

To Xilinx, Inc.

Thank you for the donation of the Virtex-5 FPGAs, without which this project would have been enormously expensive.

To the employees at Tellumat:

Ashwin Kasi and others - thank you for your great work in assembling the PCBs and for sorting through the most complicated mess of components you've probably ever seen.

My two years of living, travel and equipment expenses were funded by my SKA postgraduate bursary, and I am truly grateful for the resources and experiences I was afforded through the SKA - Human Capital Development Programme.

To anyone else I have forgotten to mention here, thank you!

### Contents

| יע           | eciar        | ation                                                      | 1   |

|--------------|--------------|------------------------------------------------------------|-----|

| $\mathbf{A}$ | bstra        | $\operatorname{\mathbf{ct}}$                               | ii  |

| A            | ckno         | vledgements                                                | 111 |

| N            | omer         | clature                                                    | Х   |

| 1            | Intr         | oduction                                                   | 1   |

|              | 1.1          | Objectives                                                 | 1   |

|              | 1.2          | Motivation                                                 | 3   |

|              | 1.3          | Chapter Summaries                                          |     |

| 2            | A E          | ackground to Reconfigurable Computing                      | 9   |

|              | 2.1          | The Rebirth of Parallel Computing                          | 9   |

|              | 2.2          | Encountering Amdahl's Law                                  | 10  |

|              | 2.3          | The Unexploited Field of Reconfigurable Computing          | 11  |

|              | 2.4          | Reconfigurable Co-Processing                               | 12  |

| 3            | ΑΊ           | echnology Review                                           | 15  |

|              | 3.1          | Existing Accelerator Cards                                 | 15  |

|              |              | 3.1.1 Celoxica's RCHTX-XV4                                 | 15  |

|              |              | 3.1.2 University of Mannheim HTX-Board                     | 15  |

|              |              | 3.1.3 Nallatech BenONE-PCIe                                | 17  |

|              |              | 3.1.4 Pico Computing E-16 LX50                             | 18  |

|              | 3.2          | Top-End FPGA Technology                                    | 18  |

|              | 3.3          | Expansion Card Interfaces                                  | 19  |

|              |              | 3.3.1 HTX vs PCI Express                                   | 19  |

|              | 3.4          | On-board Memory Technologies                               | 21  |

|              | 3.5          | Back-end I/O Capabilities                                  | 22  |

|              | 3.6          | Power Supply                                               | 23  |

| 4            | $Th\epsilon$ | Requirements of a General Reconfigurable Co-Processor Card | 24  |

|              | 4.1          | Form Factor                                                | 24  |

|   | 4.2  | Functional Requirements                    |  |

|---|------|--------------------------------------------|--|

|   |      | 4.2.1 Usability in Different Architectures |  |

|   |      | 4.2.2 I/O Capabilities                     |  |

|   |      | 4.2.3 Reconfigurable Component             |  |

|   |      | 4.2.4 Latency                              |  |

|   |      | 4.2.5 On-board Memory                      |  |

|   |      | 4.2.6 Power Consumption                    |  |

|   | 4.3  | Cost Considerations                        |  |

| 5 | Har  | dware Design 28                            |  |

|   | 5.1  | Subsystems                                 |  |

|   |      | 5.1.1 FPGAs                                |  |

|   |      | 5.1.2 FPGA Configuration                   |  |

|   |      | 5.1.3 HyperTransport Interface             |  |

|   |      | 5.1.4 QDRII+ Memory                        |  |

|   |      | 5.1.5 10 Gigabit Ethernet                  |  |

|   |      | 5.1.6 Serial Debug                         |  |

|   |      | 5.1.7 LEDS                                 |  |

|   |      | 5.1.8 Clocking                             |  |

|   | 5.2  | Power Supplies and Voltage References      |  |

|   | 5.3  | Final Design                               |  |

| 6 | Har  | Iware Implementation 38                    |  |

|   | 6.1  | CAD Suite                                  |  |

|   | 6.2  | FPGA pin management using I/O Designer     |  |

|   | 6.3  | Manual symbol creation using DxDesigner    |  |

|   | 6.4  | Modular design in DxDesigner               |  |

|   | 6.5  | Voltage Integrity                          |  |

|   | 6.6  | Outsourced Layout                          |  |

|   | 6.7  | Signal Integrity Tests                     |  |

|   | 6.8  | Bill of Materials                          |  |

|   | 6.9  | Fabrication                                |  |

|   | 6.10 | Assembly                                   |  |

| 7 | Gat  | eware and Interface Tests 54               |  |

|   | 7.1  | Test Bench Setup                           |  |

|   | 7.2  | Gateware                                   |  |

|   |      | 7.2.1 Configuration, LED and Clock Test    |  |

|   |      | 7.2.2 Serial UART Interface Test           |  |

|   |      | 7.2.3 FPGA-to-FPGA HT-Link                 |  |

|   |      | 7.2.4 QDRII+ Interface                     |  |

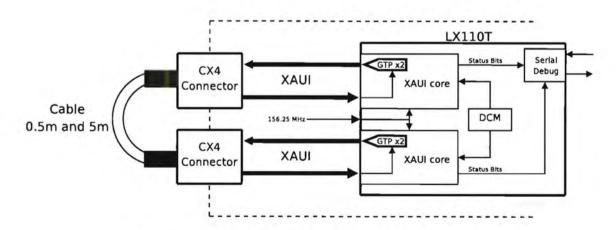

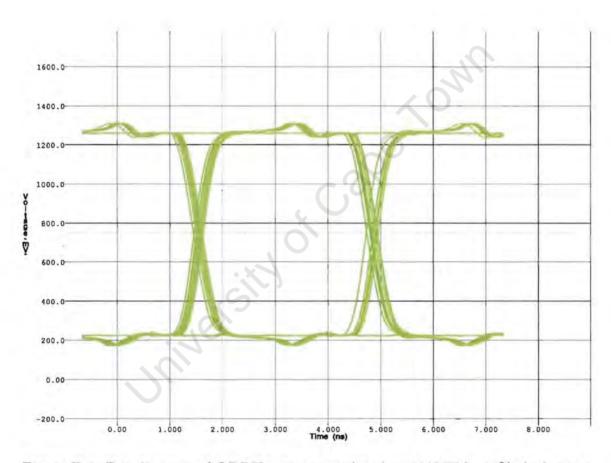

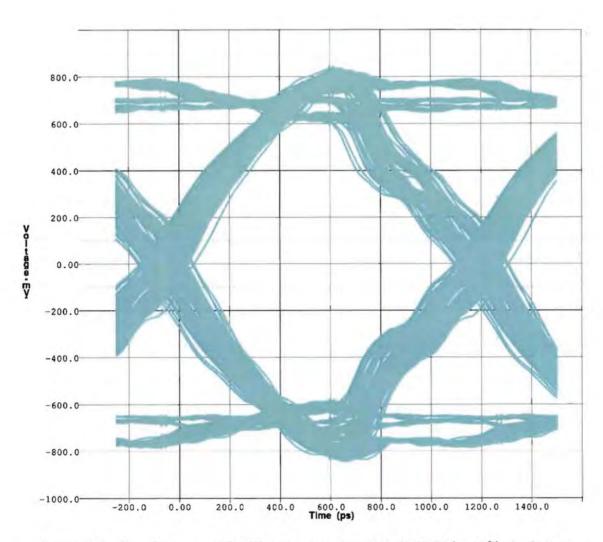

|   |      | 7.2.5 CX4 Interface Test                   |  |

|    |       | 7.2.6 HyperTransport                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | pr |

|----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|    | 7.3   | Test Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 60 |

| 8  | Fut   | ure Work and Recommendations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 62 |

|    | 8.1   | Further Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 62 |

|    |       | 8.1.1 Gateware Library                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 62 |

|    |       | 8.1.2 Drivers and API Tool Set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

|    |       | 8.1.3 Reconfigurable Accelerator Card Revision 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 63 |

|    | 8.2   | Recommended Project Extensions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 63 |

| A  | Des   | ign Files                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 64 |

| В  | Det   | ailed HyperLynx Simulations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 65 |

| Bi | bliog | graphy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 68 |

|    |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|    |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|    |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|    |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|    |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|    |       | O)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

|    |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|    |       | .5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

|    |       | (0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |

|    |       | University of the second of th |    |

|    |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|    |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|    |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|    |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

### List of Figures

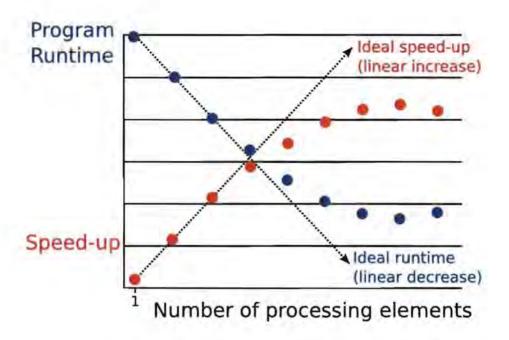

| 2.1 | Demonstration of Amdahl's Law                                        | 11 |

|-----|----------------------------------------------------------------------|----|

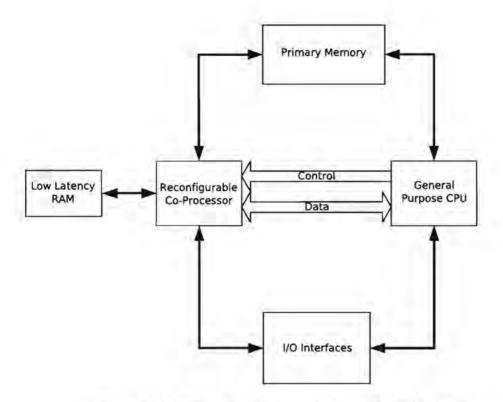

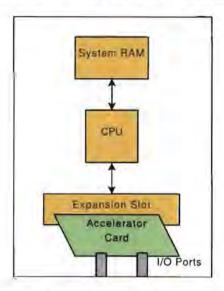

| 2.2 | A functional view of a reconfigurable co-processor                   |    |

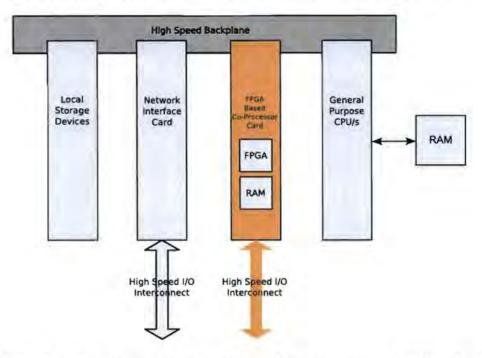

| 2.3 | A practical view of a reconfigurable co-processor interfaced with an |    |

|     | existing Von Neumann node                                            | 14 |

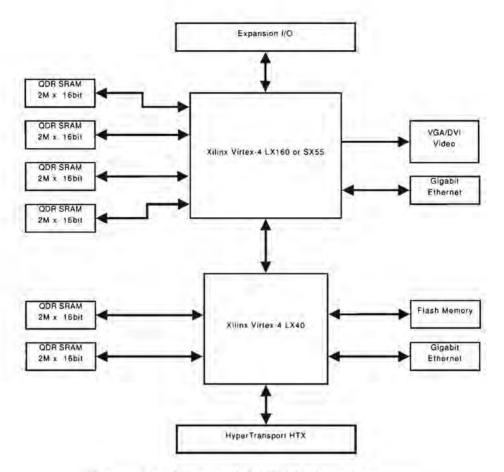

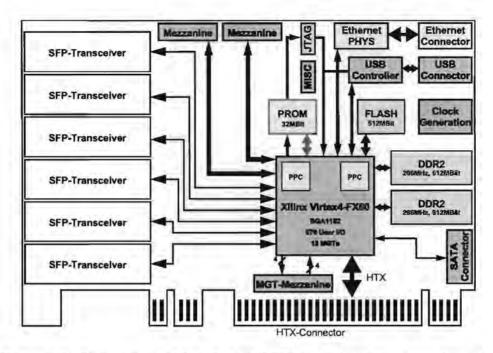

| 3.1 | Celoxica RCHTX-XV4 architecture                                      | 16 |

| 3.2 | University of Mannheim's HTX-Board architecture, from [1]            | 17 |

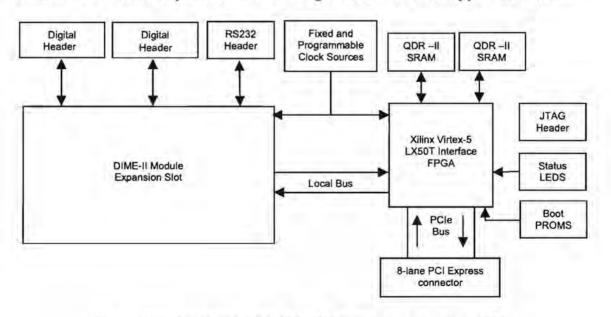

| 3,3 | Nallatech BenONE-PCIe architecture, from [17]                        | 17 |

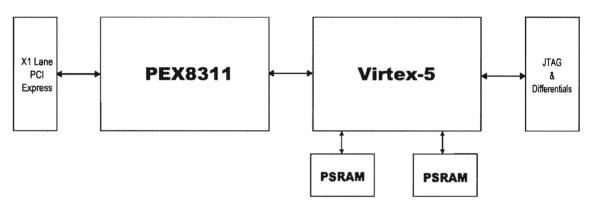

| 3.4 | Pico Computing E16 architecture, from [18]                           | 18 |

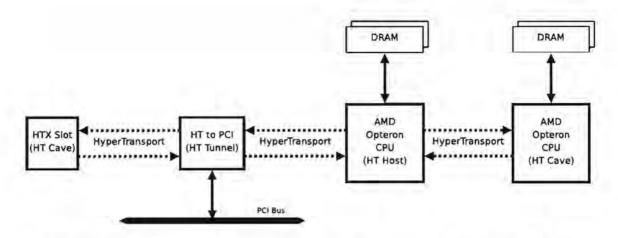

| 3.5 | A Simple HyperTransport Chain with multiple CPUs and an HTX          |    |

|     | expansion slot                                                       | 20 |

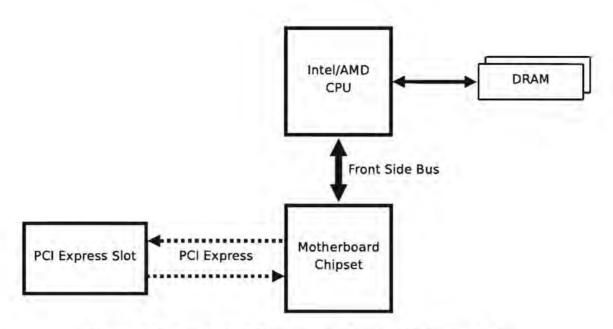

| 3.6 | Simple PCI Express interface to the front side bus                   | 21 |

| 4.1 | Use case 1 - Single host machine                                     | 25 |

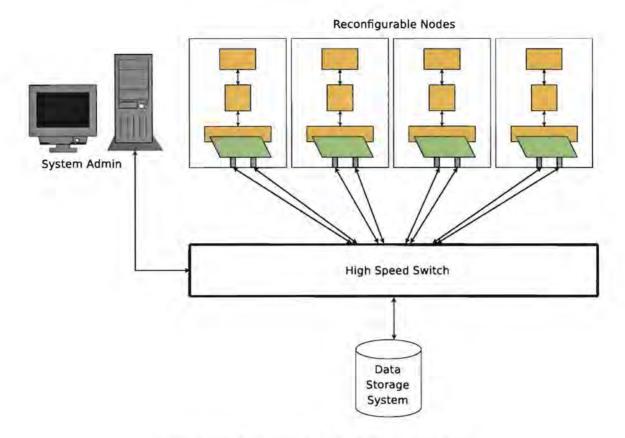

| 4.2 | Use case 2 - Cluster configuration                                   | 26 |

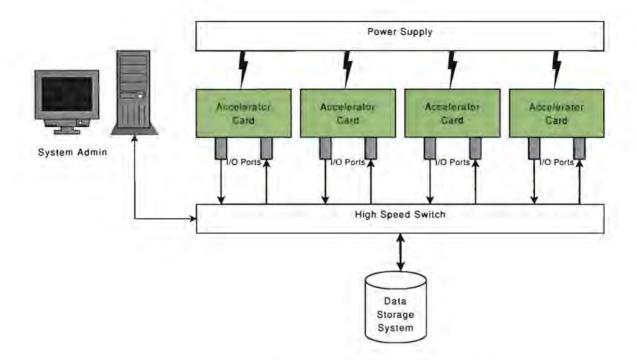

| 4.3 | Use case 3 - Cluster configuration (stand-alone)                     | 27 |

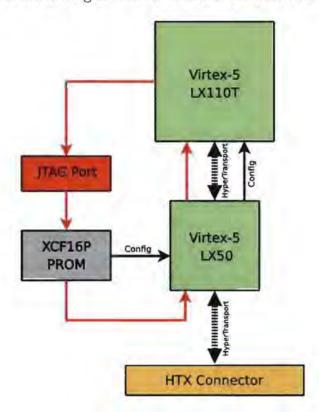

| 5.1 | The multi-FPGA setup with HyperTransport links and configuration     |    |

|     | options                                                              | 29 |

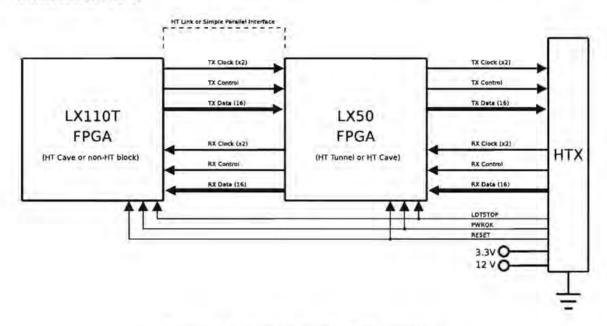

| 5.2 | The on-board HTX interface                                           | 30 |

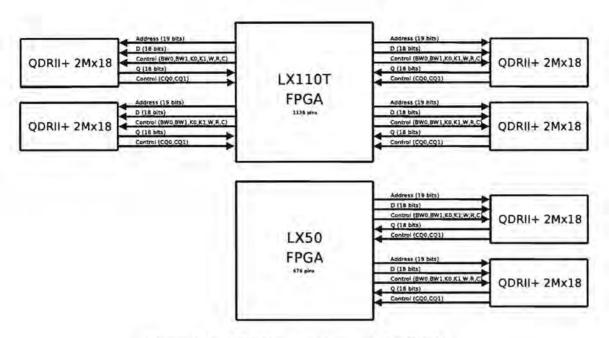

| 5.3 | QDRII+ interfaces to the FPGAs                                       | 32 |

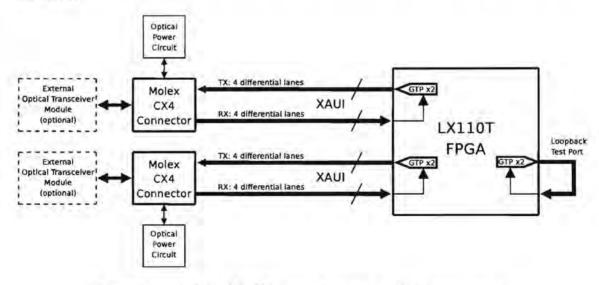

| 5.4 | 10GBASE-CX4 interface to the CX4 connectors                          | 32 |

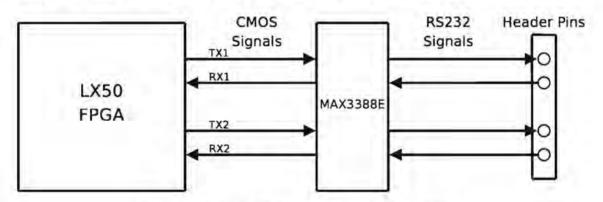

| 5.5 | Serial RS232 interface to the LX50                                   | 33 |

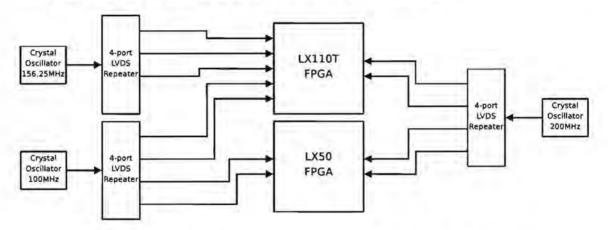

| 5.6 | On-board clock generation using crystal oscillators                  | 34 |

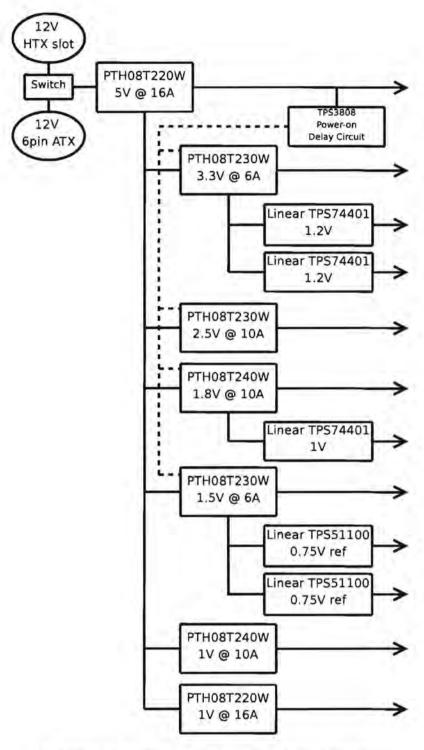

| 5.7 | Power and reference voltage network                                  | 36 |

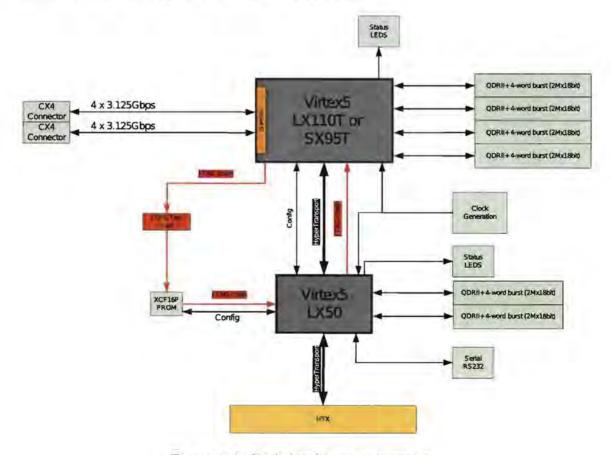

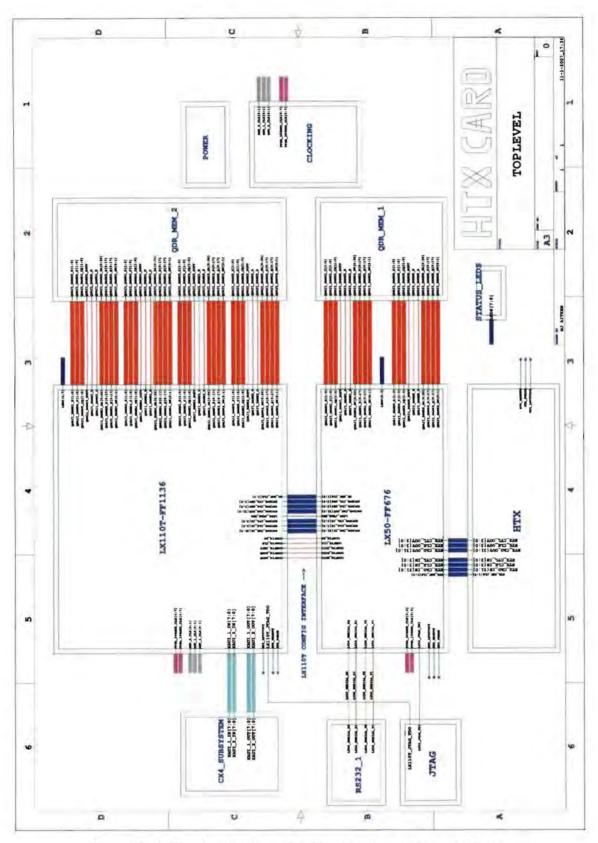

| 5.8 | High level system overview                                           | 37 |

| 6.1 | Pin-out diagram of the LX50 Virtex-5 FPGA, from [26]                 | 39 |

| 6.2 | Pin-out diagram of the LX110T Virtex-5 FPGA, from [26]               | 40 |

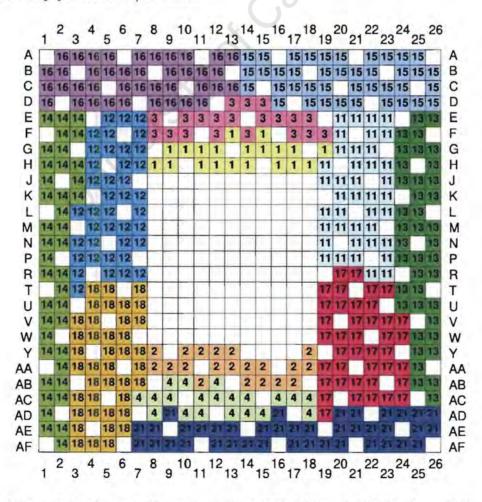

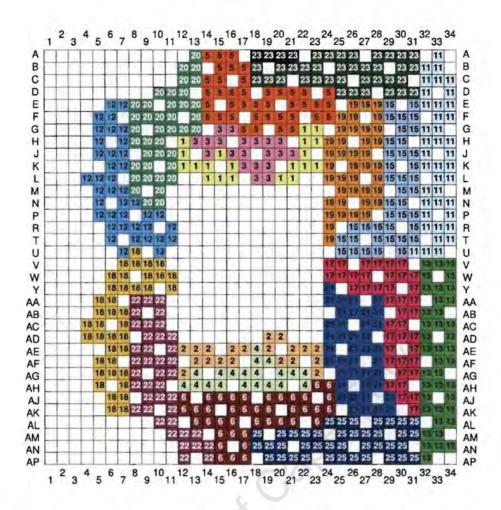

| 6.3 | Top level schematic file showing system modules                      | 42 |

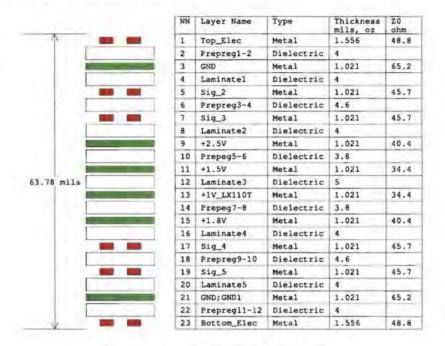

| 6.4 | Diagram of stack-up                                                  |    |

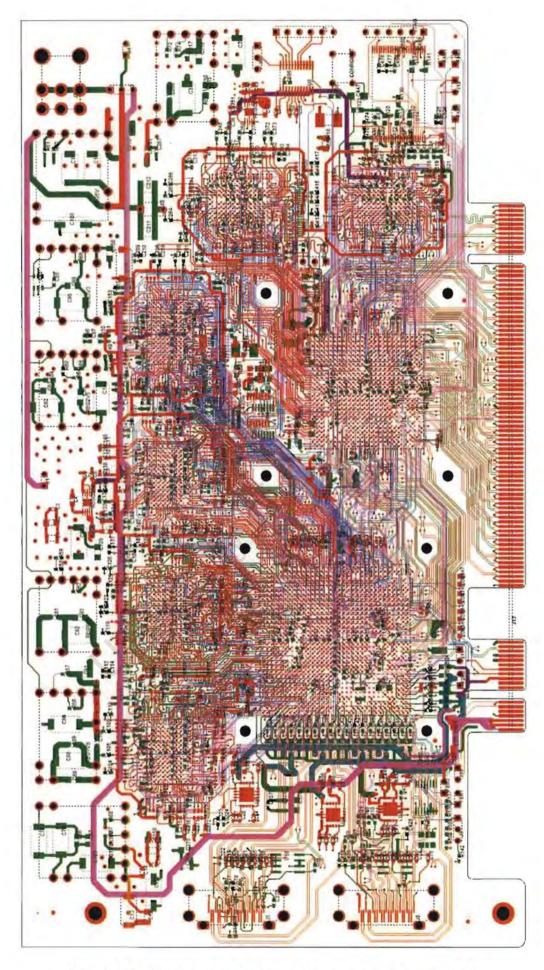

| 6.5 | Final layout design - showing signal layers only                     | 46 |

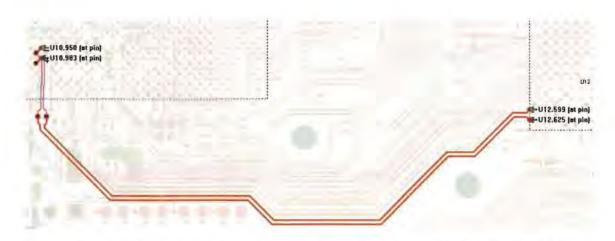

| 6.6 | Differential traces HTCAVE_CAD_IN00, HTCAVE_CAD_IN01 shows           | n  |

|     | in the pin selection screen                                          | 48 |

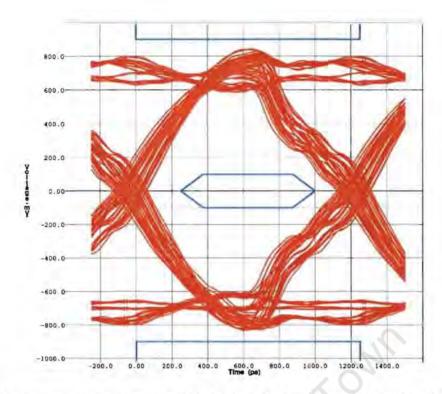

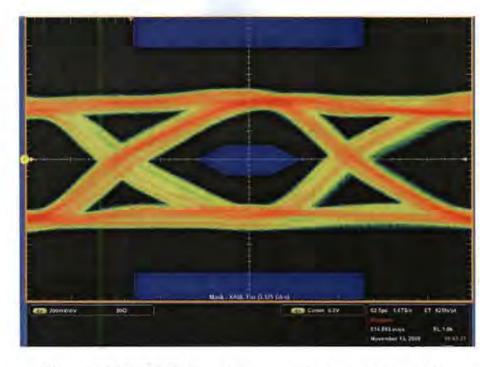

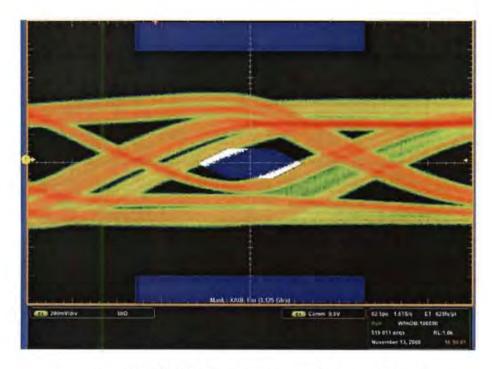

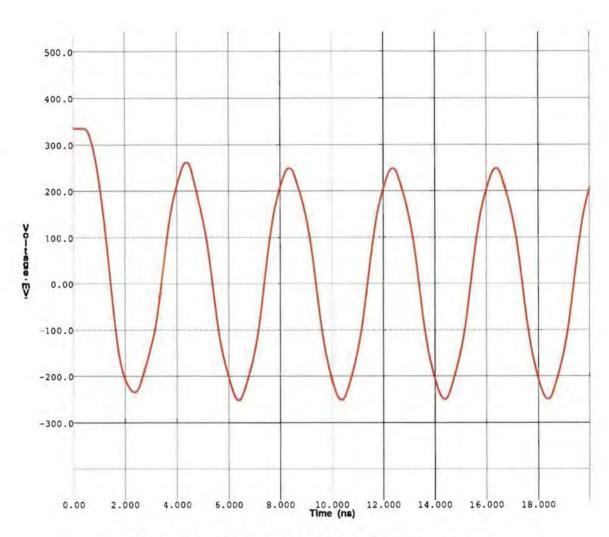

| 6.7 | Eye-diagram of traces HTCAVE_CAD_IN00, HTCAVE_CAD_IN01 simulated at 800MHz using detailed simulation in the digital oscillo-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | scope with 15% clock jitter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 49 |

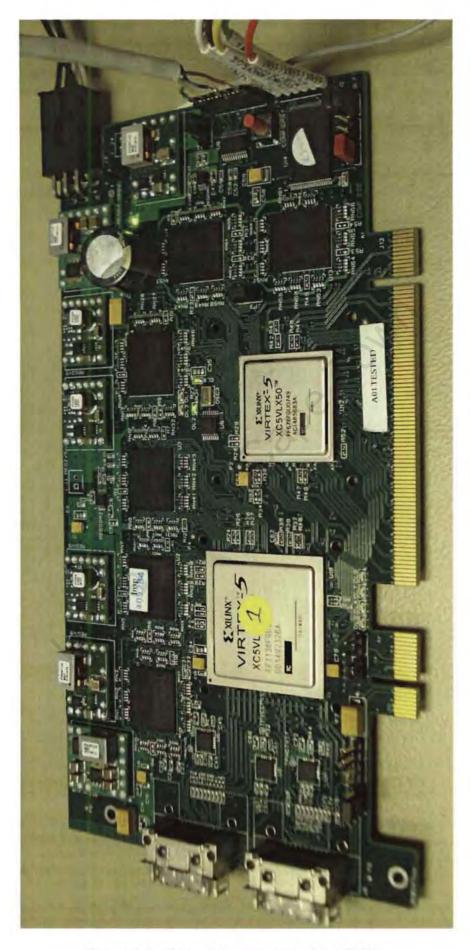

| 6.8 | One of the two assembled PCBs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 53 |

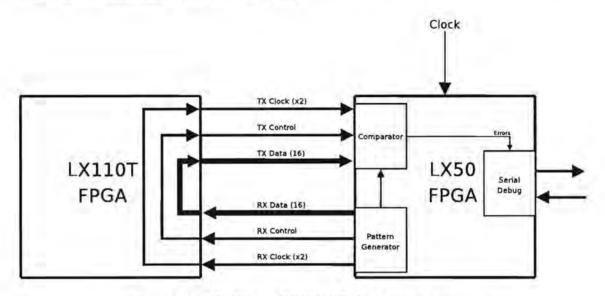

| 7.1 | FPGA-to-FPGA HT-link test gateware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 57 |

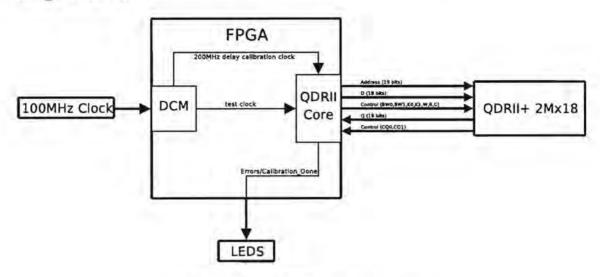

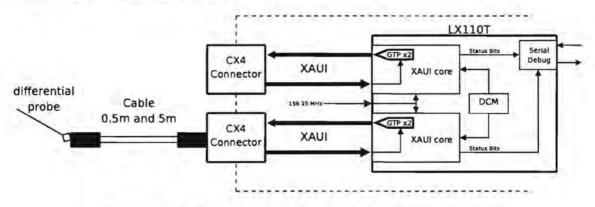

| 7.2 | QDRII test gateware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 58 |