The copyright of this thesis vests in the author. No quotation from it or information derived from it is to be published without full acknowledgement of the source. The thesis is to be used for private study or non-commercial research purposes only.

Published by the University of Cape Town (UCT) in terms of the non-exclusive license granted to UCT by the author.

# Design of a Scheduling Mechanism for an ATM Switch

Nicholas Oliver Harvey

# Design of a Scheduling Mechanism for an ATM Switch

## **Abstract**

Transfer Mode (ATM), a packet switching architecture. One of the promises of ATM is the provision of guaranteed Quality of Service (QoS). A major factor in the provision of QoS in ATM switches is the capability of a scheduling mechanism to control access to the switching fabric. Historically the use of queuing and scheduling at the switch fabric outputs has been the favoured approach used in the design of ATM switches. However, input queued switch architectures have recently been receiving considerable interest in the research community. Input queued switch architectures for various reasons have become an attractive solution for the design of high performance packet switches. In particular input queued switches scale better to larger sizes. They are also cheaper to construct in terms of the speed of the switch fabric and the memory size and bandwidth required. However, there are still considerable problems associated with the implementation of input queued scheduling algorithms.

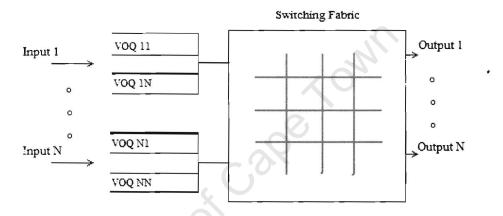

The dissertation to follow is devoted to design and related theory of a centralized scheduling algorithm to maximize the throughput and provide fair bandwidth allocation in an input queued ATM switch. In particular, the use of Virtual Output Queueing (VOQ) at the input ports to avoid head of line blocking is considered. The problem faced by an input queued scheduling algorithm utilizing VOQ is formalized as finding the maximum weighted matching on a bipartite graph in which nodes represent input and output ports and edges represent cells to be switched.

In this dissertation, the candidate proposes the use of a ratio to multiply the weights used in the matching algorithm to control the delay that individual connections encounter. We demonstrate the improved characteristics of a switch using a ratio presenting results from simulations.

The candidate also proposes a novel scheduling mechanism for an input queued ATM switch. In order to evaluate the performance of the scheduling mechanism in terms of throughput and fairness, the use of various metrics, initially proposed in the literature to evaluate output buffered switches are evaluated, adjusted and applied to input scheduling. In particular the Worst-case Fairness Index (WFI) which measures the maximum delay a connection will encounter is derived for use in input queued switches

The evaluation of the scheduling algorithm is conducted with the use of a specifically developed software cell based simulator. The simulator is designed to evaluate the performance of input scheduling algorithms under various traffic conditions and different switch configurations. In particular the use of algorithms which accurately mimic real network traffic allows the evaluation of the scheduling mechanism under realistic conditions. By using the simulator to compare the performance of the proposed scheduling algorithm with those in the literature, the candidate will demonstrate the scheduler's advantages. The dissertation is concluded with a study of the practical considerations of implementing the scheduler in hardware, and with some thoughts on simulating scheduling algorithms. Some ideas for further research are also proposed.

Julia of Carle

# **Table of Contents**

| List of Figures                                                            | vii |

|----------------------------------------------------------------------------|-----|

| List of Tables                                                             | ix  |

| Chapter 1 : Introduction                                                   |     |

| 1.1 Quality of Service in Packet Switched Networks                         |     |

| 1.1.1 QoS and the Converged Network                                        |     |

| 1.1.2 QoS Parameters                                                       |     |

| 1.2 A Quality of Service Framework                                         |     |

| 1.3 Packet Switching                                                       |     |

| 1.4 Scheduling in a Packet Switch                                          |     |

| 1.5 The Evaluation of Scheduling Mechanisms                                |     |

| 1.6 The Simulation of Scheduling Algorithms                                |     |

| 1.7 Conclusion                                                             | 10  |

|                                                                            | 4.5 |

| <b>Chapter 2 : Overview of ATM switch Architectures</b>                    |     |

| 2.1 Overview of ATM switch Architectures                                   | 12  |

| 2.2 Single stage ATM Switches                                              | 13  |

| 2.2.1 Shared memory switches                                               | 13  |

| 2.2.2 Shared medium (Bus)                                                  |     |

| 2.2.3 Rings                                                                | 16  |

|                                                                            |     |

| 2.3.1 Performance of Multistage Switches                                   |     |

| 2.4 Queuing in ATM Switches                                                | 19  |

| 2.4.2 Input Queuing                                                        |     |

| 2.4.3 Combined Input and Output Queuing                                    |     |

| 2.5 Buffer Management                                                      |     |

| 2.6 Summary                                                                |     |

| 2.0 5421111111                                                             |     |

| Chapter 3: Scheduling in Output Buffered Switches                          | 23  |

| 3.1 Introduction                                                           |     |

| 3.2 Output Scheduling Algorithms                                           |     |

| 3.3 Generalized Processor Sharing                                          |     |

|                                                                            |     |

| 3.4 Fairness in Output Buffered Switches  3.4.1 The Service Fairness Index |     |

| 3.4.2 The Worst-case Fairness Index.                                       |     |

| 3.5 Practical Output Scheduling Algorithms                                 |     |

| 3.5.1 Weighted Round Robin Scheduling                                      |     |

| 3.5.2 Packet-by-packet Generalised Processor sharing Policy (PGPS)         |     |

| 3.5.3 Self-Clocked Fair Queueing Scheduling (SCFQ)                         |     |

| 3.5.4 Start Time Fair Queuing Policy (SFQ)                        |      |

|-------------------------------------------------------------------|------|

| 3.5.5 Discrete Rate Schedulers                                    |      |

| 3.5.6 Worst Case Fair Weighted Fair Queuing (WF2Q)                |      |

| 3.6 Other Work                                                    |      |

|                                                                   |      |

| 3.7 Summary                                                       | 34   |

| Chapter 4 : Scheduling in Input Buffered ATM Switch               |      |

| 4.1 Traffic Scheduling in Input Buffered Switches                 | 35   |

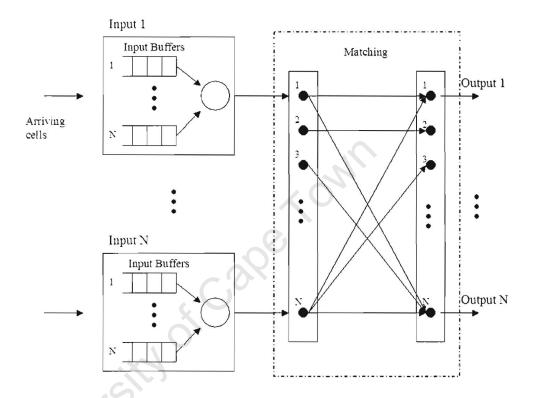

| 4.2 Virtual Output Queuing                                        | 37   |

| 4.3 The Matching Problem                                          | 38   |

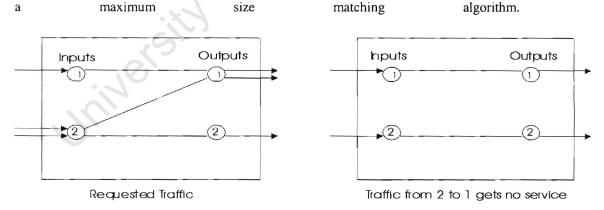

| 4.4 Maximum Size Matching (MSM)                                   |      |

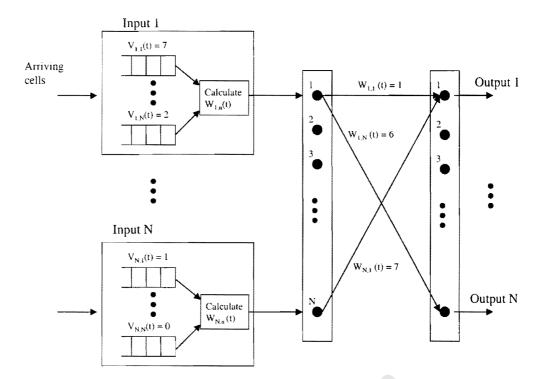

| 4.5 Maximum Weighted Matching (MWM)                               |      |

| 4.6 Iterative Scheduling Algorithms                               |      |

| 4.6.1 Parallel Iterative Matching                                 |      |

| 4.6.2 Weighted Probabilistic Iterative Matching                   |      |

| 4.6.3 Iterative Round Robin Matching with Slip                    |      |

| 4.6.4 Iterative Fair Scheduling                                   |      |

| 4.7 Other Work                                                    | 46   |

| 4.8 Evaluation of scheduling algorithms for input buffered switch | es47 |

| 4.8.1 Latency                                                     |      |

| 4.8.2 Worst-case Fairness                                         | 49   |

| 4.8.3 Service Fairness Index                                      | 51   |

| 4.9 Traffic Models                                                | 53   |

| 4.10 Implementation of Input Scheduling Algorithms                | 53   |

| 4.11 Summary                                                      |      |

| X O                                                               |      |

| Chapter 5: Worst-case Iterative Matching                          | 55   |

| 5.1 Iterative Scheduling Algorithms                               |      |

| 5.2 Using a Ratio to Control the Delay                            |      |

| 5.3 Worst-case Iterative Matching                                 | 57   |

| 5.4 Parallel Implementation of Worst-case Iterative Matching      |      |

| -                                                                 |      |

| 5.5 Summary                                                       | 01   |

| Chantan 6 . Evaluation Warst Casa Itanativa Matahine              | ~ 62 |

| Chapter 6: Evaluation Worst Case Iterative Matching               |      |

| 6.1 Evaluation of Scheduling Algorithms                           |      |

| 6.2 Performance under Bernoulli Traffic                           |      |

| 6.2.1 Latency                                                     |      |

| 6.2.2 Worst-case Fairness                                         |      |

| 6.3 Performance under non-uniform traffic                         |      |

|                                                                   |      |

| 6.3.1 Latency                                                     |      |

| 6.3.3 Worst-case Fairness under bursty traffic                    |      |

| 6.4 Switch Size                                                   |      |

| 6.4.1 Latency                                                     |      |

| 6.5 Summary                                                       |      |

|                                                                   |      |

| Chapter 7: Summary and Future Research                | 80    |

|-------------------------------------------------------|-------|

| 7.1 Summary                                           |       |

| 7.2 Providing QoS support in an Input Buffered Switch |       |

| 7.3 Worst-case Performance                            | 81    |

| 7.4 Simulation Study of Input Scheduling Algorithms   | 81    |

| 7.5 Future Work                                       |       |

| References                                            | 83    |

| Appendix A: A Quality of Service Framework            | 88    |

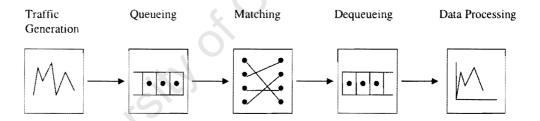

| Appendix B: Design of an ATM Scheduler Simulator      | or 92 |

University of Care

# **List of Figures**

| Figure 2.1 Bus Based Switch                                                              | 14         |

|------------------------------------------------------------------------------------------|------------|

| Figure 2.2 Ring Based Switch                                                             | 15         |

| Figure 2.3 A Multistage Switch                                                           |            |

| Figure 2.4 Input and Output Queueing                                                     | 19         |

| Figure 2.5 Buffer Allocation in an ATM switch                                            |            |

| Figure 3.1 Scheduling in an Output Buffered ATM Switch                                   | 24         |

| Figure 4.1 Virtual Output Queueing                                                       |            |

| Figure 4.2 The Matching Problem                                                          |            |

| Figure 4.3 Service denial using a Maximum Size Matching Algorithm                        |            |

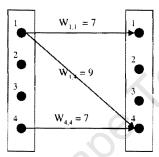

| Figure 4.4 Example of Weights for Maximum Weighted Matching Algorithm                    |            |

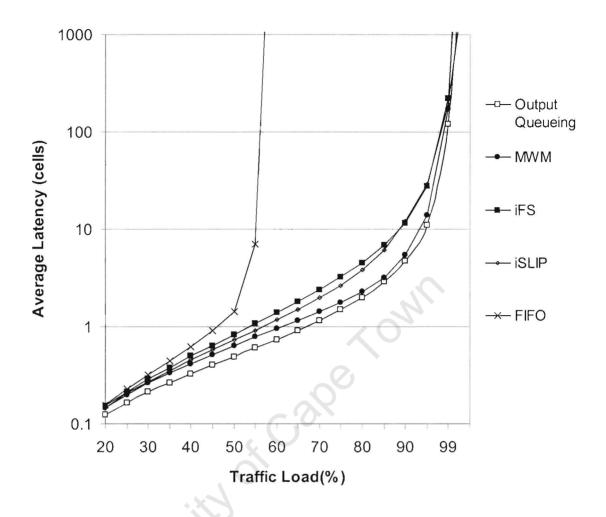

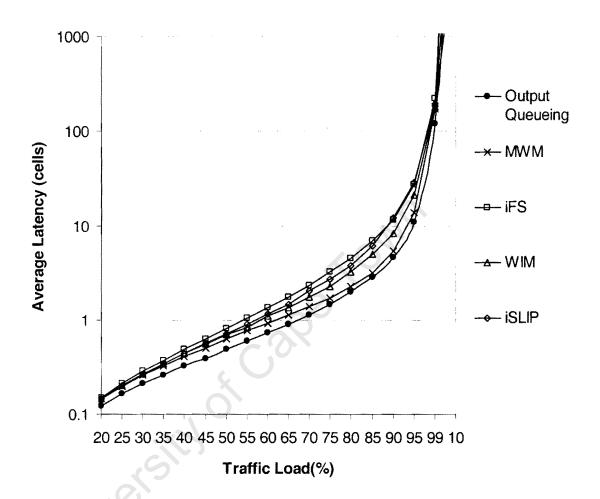

| Figure 4.5 Latency characteristics of MWM, iSLIP, iFS and Output Queueing for            |            |

| Bernoulli arrival processes and destinations uniformly distributed across the output     |            |

| ports. The switch size used is 16x16. The graph shows the average delay in cell units.   | 49         |

| Figure 5.1 Finding a maximum match, selecting at the output ports                        |            |

| Figure 5.2 Finding a maximum match, selecting at the input ports                         |            |

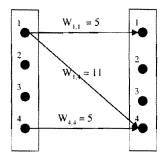

| Figure 5.3 Parallel implementation of WIM                                                |            |

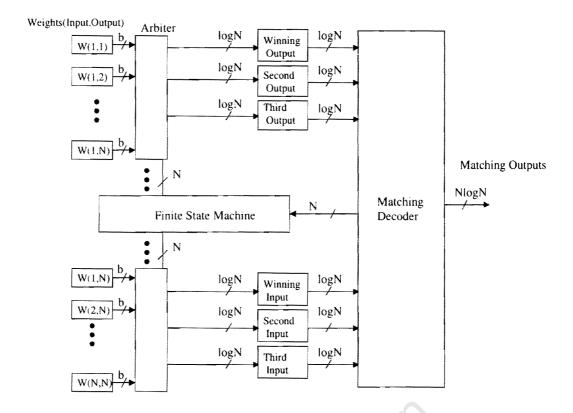

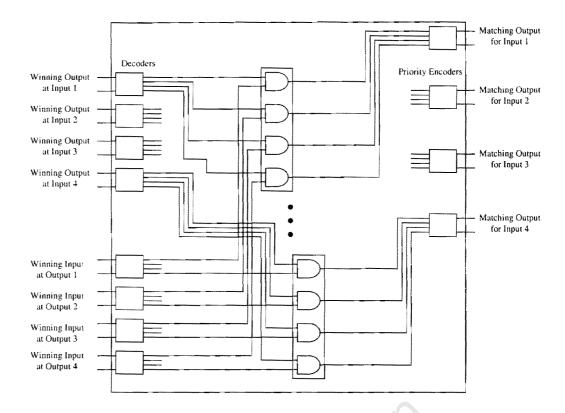

| Figure 5.4 An input matching decoder used in a parallel implementation of WIM for a 4x4  |            |

| switch                                                                                   | 61         |

| Figure 6.1 Latency characteristics for MWM, iSLIP, WIM, iFS and Output Queueing for      |            |

| Bernoulli arrival processes and destinations uniformly distributed across the output     |            |

| ports. The switch size used is 16x16. The graph shows the average delay in cell units.   | 65         |

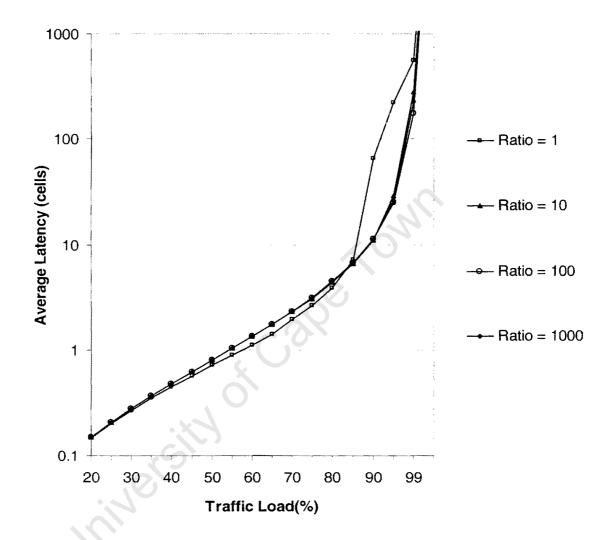

| Figure 6.2 Latency performances for WIM scheduling algorithm using different ratio       |            |

| values Arrival processes are Bernoulli and destinations uniformly distributed across     |            |

| the output ports. The switch size used is 16x16. The graph shows the average delay in    |            |

| cell units                                                                               | 66         |

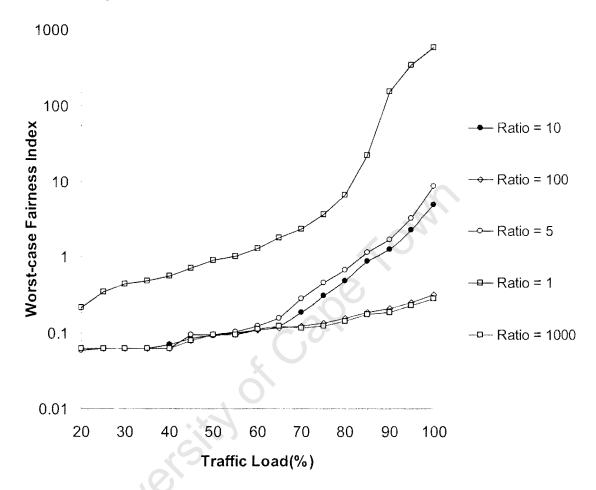

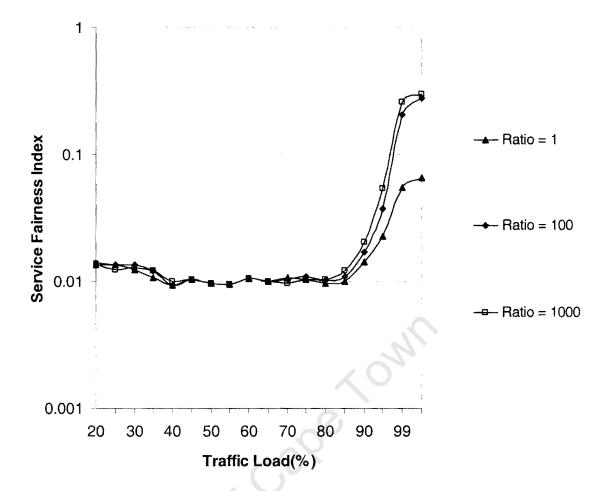

| Figure 6.3 Worst-case Fairness Index for WIM scheduling algorithm using different ratio  |            |

| values Arrival processes are Bernoulli and destinations uniformly distributed across     |            |

| the output ports. The switch size used is 16x16. The graph gives an indication of the    |            |

| maximum delay a cell might experience.                                                   | 67         |

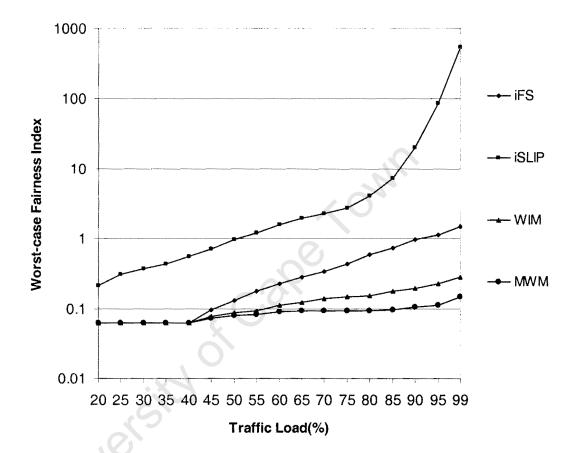

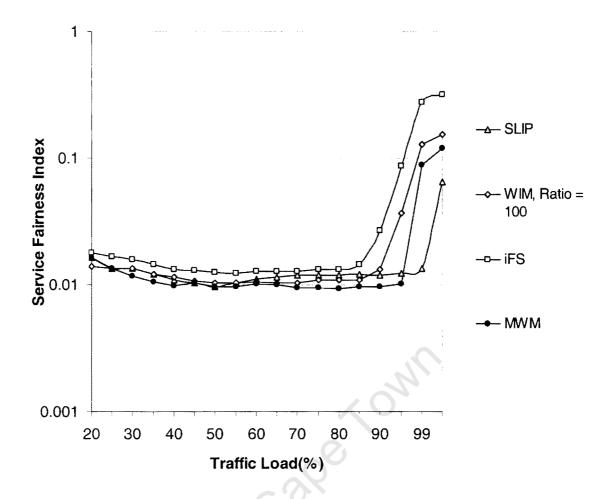

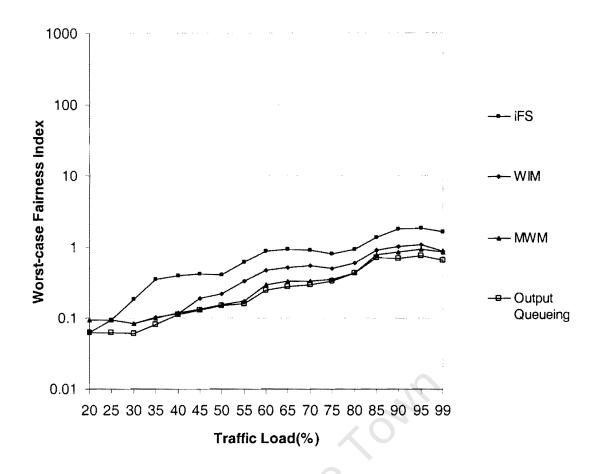

| Figure 6.4 Worst-case Fairness Index for the WIM, iSLIP, iFS and MWM scheduling          |            |

| algorithms Arrival processes are Bernoulli and destinations uniformly distributed        |            |

| across the output ports. The switch size used is 16x16. The graph gives an indication    |            |

| of the maximum delay a cell might experience.                                            | 68         |

| Figure 6.5 Service Fairness Index for the WIM scheduling algorithm using different ratio |            |

| values. Arrival processes are Bernoulli and destinations uniformly distributed across    |            |

| the output ports. The switch size used is 16x16. The graph gives an indication of the    |            |

| how fairly the bandwidth is distributed under different traffic loads                    | 69         |

| Figure 6.6 Service Fairness Index for the WIM, SLIP, iFS and MWM scheduling              |            |

| algorithms. Arrival processes are Bernoulli and destinations uniformly distributed       |            |

| across the output ports. The switch size used is 16x16. The graph gives an indication    |            |

| of the how fairly the bandwidth is distributed                                           | 70         |

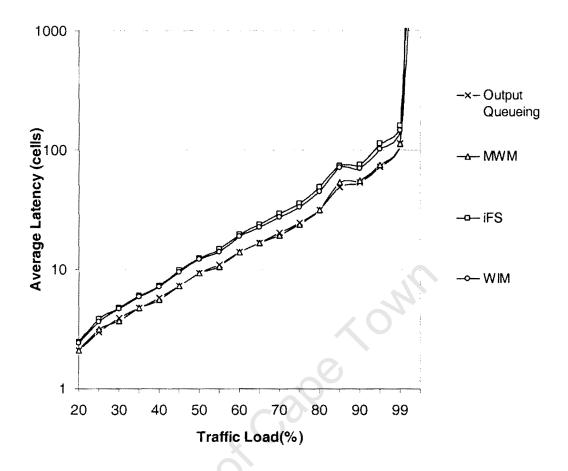

| Figure 6.7 Latency performances for MWM, WIM, iFS and Output Queueing for Bursty         |            |

| arrival processes and destinations uniformly distributed across the output ports. The    | <b>-</b> - |

| switch size used is 16x16. The graph shows the average delay in cell units               | /1         |

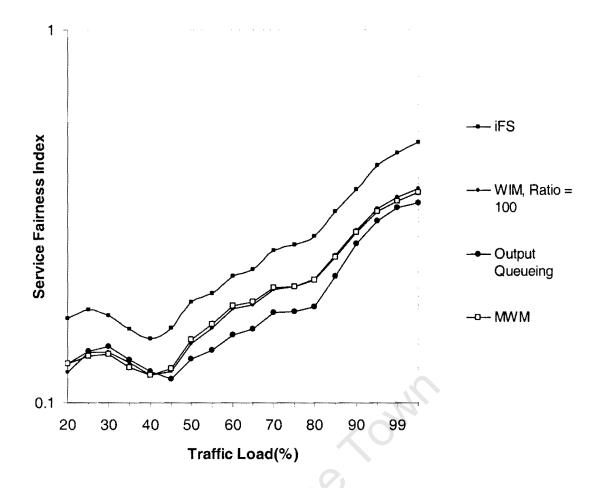

| Figure 6.8 Service Fairness Index for WIM, iFS, Output Queueing and MWM. Arrival         |            |

| processes are Bursty and destinations uniformly distributed across the output ports.     |            |

| The switch size used is 16x16. The graph gives an indication of the how fairly the       |     |

|------------------------------------------------------------------------------------------|-----|

| bandwidth is distributed between connections                                             | .72 |

| Figure 6.9 Service Fairness Index for the iFS, WIM, MWM and Output Queueing              |     |

| scheduling algorithms. Arrival processes are bursty and destinations uniformly           |     |

| distributed across the output ports. The switch size used is 16x16                       | .73 |

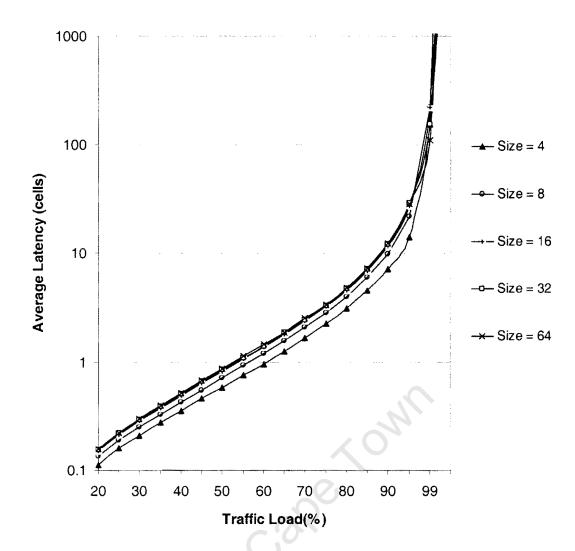

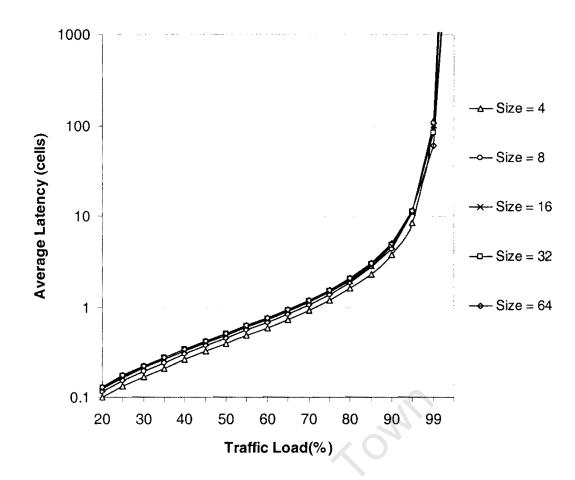

| Figure 6.10 Latency characteristics of the WIM scheduling algorithm, for different size  |     |

| switches. Arrival processes are Bernoulli and destinations are uniformly distributed     |     |

| across the output ports. The graph shows the average delay in cell units                 | .75 |

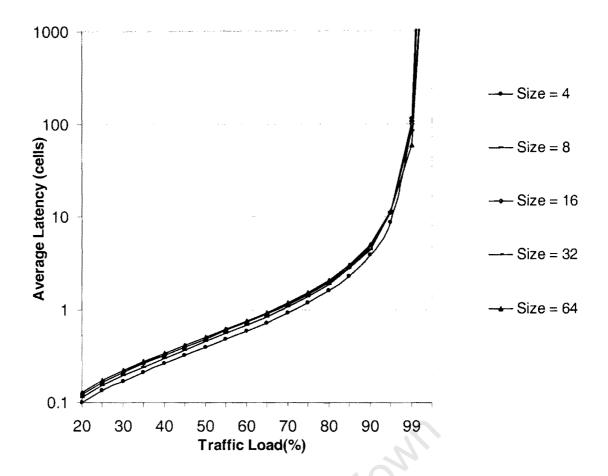

| Figure 6.11 Latency characteristics of the iFS scheduling algorithm, for different size  |     |

| switches. Arrival processes are Bernoulli and destinations are uniformly distributed     |     |

| across the output ports. The graph shows the average delay in cell units                 | .76 |

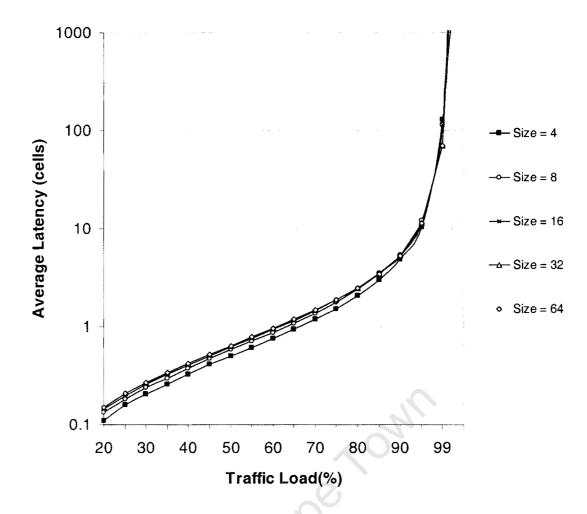

| Figure 6.12 Latency characteristics of Maximum Weighted Matching scheduling              |     |

| algorithm, for different size switches. Arrival processes Bernoulli and destinations are | :   |

| uniformly distributed across the output ports. The graph shows the average delay in      |     |

| cell units                                                                               | .77 |

| Figure 6.13 Latency characteristics of Output Queueing, for different size switches.     |     |

| Arrival processes are Bernoulli and destinations are uniformly distributed across the    |     |

| output ports. The graph shows the average delay in cell units                            | .78 |

|                                                                                          |     |

Unit Versity of Cape

# **List of Tables**

Table 1. – QoS Technologies ......4

Unity ereity of Caipe Lown

# **Chapter 1: Introduction**

### 1.1 Quality of Service in Packet Switched Networks

Rapid advances in computer and telecommunications network technologies have meant that in the near future we will experience as part of every day life, applications and services that a decade or two ago were in the realms of science fiction. Examples of these applications are videophones, video on demand and multi person virtual reality.

Traditionally there was one network for each type of traffic, for example a business enterprise may have had a private Time Division Multiplex (TDM) based voice network, an Internet Protocol (IP) network to the Internet, and an ISDN video conferencing network as well as a multi-protocol based Local Area Network (LAN). However today network traffic is becoming more varied and in the future there will be requirements to support an even more diverse set of applications. It is evident that it would be ideal to support all of these applications on one network.

When the different applications had separate dedicated networks, controlling the levels of service provided was less of a problem as all the traffic in each network was similar and the networks could be engineered and fine tuned to provide the required service levels. When different types of traffic, each with different requirements are transported over a single network, the different traffic types often react unfavourably together. For example a voice application expects to experience no packet loss and a minimum but fixed amount of packet delay. The voice application receives this service level when it operates over a TDM network. A best effort IP network has varying amounts of packet loss and variable delay. The result is that the voice application runs very badly on the IP network, however the alternative of using circuit switching to transmit data, results in ineffective use of the resources of the network.

#### 1.1.1 QoS and the Converged Network

What is required in a multi-service network is a means of preventing different applications from affecting the performance of one another. The term for this concept is "Quality of Service" (QoS). A best effort IP network effectively provides no QoS. Other networks

technologies such as Asynchronous Transfer Mode (ATM) have been engineered to provide QoS.

From the network user's point of view, QoS is a term used to describe the complete experience an application will receive from a network. A more network centric definition would be that QoS refers to the classification of packets for the purpose of treating certain classes or flows of packets in a particular way compared to other packets.

The aim of this chapter is to provide an introduction to QoS and to show why it is necessary and how it is incorporated in the modern network and what mechanisms are required to provide this.

Today most networks are converging to an IP based transport layer. Data applications are already all IP-based, while traditionally Time Division Multiplexing (TDM) based voice networks are also transitioning to being IP-based. Video conferencing is also moving towards IP however at a slower pace.

Traditionally IP has been routed over ATM using IP over ATM virtual circuits or multi protocol over ATM (MPOA). These forwarding methods have proven to be complicated and cumbersome. However packet switched IP does have numerous advantages over traditional IP routers, the most important of which is the ability to provide QoS. Along with this move to IP transport networks, the Multi Protocol Label Switching (MPLS) protocol is being widely deployed in the core network as a means to bring the speed advantages of packet switching to the IP realm. Multi protocol Label switching allows IP flows to be routed through a packet switched network and so allows IP to acquire some of the QoS mechanisms of ATM and packet switched networks. The intention of this chapter is not to give an introduction to MPLS or any particular technology, but merely to show how each technology provides QoS.

#### 1.1.2 QoS Parameters

How is QoS quantified? A number of QoS parameters can be measured and monitored to determine whether a service level offered or received is being achieved. Not all are equally important to every application. Perhaps the most basic is network availability. Network availability can have a significant affect on QoS. Network availability is the sum of the availability of many items that are used to create a network, such as fibre, network interface cards, power sources etc. Network operators can determine their networks

availability by among other things the amount of redundancy they incorporate into their network.

When the term QoS is discussed with regard to packet switched networks what comes to mind is most commonly associated with a guaranteed bandwidth. When more than one user shares the use of a network they compete for the available bandwidth. They get more or less bandwidth depending on various factors. If QoS is to be implemented in a network some mechanism is required to divide up the bandwidth and share it fairly among users. Since the point of congestion in most modern computer networks is the switch or router, dividing up the bandwidth amounts to implementing a scheduling mechanism which allocates access to the switch fabric. This topic is the focal point of this text.

Network delay is the transmit time a user experiences from the ingress point to the egress point of the network. Delay can cause significant QoS issues with applications such as voice and video. The delay can be fixed, for example due to propagation delay, or it can be variable, for example due to contention in switches.

Jitter is the measure of delay variation between consecutive packets for a given traffic flow. Jitter has a pronounced effect on real time delay sensitive applications such as voice and video. Losses can occur due to various reasons. Two of the main causes of packets loss are errors introduced by the physical transmission medium and congested network nodes. Because congestion has a direct impact on packet loss, congestion avoidance mechanisms are often deployed. In the ideal converged network, those connections which are within their allowed traffic agreement will not experience any of the congestion.

## 1.2 A Quality of Service Framework

Providing QoS in a network has become an active area of work in the last few years, and many approaches have been investigated. Generally implementing QoS in a network requires a number of technologies to work together. These QoS technologies operate at different layers in the protocol stack and provide different services. Some of these are listed in Table 1. The purpose of this section is not to delve in depth into these technologies but to provide an understanding of how they are used to support QoS.

Table 1. - QoS Technologies

QoS Aware Application **RSVP** IP QoS IP Differentiated Services Network-Signalled QoS ATM PNNI, MPLS RSVP-TE or MPLS CR-LDP **QoS Monitoring** Traffic Engineered Paths ATM Virtual Circuits, MPLS Label Switched Paths(LSP) Link Layer QoS ATM, MPLS, PPP, Frame Relay Physically Layer QoS Wavelengths, Ports, Virtual Circuits

Physical technologies allow for the separation of traffic. The separation may take the form of wavelengths, Virtual Circuits, ports on a device, or frequencies over the air. This is the simplest form of QoS whereby different levels of QoS are provided through traffic separation at the physical layer. For example different wavelengths may provide different services. This type of QoS works well when the transmission media is inexpensive or abundant, but when the resources are limited it becomes inefficient and expensive, for example the Wireless frequency spectrum. ATM currently has the most comprehensive QoS support. The ATM forum has created ATM service categories, each with a different QoS traffic management parameters and performance levels. A more comprehensive introduction to a QoS framework is provided in Appendix A.

#### 1.3 Packet Switching

Both MPLS and ATM have packet switching as the core of the technology. This could be said to form the basis of the ability of these technologies to support QoS. Packet switching means the forwarding of the packet through the switch fabric from the input port to the output port. Scheduling consists of choosing which packet to transmit or forward across the switch fabric when there is more than one packet destined for the same output port. The switch scheduling mechanism thus determines the order in which traffic is forwarded as it traverses a network node. Traffic with higher priority is typically forwarded ahead of traffic with lower priority. The scheduling mechanism may be designed to classify traffic as belonging to different classes or each connection may be assigned a specific bandwidth

share. Thus the scheduling priority determines the amount of latency introduced to the traffic by the switching node. In its simplest form a scheduling mechanism is a simple priority scheme where higher priority connections are always given priority ahead of lower priority traffic. This is usually accomplished using some form of priority scheduling. The problem with this approach is that lower priority traffic may never get serviced, if there is always higher priority traffic entering the switch. More elaborate scheduling schemes provide a weighted approach to the transmission of traffic to improve fairness. In this way lower priority connections will not always yield to higher priority traffic. The ideal scheduling situation is when every connection gets its exact share of the bandwidth at every moment. This is called Generalised Processor Sharing, and is a fluid system, and is not possible to implement exactly in Packet Switched Networks.

It has been shown that the element that has the most effect on the QoS provided by packet switched networks is the mechanism that determines which packets will be transmitted next on the output link. We will refer to this mechanism as the traffic scheduling algorithm. Although this traffic scheduling algorithm is the basis for the provision of QoS, as has been shown the successful provision of QoS is also dependant on various other technologies at different layers in the protocol stack.

## 1.4 Scheduling in a Packet Switch

One of the major barriers to building high performance networks is the difficulty of high speed switching. With the introduction of fibre optics the performance bottleneck has moved from the transmission media to the switching node. Many ATM switches have been proposed in the literature and this is still an area of active research.

The aim of this dissertation is to focus on scheduling strategies for packet switches. Although it is impossible to separate the scheduling mechanism from the switching fabric, we make certain assumptions on the architecture of the switching fabric. The switch fabrics considered all fall into the space division, internally non-blocking category. These fabrics provide multiple concurrent paths between the input and output ports and allows multiple cells to be simultaneously switched across the fabric, assuming that all cells are destined for distinct outputs. This dissertation investigates the issues involved in the design of scheduling algorithms.

Scheduling mechanism that packet switches use can be generally classified into two categories depending on whether cells are buffered at the inputs or the outputs of the

switch. Scheduling algorithms for input buffered and output buffered switches are investigated in this thesis, although the main focus is input buffered switches.

Output buffered switches are examined first. Traditionally ATM switches have employed output queuing. Switches with output queues are conceptually simpler and were more popular before the recent interest in input queued switches. In output queuing, when packets arrive at an input port they are transferred by a high speed switching fabric to the correct output port. At the output port a scheduling mechanism then allocates the output bandwidth to the different connections according to a specific policy. The function of the scheduling mechanism is thus to select the particular packet to be transmitted next on the output link.

Scheduling algorithms for output buffered switches are currently able to offer guaranteed bandwidth protection to individual connections, however for various reasons, mainly due to speed limitations, output buffered switches are not practical for all but the smallest switches. These factors are investigated more completely in the following chapters.

To overcome the many problems associated with output queuing, input queuing is being widely investigated. In an input buffered switch cells are buffered at the input ports of the switch. A set of paths must be established in the switch fabric for transmitting packets from the input ports to the output ports of the switch. Input Buffered have their own set of problems, the most serious is that they are currently not able to offer any meaningful delay guarantees to connections.

### 1.5 The Evaluation of Scheduling Mechanisms

The evaluation of scheduling algorithms is a non trivial exercise. There are many factors to consider and often trade offs need to be made. Most of the considerations apply to both output and input queued switches; however there are some which apply exclusively to each. We now briefly discuss some of the issues involved in the design of a scheduling mechanism.

Perhaps the primary requirement for a scheduling algorithm is that it should be able to isolate a connection from the effects of other possibly misbehaving connections. This means that the scheduling algorithm must provide per connection isolation. There are certain QoS frameworks which provide different classes of service to different types of

applications, for example guaranteed delay traffic would always have the highest priority. However providing per connection QoS means that a scheduler should also be able to isolate traffic belonging to the same class. Note that the ability to isolate traffic is necessary even if policing mechanism are used to shape traffic entering the network, since traffic can become bursty while in the network.

A scheduling algorithm should also be able to effectively utilize the available bandwidth. In other words the algorithm should be able to achieve the benefits of statistical multiplexing, while also being able to handle bursty sources. It should be able to do this in real-time as well. For example if a low delay, high priority connection is not using its bandwidth, it should be instantly available to low priority traffic, but as soon as the high priority application requires its bandwidth capacity, it should be available.

A scheduling algorithm should preferably minimize the delay that cells encounter as they are routed across the switch. This delay should preferably be independent of the behaviour of other connections. If a switch is not able to provide proper traffic isolation, behaving connections end up enduring unwanted delay. Algorithms which provide proper traffic isolation may still differ considerably in their ability to provide low delay.

Another requirement is that the scheduling mechanism implementation should also be fair. This is not exactly the same as providing traffic isolation. The algorithm should attempt to allocate each connection its fair share of bandwidth every instant, and should also distribute excess bandwidth fairly among connections including those with no minimum bandwidth reservations. In reality it is helpful to consider the ability of a scheduling mechanism to offer fair bandwidth distribution over the long term and over short time intervals. While two schedulers may distribute their bandwidth equally fairly over a long time interval, one may for instance penalize a connection for bandwidth received in excess of its reservation at an earlier time. Thus a backlogged connection would be starved until all the other connections are given the same amount of service. This situation would lead to short-term unfairness. Thus two scheduling algorithms having otherwise similar properties may exhibit vastly different fairness properties over the short term. This factor is very important for delay sensitive traffic, such as packet based voice applications.

Scheduling algorithms usually need to be implemented in hardware in high speed networks.

Some of the scheduling algorithms presented in the next chapters perform very well theoretically but are immensely complex. It is important that the scheduling algorithm be

Scheduling algorithms usually need to be implemented in hardware in high speed networks.

Some of the scheduling algorithms presented in the next chapters perform very well theoretically but are immensely complex. It is important that the scheduling algorithm be simple enough to implement in hardware. In ATM the available time for scheduling cells is very short. At ATM speeds less than 3  $\mu$ s are available for scheduling. The result of this is that only hardware implementations are feasible. This places severe restrictions on the complexity of algorithms that can be implemented. For example some of the factors that can increase the implementation complexity of a scheduling algorithm are the need to maintain per cell or per connection timestamps and to generate random numbers. However the scheduling algorithms which don't use timestamps generally provide worse delay bounds and fairness. The scheduling algorithm designer usually has to trade off complexity of implementation with the properties of low delay and good short-term fairness. In practice often the only way to determine whether a scheduling algorithm is feasible and can support the desired speed is to implement it in a prototype.

The scheduling algorithm should also scale well to larger sizes and maintain its performance characteristics. It should also perform equally well at different link speeds. It is quite a difficult task to simultaneously provide good delay bounds to a 150mb/s connection and a 56kb/s connection. Again often the only way to determine if a scheduling algorithm is feasible to implement at a specific switch size is to prototype it.

An important criterion for scheduling algorithms is that they perform well under real network conditions. Real network traffic is correlated and in practice packets arrive in bursts. Understanding the nature of this sort of traffic and evaluating its impact are important for the design of network elements. Many ways of modelling traffic bursts in network traffic have been proposed. Studies have shown that burstiness has more influence on the performance of output queued switches than input queued switches. In other words burstiness tends to concentrate the conflicts on outputs rather than inputs. Generally burstiness has been shown to increase the queuing delay of a particular connection; however some scheduling algorithms may be more susceptible to decreased performance under bursty traffic.

to mimic a real world switch as closely as possible. For example a typical configuration would be a 16 by 16 switch with up to a few hundred connections on each port.

To model a core network switch the connections would be randomly distributed across all the ports and the destinations would also be more or less randomly distributed. To model a network edge switch all the input ports connections destination would be focused all on one or two of the output ports, to model a switch connecting several DSL access multiplexers (DSLAMS) to the network.

An important part of the simulation is the choice of traffic model. As is widely known real network traffic is not uniform, and has been shown to be bursty over many time scales. Ideally the traffic model should mimic real network traffic as closely as possible. The modelling of real network traffic is a complex topic. Generating a bit stream that closely approximates real traffic is processor intensive, while using a trace from real network traffic requires large disk space and is slow. While a life-like traffic model is useful to determine the performance of a scheduling algorithm under real traffic, using a simple uniform traffic model is useful to gain a more intuitive understanding of the algorithm. It also provides a method of comparing an algorithm's performance with others.

Another consideration is the modelling of the cell queues. A real switch has a finite number of buffers and perhaps only a small number of buffers dedicated to each connection. Other factors which may be considered are the use of early packet discard mechanisms which are usually implemented in real switches. The behaviour of traffic is also not immune to the condition of a switch; a connection experiencing very long switching delays may lower its transmission rate or find an alternative route through the network.

The simulation also needs to be carefully designed so that it is practical to implement in the time and hardware constraints available. A supercomputer would be the ideal simulation platform, but on smaller platforms approximations may have to be made in order to decrease the complexity of the simulation.

#### 1.7 Conclusion

This chapter has provided a review of the current state of QoS in packet switched networks and given a very brief introduction to output buffered switch scheduling and input buffered switch scheduling. In a switch the quality of the service that is offered to the packets of a particular connection depends on several factors including the arrival pattern of the connections traffic, the number of buffers in the switch and the congestion information from downstream nodes. However the most important factor which affects the quality of service is the scheduling mechanism which determines which packet to transmit next on the output link.

In chapter 2, the architecture of ATM switches is investigated in further detail. This chapter provides the necessary background for scheduling in an ATM switch. In chapter 3 scheduling an output buffered switch is presented. This chapter provides an introduction to scheduling in output buffered switches it also lays some of the foundation for material presented in the next chapter. An introduction to Generalised Processor Sharing is presented. The topic of fairness is addressed and in particular the worst-case fairness and service fairness indices are introduced. Some simpler mechanisms are described, followed by some more complicated algorithms which attempt to make provision for per connection QoS. In chapter 4 the topic of scheduling in input queued ATM switches is presented. The development of scheduling algorithms of output buffered ATM switches is covered, and hence this chapter serves as a review of the current state of research into scheduling algorithms for input buffered ATM switches. The chapter starts with an investigation into the benefits of input buffered switches. Algorithms such as maximum size matching and maximum weighted matching are studied. Some of the input scheduling algorithms which have been presented in the literature very recently are reviewed. The methods used to evaluate the performance of input scheduling algorithms are derived from similar methods used in output buffered ATM switches.

In chapter 5, we present the idea of using a multiplying ratio to control the delay that a cell experiences in an input buffered switch. We also present a new algorithm for input buffered switches called *Worst-case Iterative Matching* (WIM). We highlight some of its predicted advantages, and we present a design for implementing it in hardware. In chapter 6, the results of some experiments to determine the performance of WIM scheduling algorithm for input buffered switches compared to other scheduling algorithms for input buffered switches. The chapter is concluded with an investigation of the effect of the switch size on the performance of scheduling algorithms for input buffered switches. In

chapter 7 we give a summary of the work which has been conducted, together with some conclusion. We also present some directions for future research.

University of Cale Lown

# Chapter 2 : Overview of ATM switch Architectures

#### 2.1 Overview of ATM switch Architectures

The aim of this section is to provide an introduction to ATM switching. The aim is not to provide an extensive discussion on various switch architectures, but rather to describe general switching fundamentals and to provide a description of the various architectural options. The design of a switch fabric is a complex topic. For a more detailed introduction to the topic of ATM switch architectures see the paper by Turner [1]. Ahmadi and Denzel [2] provide an extensive survey of ATM switching, perhaps a little outdated but still largely relevant. A good review of commercial ATM switches is presented By Chao in [3].

The switching function is performed by a switching fabric. This fabric switches between N links usually of the same speed. A physical port is bi-directional and consists of an input and an output port on the same physical port. There are thus N input ports and N output ports. The input port is usually responsible for VPI/VCI translation. This operation is performed using a look-up table, possibly implemented using Content Addressable Memory (CAM). Other information which may be included in the look-up table is the output port, class of service and priority. The switch fabric routes from the input port to the desired output port and in the case of multicast two or more output ports. In all switches time can be divided into switching slots or the amount of time it takes to switch one cell. The design of the switch fabric has the most impact on the performance of an ATM switch.

There are many ways to categorize ATM switches, but the broadest is according to their structure.

Switch fabrics have been classified into 2 general categories in terms of their structure, namely space division and time division. A time division switch consists of a single dual ported memory block or a common high speed medium such as a parallel bus which is accessed by all input links and output links sequentially. The memory is usually partitioned per output link. A space division switch fabric uses many concurrent spatial paths from each input link to each output link`

ATM switches can also be classified according to their size. Smaller switches (4-16 ports) are usually made up of one switching stage, while larger switches have multiple switching stages. Most ATM switches today use one of several single stage switching techniques. Single stage switches are relatively simple, but of course are limited in the number of ports and also their total throughput. This section reviews the major categories of single and multi stage switches and discusses the key design issues.

### 2.2 Single stage ATM Switches

Most small ATM switches are of the shared memory or shared medium variety. The shared memory switch uses a common memory to transfer cells from the input ports to the output ports. Shared medium switches use a common medium like a bus or a ring.

#### 2.2.1 Shared memory switches

In a shared memory switch cells from the input ports are multiplexed into a single stream and written sequentially into logically partitioned memory. The cells are then written to a particular section of memory depending on their destination. There are several issues affecting the performance of shared memory switches the main one being the structure of the shared memory, for example it can be a common memory for all ports which needs less memory, or it can be partitioned into separate sections for each port. It could also be a combination of both.

#### 2.2.2 Shared medium (Bus)

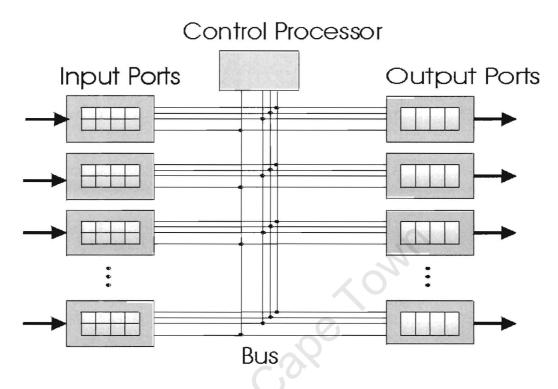

Shared medium switches use a shard medium like a bus or a ring to sequentially send cells to the output ports. Buses are the most common form of single stage switches today. A simple single stage switch is illustrated in figure 2.1. See [1]. The input port processor handles the input processing functions at the ATM layer; this includes synchronizing arriving data to the internal timing of the switch, VPI/VCI translation, checking ATM header errors. To transfer data to the outputs, input port processes contend for access to the shared bus using one of a variety of bus contention techniques. Once an input port has possession of the bus it then transfers a cell or cells onto the bus in parallel form. The input port processor also transmits the output port number on the bus. The output port processors compare the number of the output port on the bus to their own address and buffer matching cells in a queue prior to transmission. The output port may implement a

simple FIFO queue, or several more sophisticated per virtual circuit queues. It may also implement one or more congestion control techniques to improve queuing performance in the presence of bursty data traffic.

Figure 2.1 Bus Based Switch

In addition to the data path components described above, a switch must also have a control processor, which configures the input port routing tables in response to user requests. The control processor must also have control of the queuing system in the output port. The control processor is usually implemented as a general purpose processor with software to perform terminal-to-switch and switch-to-switch signalling, in addition to switch control and maintenance functions. In some systems the control processor is directly connected to the bus and often also has a separate bus connecting it to the memory implementation in the routing tables. This enables the control processor to modify the routing tables. The control processor may be connected to the switch through one of its external ports and communicate control information through the use of ATM cells carried on a specific VPI/VCI. This of course requires that the input and output ports have the ability to interpret and react to control cells. This solution becomes more attractive as the switch size increases as multiple processors may be required to maintain the switch. In order to provide non-blocking transfer medium, a bus supporting n ports, operating at a rate of n bits per second. If the clock

frequency used for the bus is r Hz, the bus width w must be at least  $\frac{Rn}{r}$ . Notice that as the

number of ports in a system increases, both the number of ports connecting to the bus and the width of the bus must increase. This yields quadratic growth factors, making bus based switches unfeasible for larger systems. Another problem with bus based systems is the capacitive loading effect, as the number of ports connecting to a bus increases the capacitive loading of the signal lines increase, thus reducing the maximum frequency that can be used. The result of this is that the bus bandwidth must increase faster than the port count to maintain sufficient bandwidth.

Shared medium switches have the advantage that the technologies that are used to construct them are well developed and commercially available. For example Gigabit Ethernet is one technology that is well suited to building a shared medium switch.

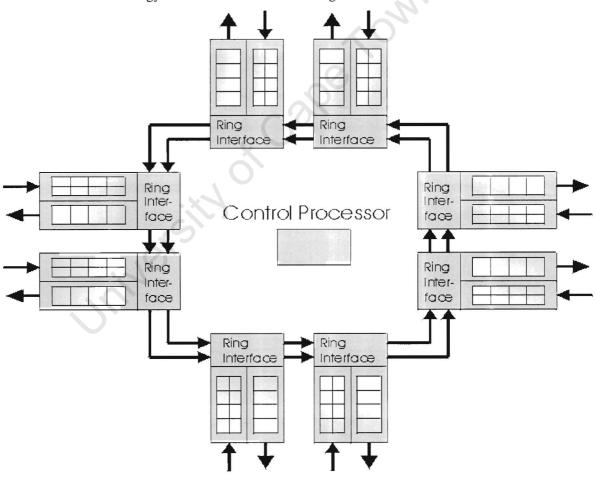

Figure 2.2 Ring Based Switch

#### **2.2.3 Rings**

This switch architecture replaces the bus in the previous section with a ring interconnect system. Each input port or output port interfaces with the ring, which is where cells are inserted or removed from the ring. The simplest ring protocol uses a time slotted approach where cells are sent synchronously during specified time slots, and a busy/idle bit is used to indicate the availability or unavailability of a time slot. An input port which has a cell to send waits for the start of a timeslot in which the busy/idle bit is clear and then changes the value of the bit and then transmits the cell on the timeslot. The ring rotates and the output ports compare the output number of the transmitted cell to their own address and copy the matching cells of the ring. They then change the value of the busy idle bit to indicate that the slot is again available for transmission.

Rings, like buses have quadratic scaling properties; however they are not hampered by capacitive loading effects. Rings do introduce some additional latency, relative to buses, but for switching applications these latencies are not that significant. If carefully designed they also may allow for more than one cell to be switched in each time slot.

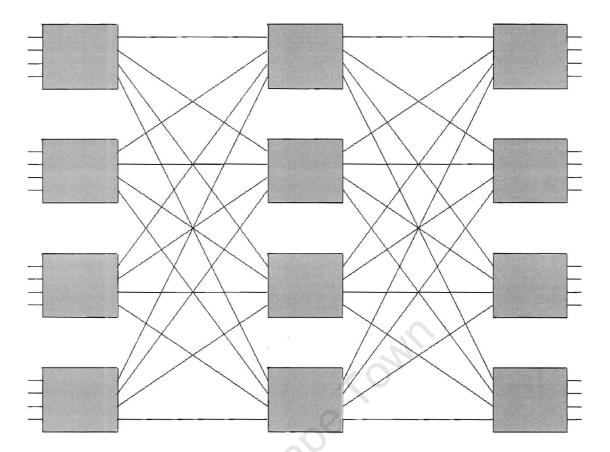

# 2.3 Multistage Switches

Single stage switching techniques are inherently limited by their inability to scale to larger sizes. While the use of higher speed cores to handle lower speed ports provides some relief, for any given technology there comes a point where greater amounts of parallelism are needed to obtain higher throughput. For systems implemented using modern integrated circuits, multistage networks using identical small switching nodes are among the most attractive. An example of a multistage network is shown in Figure 2.2. Each of the switch elements is capable of simultaneously switching all of its inputs to all of its outputs (possibly using speedup). Each element may also have a small cell buffer.

Figure 2.3 A Multistage Switch

The most convenient method of classifying space division (multistage) switches is based on whether there is more than one path between any two pairs of input and output ports. If only one path exists it is a single path switch, and if more than one path exists it is a multipath switch. The switching network illustrated in figure 2.3 is multipath.

In order for cells to get from the input ports to the correct output ports there needs to be some method of routing cells through the switch fabric. There are two main classifications of switches in terms of routing, those that use dynamic routing and those that use static routing. In systems that use dynamic routing, each cell is routed independently, spreading traffic as evenly as possible among all different paths between the pair of input and output ports. In static routing systems all cells in a given virtual circuit follow the same path. Static routing networks maintain cell ordering directly, but require explicit path selection and are subject to virtual circuit blocking. Virtual circuit blocking occurs when one cell can't be routed from its input port to its output port, because the resources are in use by another connection. Dynamic routing networks require the use of some other mechanism to restore cell order, after cells emerge from the interconnection network. This usually involves some form of re-sequencing buffer.

#### 2.3.1 Performance of Multistage Switches

After routing, queuing in multistage interconnection networks is the second key performance issue for this class of systems. The design parameters that have the most influence on performance are the speed advantage, the dimensions of the switch elements, their queue organization and queue size, and the absence or presence of inter-stage flow control. In general, large switch elements with shared queues give the best performance for a given total amount of buffering. [2]

In dynamic routed multistage ATM switches only limited studies have been performed for time dependant traffic. For switches that use static routing, the queuing performance in the presence of time dependent traffic is somewhat more problematic. In these systems congestion can occur on any inter stage switch link in the interconnection network. The most effective way to solve this problem [1] is to use separate queues for each virtual circuit that passes through a switch element. In this approach a switch element with a congested output link signals to its upstream neighbours, blocking new cell transmissions for all virtual circuits using the congested link. These signals would be propagated backwards through the network to the input port where typically large buffers are located for the storage of bursts. Note that scheduling algorithms similar to those required for single stage switches are required in each stage of a static routed buffered multistage switch.

The switches considered in this text are static routed switches. The switch is capable of making as many connections as there are ports. For example in a 16 by 16 switch there can be 16 simultaneous connections all originating and destined for separate ports. The exact details of how the cells are switched are not relevant to the operation of the scheduling mechanism.

## 2.4 Queuing in ATM Switches

This section compares the different queueing options that a switch designer might use. Basically cells can be queued at the input or the output of a switch or both or not at all.

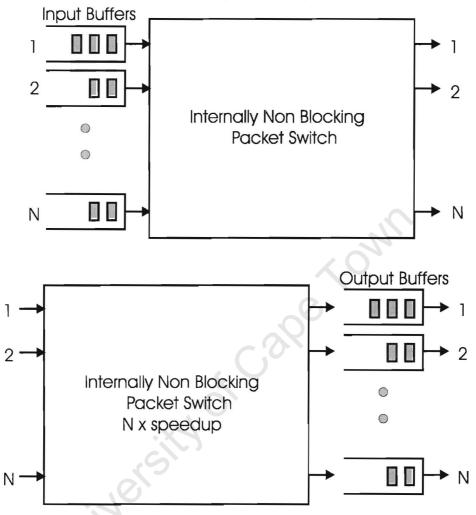

Figure 2.4 Input and Output Queueing

#### 2.4.1 Output Queuing

In output queuing, when packets arrive at an input port they are transferred by a high speed switching fabric to the correct output port. The cells are then transferred into memory to await transmission on the output link. At the output port a scheduling mechanism then allocates the output bandwidth to the different connections according to a specific policy. If there are no input buffers the switch fabric has to be capable of transmitting as many cells as there are ports to any output in any switching interval. This absence of input buffers makes two very demanding requirements on the switch.

#### 2.4.2 Input Queuing

In a switch with only input buffers, cells contend for access to the output port before they enter the switch fabric. Cells that are not selected are stored in the input buffers with cells that arrive in the next time slot. Again the switch fabric transfers at most one cell per unit time slot from each input port. Output buffers are obviously not needed in this case.

When a first in first out (FIFO) service discipline is used for the input buffers the maximum switch throughput is 0.586 of the total switch bandwidth. The maximum throughput of a non blocking switch with FIFO input buffers is thus lower than that of a switch fabric with no buffering. Note that the cell loss performance is still much better for an input buffered switch.

An input buffered switches using FIFO service discipline suffers from head of Line blocking. This means that cells at the head of the queue block which are blocked stop cells which could otherwise be routed to different output ports. A number of methods are available to increase the switching capacity of input buffered switches. One approach is to increase the speed of the switching fabric. Another is to use a non – FIFO input buffered service discipline. This topic is dealt with in more detail in subsequent chapters.

# 2.4.3 Combined Input and Output Queuing

The option of using both input and output buffering has recently received a lot of attention. This combines both the advantages and disadvantages of input and output queueing. The switch fabric is required to be faster than that required for input queueing, but does not need the speed required of a typical output buffered switch. This solution is usually referred to as Combined Input Output Queueing (CIOQ). However in larger switches even a small speed-up is not very practical.

For a switch fabric without any buffers, when output contention occurs, only one cell gets transmitted. The other cells are dropped or recycled into another input link. Assuming the cell switches at most one cell per time slot from each input, this sort of switch generally has a higher probability of dropping cells than the other solutions discussed here.

## 2.5 Buffer Management

The size and the way in which the cell buffers in an ATM switch are allocated in an output buffered switch have a large impact on the performance of the switch. Dedicated per VC queues are required to guarantee buffer space for non congested connections and traffic classes. Large buffers (of the order of several megabytes) are required to support bursty self similar traffic. Sharing a large central memory allows a switch to provide sufficient buffers for each port to handle large traffic bursts with a smaller total amount of memory. The alternative of providing several hundred megabytes on each port can be prohibitively expensive.

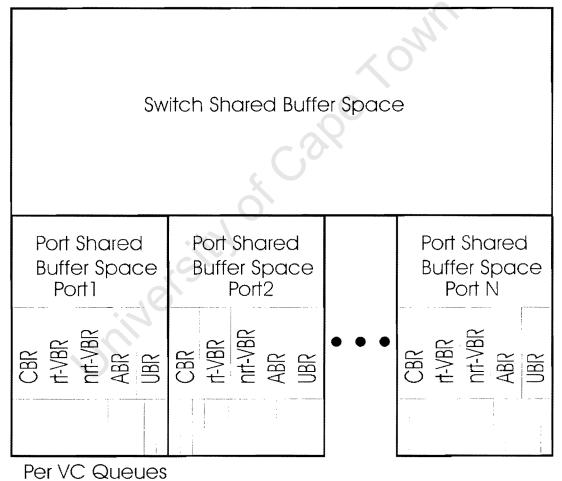

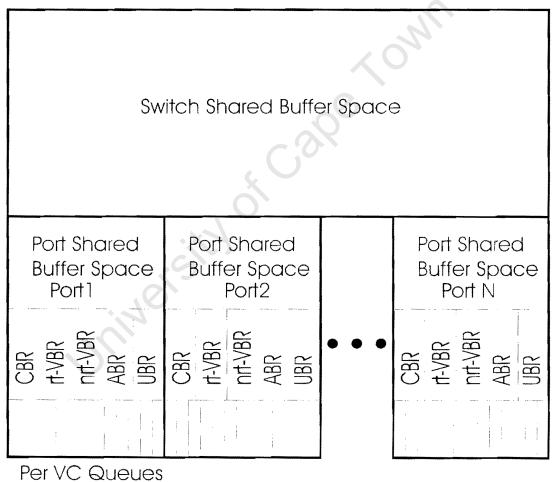

Usually the first step in providing buffer management on an ATM switch is to provide traffic isolation. Non-congested ports and traffic classes should always have available buffer space. The simplest way to achieve this is to assign dedicated queues to the five ATM forum management version 4.0 traffic classes (i.e. CBR, rt-VBR, nrt-VBR, ABR, and UBR). A Typical buffer allocation scheme is shown in figure 2.5.

Figure 2.5 Buffer Allocation in an ATM switch

## 2.5 Buffer Management

The size and the way in which the cell buffers in an ATM switch are allocated in an output buffered switch have a large impact on the performance of the switch. Dedicated per VC queues are required to guarantee buffer space for non congested connections and traffic classes. Large buffers (of the order of several megabytes) are required to support bursty self similar traffic. Sharing a large central memory allows a switch to provide sufficient buffers for each port to handle large traffic bursts with a smaller total amount of memory. The alternative of providing several hundred megabytes on each port can be prohibitively expensive.

Usually the first step in providing buffer management on an ATM switch is to provide traffic isolation. Non-congested ports and traffic classes should always have available buffer space. The simplest way to achieve this is to assign dedicated queues to the five ATM forum management version 4.0 traffic classes (i.e. CBR, rt-VBR, nrt-VBR, ABR, and UBR). A Typical buffer allocation scheme is shown in figure 2.5.

Figure 2.5 Buffer Allocation in an ATM switch

Switched cells are placed in an appropriate queue based on origin, destination and traffic class. If the per connection becomes congested the traffic will back up into the traffic class queue. If the dedicated traffic class queue fills up then the traffic backs up into the port shared buffer space. If the per port shared buffer fills up the traffic backs up into the shared switch memory.

## 2.6 Summary

As stated the aim of this dissertation is to focus on scheduling strategies for ATM switches. Although it is impossible to separate the scheduling mechanism from the switching fabric, we make certain assumptions on the architecture of the switching fabric. The switch fabrics considered all fall into the space division, internally non-blocking and internally blocking category. These fabrics provide a limited number of concurrent paths between the input and output ports and thus allow multiple cells to be simultaneously switched across the fabric.

In the case of output buffered switches it is assumed that all required cells can be switched, while in the case of input buffered switches only cells that are destined for separate outputs can be switched. This dissertation investigates some of the issues involved in the design of scheduling algorithms for this sort of switch.

# **Chapter 3 : Scheduling in Output Buffered Switches**

#### 3.1 Introduction

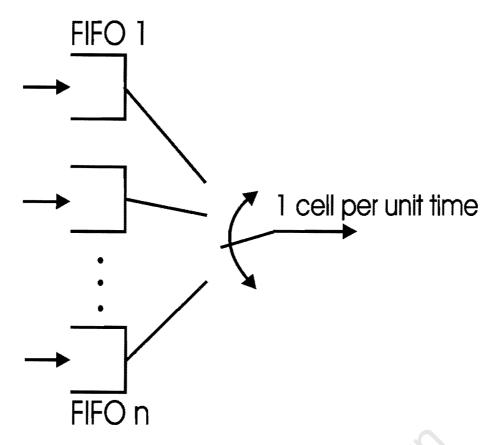

As scheduling for output buffed switches is generally a simpler topic than scheduling for input buffered switches we discuss this topic first. Some of the material presented here is necessary for the following chapter. Traditionally ATM switches have employed output queuing. They are conceptually simpler and provide a benchmark for the performance of input buffered switches which are examined later. In output queuing, when packets arrive at an input port they are transferred by a high speed switching fabric to the correct output port. At the output port a scheduling mechanism then allocates the output bandwidth to the different connections according to a specific policy. See figure 3.1. The function of the scheduling mechanism is thus to select the particular packet to be transmitted next on the output link.

Figure 3.1 Scheduling in an Output Buffered ATM Switch

The main function of this output scheduling mechanism function is to provide the desired service to each connection. Each ATM connection has a set of ATM forum traffic management parameters, and these should be supported by the ATM switch.

## 3.2 Output Scheduling Algorithms

Many scheduling mechanisms for output buffered switches have been proposed in the literature in recent years, in the general context of connection orientated packet network architectures with explicit resource allocation and admission control policies. One of the first to studies to investigate fair scheduling was by Demers Keshav and Shenker in [4]. Many have since followed. This section aims to give a review of some of the algorithms proposed in the literature. The area of investigation will be restricted to rate based scheduling algorithms. A rate based service discipline is one that attempts to provide connections with a service rate, independent of the traffic characteristics of other clients [5]. Typically such a discipline manages the following resources at an output port: bandwidth, service priority, and buffer spaces. In conjunction with appropriate admission

policies, such disciplines allow clients to get performance guarantees in terms of throughput, delay, jitter and loss rate.

# 3.3 Generalized Processor Sharing

Generalised Processor Sharing (GPS) is the ideal theoretical scheduling algorithm, first proposed for use in broadband networks in [6]. Generalised Processor Sharing is defined with respect to a fluid model. In GPS each connection gets its fair share of the total available bandwidth at every instant. It is thus a fluid system and can not be exactly implemented in practice.

A GPS server serving N sessions is characterised by N positive real numbers,  $\phi_1, \phi_2, ..., \phi_N$  which represent the bandwidth that each of the N connections will receive. The server operates at a fixed rate r and is work conserving (If there are packets available to switch it will always switch them) If  $W_i(t_1, t_2)$  is the amount of traffic from session i

served in the interval  $(t_1, t_2)$  then a GPS server is defined as one for which

$$j = 1, 2, \Lambda, N$$

$$\frac{W_i(t_1, t_2)}{W_i(t_1, t_2)} \ge \frac{\phi_i}{\phi_j}$$

(1)

holds for any session i that is backlogged throughout the interval  $[t_1,t_2]$ . From the definition, it follows that  $B_{GPS}(\tau)$  the set of backlogged sessions at time  $\tau$  remains unchanged during any time interval  $[t_1,t_2]$ , the service rate of session i during the interval will be exactly

$$r_i^*(t_1, t_2) = \frac{\phi_i}{\sum_{j \in GPS(t_1)} \phi_j} r$$

(2)

Where r is the output link speed. Since  $B_{GPS}(t_l)$  is a subset of all the sessions on the server, it is easy to see that  $r_i^*(t_1, t_2) \ge r_i$  holds where:

$$r_i = \frac{\phi_i}{\sum_{j=1}^i \phi_j} r \tag{3}$$

Therefore session i is guaranteed a minimum service rate of  $r_i$  during any interval when it is backlogged.

Of course realise that GPS is an idealised server that does not transmit packets as entities or even as bits. It assumes that the server can serve all backlogged sessions simultaneously and that the traffic is infinitely divisible. In packet system, only one session can receive service per timeslot.

In order to implement a GPS-like scheduling policy in practice many packet approximations have been proposed. These approximations generally involve the computation of a virtual finishing time for each packet and the computation of a system virtual time. The packets are then scheduled in increasing order of their virtual finishing times. These algorithms are usually referred to as Packet Fair Queuing (PFQ) algorithms.

# 3.4 Fairness in Output Buffered Switches

The service provided by a scheduling mechanism to a group of connections can differ significantly over the short term. The generally accepted definition of fairness is that we would like to serve connections in proportion to their reservations and distribute unused bandwidth among connections which are able to use it. (Not all connections can use excess unused bandwidth). However allowances also have to be made for connections which have no reserved bandwidth which only use excess bandwidth (UBR connections). Fairness can also be defined in terms of average delay jitter, some connections require this parameter to be very low, and it would be unfair to give one of two identical connections a low average delay jitter and the other one a much larger average jitter. Two indices for determining the performance of an ATM scheduling mechanism have been proposed in the Literature. These are the Service Fairness Index and the Worst-case Fairness Index.

#### 3.4.1 The Service Fairness Index

The Service Fairness Index(SFI), originally introduced by Golestani in [7] is the maximum difference of normalised service that two sessions i, j can receive during any time interval when they are continuously backlogged:

$$F_{i,j} = \max_{\substack{n_1 < n_2 \\ i,j \in B(n_1,n_2)}} \left| \frac{W_i(n_1, n_2)}{r_i} - \frac{W_j(n_1, n_2)}{r_j} \right|$$

(4)

where  $W(n_1, n_2)$  is the number of cells session transmitted by the server between timeslot  $n_1$  and  $n_2$ , and  $B(n_1, n_2)$  is the set of sessions that are continuously backlogged between  $n_1$  and  $n_2$ . The SFI captures the difference in fairness of the scheduler from the ideal fairness of GPS in distributing service to connections that are continuously backlogged.

#### 3.4.2 The Worst-case Fairness Index

The Worst-case Fairness Index, defined by Parekh in [8] and also used by Bennett and Zhang in [9], measures the maximum amount of time that a backlogged connection may have to wait between two consecutive services. In the case of ATM., the WFI can only be measured in cells and a Cell Worst Case Fairness Index (C-WFI) is thus defined. A scheduler is called worst-case-fair if the C-WFI for any session *i* is minimal and independent of the total number of allocated sessions. The distribution of service to competing connections in a scheduler with small C-WFI is closer to GPS than in a scheduler with identical SFI but larger C-WFI.

Parekh's definition of the Worst-case Fairness Index for output buffered switches is presented here for completeness and for comparison with the WFI for input buffered switches which is presented in the next chapter.

**Definition 1** A service discipline s is called worst case fair for session i, if for any time  $\tau$ , the delay of a packet arriving at  $\tau$  is bounded by  $\frac{1}{r_i}Q_{i,s}(\tau)+C_{i,s}$ , i.e.,

$$d_{i,s}^{k} < a_{i}^{k} + \frac{Q_{i,s}(a_{i}^{k})}{r_{i}} + C_{i,s}$$

(5)

where  $r_i$  is the throughput guarantee to session i,  $Q_{i,s}(a_i^k)$  is the queue size of session i at time  $a_i^k$  and  $C_{i,s}$  is a constant independent of the other sessions sharing the multiplexer.  $d_{i,s}^k$  is the departure time of the packet. A service discipline is called worst-case fair if it is worst case fair for all sessions.

To perform a comparison between connections with different bandwidth reservations Bennett and Zhang define the Normalised Worst-case Fair Index for session *i* at server *s* to be:

$$c_{i,s} = \frac{r_i C_{i,s}}{r} \tag{6}$$

For a server that is worst-case fair, its Normalised Worst-case Index is defined to be:

$$c_{s,p} = \max_{i} \{c_{i,s}\}\tag{7}$$

GPS is worst-case fair with  $c_{GPS} = 0$ . Thus we can use the Worst-case Index to quantify the service discrepancy between GPS and a another scheduling algorithm, or indeed we can use it to compare any two scheduling algorithms

# 3.5 Practical Output Scheduling Algorithms

Although generalized processor sharing is the optimal scheduler, it is extremely complex if not impossible to implement in practice. Hence various approximations have been suggested and the following section reviews theses schedulers, which vary in their performance, complexity

#### 3.5.1 Weighted Round Robin Scheduling

In round robin schedulers the time axis is split in frames of a certain maximum size. In each frame packets from different channels are serviced in a round robin manner. A credit counter is associated with each connection, and this counter is decreased each time a packet from a connection receives service. Credit counters are reset at the beginning of a frame to the maximum amount of traffic that the connection may transmit during a frame, and a connection is not eligible for service if its credit counter is zero. The simplicity of the algorithm allows a high speed hardware implementation.

The maximum delay a packet will encounter is proportional to the maximum frame size and the requirement for a fine bandwidth allocation results in a large frame size and hence a high end-to-end delay bound. Thus WRR makes a good scheduling algorithm for separating classes of traffic but it is not as good at scheduling individual connections.

#### 3.5.2 Packet-by-packet Generalised Processor sharing Policy (PGPS)

PGPS was proposed in [4] by Demers, Keshav and is also called Weighted Fair Queueing (WFQ) and was the first proposed policy to approximate GPS for packet transmission. In this policy a GPS server is emulated to transmit packets: each packet receives a virtual service starting timestamp and a virtual service finishing timestamp. These represent the times that the packet would start and complete transmission through the server in a GPS system. Then the packets are scheduled in ascending order of their virtual finishing timestamps. A virtual time function (also called the system potential) is defined as

$$P^{PGPS}(t) = P(t_0) + \frac{r(t - t_0)}{\sum_{i \in B(t_0, t)} \phi_i}$$

(8)

Where  $B(t_0, t)$  is the set of backlogged session in interval  $[t_0, t]$

The virtual starting and finishing timestamps  $(S_i^j, F_i^j)$  of the *i*th session's *j*th packet are computed as

$$S_i^j = \max(F_i^{j-1}, P(a_i^j)) \tag{9}$$

$$F_i^j = S_i^j + \frac{l_i^j \cdot r}{\phi_i} \tag{10}$$

where  $I_i^j$  is the size of the jth packet of session i and  $a_i^j$  is its arrival time. Notice that the

rate at which the virtual time is updated every time the set  $B(r_0,t)$  changes due to the ending or beginning of a session's transmission. PGPS requires a computation of the system potential which requires a real time simulation of GPS. This is the major drawback of the PGPS policy because the complexity of virtual time updating is in O((N)) in an ATM network, where N is the number of connection. ATM networks would generally have a great number of sessions in parallel and the traffic is likely to be very bursty, so that the set of backlogged sessions is changing constantly. Therefore the total complexity of PGPS is linear with the number of sessions. It is not very difficult to see that PGPS is thus not a very practical scheduling algorithm to implement in practice. However PGPS does provide the best emulation of GPS. In [6] Parekh demonstrated that for any packet the delay between the real finishing time under PGPS,  $(F^{PGPS}(p))$  and the virtual finishing time  $F^{GPS}(p)$  of a packet of maximum size  $l^{max}$  is given by:

$$F^{PGPS}(p) - F^{GPS}(p) \le \frac{l^{\max}}{r} \tag{11}$$

In a similar manner the inequality (11) provides an upper bound on the advance of the service under GPS compared to the service under PGPS, the PGPS server may be far ahead of the corresponding GPS server. This advance in packet based system is not bounded and may cause discrepancy in the output flows of some sessions, which results in a large delay jitter. An example illustrating this problem was presented by Bennett and Zhang in [9] where they also proposed a solution. A summary of their work (Worst-case Fair Queueing) is presented in a following section.

#### 3.5.3 Self-Clocked Fair Queueing Scheduling (SCFQ)

SCFQ was proposed by Golestani in [7] in order to improve the virtual time computing complexity of the PGPS policy. A SCFQ server schedules the packet having the minimum virtual finishing time in the same way as PGPS. The virtual timestamps are computed according to the same formulae but the virtual time is computed differently. In SCFQ the virtual time is determined only using information from the real system (hence the name SCFQ), without referring to a corresponding virtual time obtained from a simulation.

$P^{SCFQ}(t)$  = the virtual finishing timestamp of the packet in service at time t

Hence the complexity of implementing this algorithm consists of finding the minimal virtual finishing timestamp, which is done in O(logN). Obviously this simplification affects the quality of the service of the scheduler; it introduces some unfairness, which does however remain bounded. It has also been shown that the latency of a session depends on the number of sessions backlogged in the system. Furthermore this policy also suffers from a poor WFI in the same way as PGPS does.

## 3.5.4 Start Time Fair Queuing Policy (SFQ)

The SFQ policy was proposed by Goyal et al [10] in order to offer a scheduling mechanism better adapted to low bandwidth flows. They modified the definition of the virtual time and the packet selection criterion. The virtual time of SFQ is given by:

PSFQ(t) = the virtual start time of packet in service at time t.

The packets are scheduled according to their Virtual starting timestamps instead of their virtual finishing timestamps, which is the main reason why the SFQ policy favours low bandwidth sessions. Such low bandwidth sessions have smaller bandwidth parameters, so their virtual finishing times are greater. Thus under scheduling algorithms using virtual finishing times, packets of low bandwidth connections must wait for the transmission of packets belonging to sessions with larger bandwidth reservations (i.e. smaller virtual finishing timestamps), even if they started transmission previously. This property is desirable for low bandwidth CBR connections which would normally carry delay sensitive voice. Intuitively giving the priority to the low bandwidth sessions will not significantly damage the fairness of the scheduler since these sessions are supposed to emit a smaller number of packets.

#### 3.5.5 Discrete Rate Schedulers

The discrete rate approach was first introduced by Bennett et al in [11]. The discrete rate scheduler is based on the assumption that it is required to support a relatively small number of guaranteed service rates at any time. This assumption is certainly realistic in most if not all ATM switches. In the discrete rate scheduler, backlogged sessions with the same service rate are grouped together in the same rate FIFO queue. When a connection becomes backlogged after being idle, it is assigned a new timestamp and appended at the tail of the corresponding rate FIFO queue. At any time scheduling is only performed among sessions at the head of rate FIFO queues at that time. Since only the timestamps at the head of the queues need to be searched to find the minimum virtual finishing time, the number of timestamps to be searched is greatly reduced (equal to the number of rate FIFO queues). The session selected by the scheduler is extracted from the head of its rate FIFO queue at that time and if still backlogged assigned a new timestamp and queued back at the tail of the rate FIFO queue.