## Improvement in Control and Gain Aspects of Impedance Source Inverters and Converters

By: Zeeshan Aleem

Thesis submitted to the Department of Electrical Engineering, University of Cape Town, in complete fulfilment of the requirements for the degree of Doctor of Philosophy

**Supervisor**: Dr. Simon Winberg

Co-Supervisor: Dr. Moin Hanif

The copyright of this thesis vests in the author. No quotation from it or information derived from it is to be published without full acknowledgement of the source. The thesis is to be used for private study or non-commercial research purposes only.

Published by the University of Cape Town (UCT) in terms of the non-exclusive license granted to UCT by the author.

#### **Declaration**

This thesis was submitted to the Department of Electrical Engineering, University of Cape Town, in complete fulfilment of the requirements for the degree of Doctor of Philosophy. It has not been submitted before for any degree or examination at this or any other university. The author confirms that this thesis is based on his own work, save for which is duly referenced. Portions of this work have been published in peer reviewed journals and at refereed international conferences.

Signed by candidate

Zeeshan Aleem

## Acknowledgments

To my esteemed supervisor, Professor Simon Winberg for his patience, guidance and technical contributions, a heart of gratitude.

To my co-supervisor, Professor Moin Hanif for his support and encouragement, a heart of gratitude.

To Mr. Chris Wozniak and Mr. Philip Titus for their technical support and directions in the laboratory, thank you.

To my colleagues in the AMES research group, Department of Electrical Engineering, University of Cape Town, your valuable insights are highly appreciated.

To my family, especially my mother for her sacrifices and unconditional support. If it was not for them, I would have never achieved this milestone in my life.

#### **Abstract**

Power electronics have revolutionized the concept of power control for power conversion and for control of electrical motor drives. Power electronics has been extensively used in industrial applications since it was first discovered in 1902. Power conversion is one of the most important and prominent applications of power electronics. Impedance source networks cover the entire spectrum of electric power conversions from DC-AC (e.g. inverters), to phase and frequency conversion (AC-AC) in a wide range of applications. A wide variety of topologies and control methods using different impedance-source networks have been presented in the literature to overcome the limitations and problems of traditional voltage source and current source as well as various classical buck—boost, unidirectional, and bidirectional converter topologies. Proper implementation of the impedance-source network with appropriate switching configurations and topologies reduces the number of power conversion stages in the system power chain, which may improve the reliability and performance of the power system.

The main focus of this thesis is to study and analyze different impedance source inverters and their control methods, and the development of improved impedance source power systems that will comprise advanced circuitry and provide higher voltage gains needing less complex systems that together provide more cost-efficient solutions. The systems under considerations would have high frequency electrical isolation and voltage clamping across the DC-link inverter bridge that would resulting in better protection, lower overall system losses, and increased efficiencies. Then parallel techniques will be discussed, analyzed and implemented for the class of impedance source inverters. This parallel operation of ZSIs leads to reduced components stress across the inverter bridges by sharing the currents, interleaving, ease of maintenance, modularity, higher reliability, and (N+1) redundancy.

The scope of impedance source networks is not limited to inverters (i.e., DC-AC power conversion), but covers a wide range of electric power conversion applications including (DC-DC and AC-AC converters). Thus, the last part of this research project will include the development of a new class of transformer based impedance source AC-AC

converters with novel control strategies to increase the input to output gains and to improve the conglomerate characteristics of the AC-AC converters.

Validation of the proposed structures will be done virtually using the Saber, PSIM simulations, and physically using experimental hardware prototypes. Several KW power systems will be fabricated and implemented using a DSP-kit based on the TMS320f28335 processor. Modified modulation schemes will be applied to control the switching of active devices. Furthermore, clamping techniques by minimizing the high frequency loop via clamping diode will be applied to the proposed inverters to limit the voltage overshoots caused by the leakage inductance energy.

The better performance of improved impedance source network (with added benefits of HF isolation and parallelization) to design more resilient and efficient converter topology for various applications such as adjustable speed drives, distributed generation systems, super-capacitor energy storage systems, uninterruptable power supply, dc circuit breakers, electric vehicles, avionics, and electronic loads will attract researchers and professional engineers to explore it in depth.

## **Table of Contents**

| De  | claration  |                                                                | 2     |

|-----|------------|----------------------------------------------------------------|-------|

| Acl | knowledg   | gments                                                         | 3     |

| Ab  | stract4    |                                                                |       |

| Tal | ole of Cor | ntents                                                         | 6     |

| Lis | t of Table | es                                                             | 11    |

| Lis | t of Figur | 'es                                                            | 12    |

| No  | menclatu   | re                                                             | 16    |

| Lis | t of Symb  | ools                                                           | 17    |

| 1.  | Chapter    | 1 Introduction                                                 | 19    |

|     | 1.1        | Background                                                     | 19    |

|     | 1.2        | Problem Statement                                              | 21    |

|     | 1.3        | Aim and Sub-objectives                                         | 23    |

|     | 1.4        | Research Questions                                             | 25    |

|     | 1.5        | Methodology                                                    | 25    |

|     | 1.5.1      | Literature Review                                              | 25    |

|     | 1.5.2      | Research Plan                                                  | 26    |

|     | 1.6        | Research Outputs                                               | 27    |

|     | 1.7        | Organisation and Scientific Contributions of the Thesis        | 29    |

| 2.  | Chapter    | 2 Review of the Z-Source Converter Topologies and their Modula | ation |

| Str | ategies    |                                                                | 31    |

|     | 2.1        | Z-Source Inverter (ZSI)                                        | 31    |

|    | 2.2     | Pulse Width Modulation Strategies for Z-Source Inverters   | 32 |

|----|---------|------------------------------------------------------------|----|

|    | 2.2.1   | Simple Boost Control                                       | 33 |

|    | 2.2.2   | Maximum Boost Control                                      | 35 |

|    | 2.2.3   | Maximum Constant Boost Control                             | 37 |

|    | 2.2.4   | Summary                                                    | 39 |

|    | 2.3     | Transformer-less ZSIs                                      | 40 |

|    | 2.3.1   | Quasi-ZSI (qZSI)                                           | 40 |

|    | 2.3.2   | Diode-Assisted Extended-Boost ZSI (DA-EBZSI)               | 41 |

|    | 2.3.3   | Capacitor-Assisted Extended-Boost ZSI (CA-EBZSI)           | 41 |

|    | 2.3.4   | Switched Inductor ZSI (SL-ZSI)                             | 42 |

|    | 2.3.5   | Switched Inductor qZSI (SL-qZSI)                           | 43 |

|    | 2.4     | Transformer Based ZSIs                                     | 43 |

|    | 2.4.1   | Trans-ZSIs                                                 | 44 |

|    | 2.4.2   | LCCT-ZSI                                                   | 44 |

|    | 2.4.3   | Improved trans-ZSI                                         | 45 |

|    | 2.4.4   | TZSIs                                                      | 45 |

|    | 2.4.5   | Γ-Z-Source Inverter (ΓZSI)                                 | 46 |

| 3. | Chapter | 3 Improved ΓZSI with Clamping Diode                        | 48 |

|    | 3.1     | Introduction                                               | 48 |

|    | 3.2     | Advantages of Improved ΓZSI with Clamping Diode            | 49 |

|    | 3.3     | Working Principle of the Improved ΓZSI with Clamping Diode | 51 |

|    | 3.4     | Boost Factor of Improved ΓZSI with Clamping Diode          | 52 |

|    | 3.5     | Comparisons with the Previous Works                        | 54 |

|          | 3.6               | Simulation Results                                                                             |

|----------|-------------------|------------------------------------------------------------------------------------------------|

|          | 3.7               | Prototyped System Results                                                                      |

|          | 3.7.1             | Platform Selection61                                                                           |

|          | 3.7.2             | Parameter Design of Proposed Inverter components                                               |

|          | 3.7.3             | Experimental Results63                                                                         |

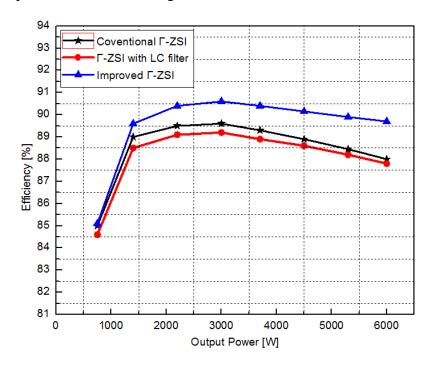

|          | 3.8               | Efficiency Calculation65                                                                       |

|          | 3.9               | Conclusions 68                                                                                 |

| 4.<br>In | _                 | 4 Single-Phase Transformer based HF-Isolated Impedance Source th Voltage Clamping Techniques69 |

|          | 4.1               | Introduction                                                                                   |

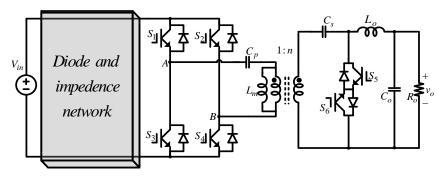

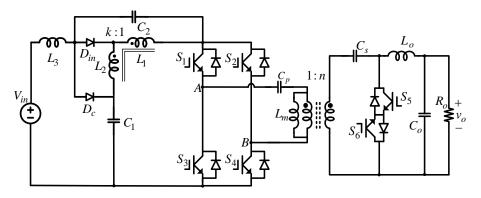

|          | 4.2               | Proposed Isolated Impedance Source Inverter70                                                  |

|          | 4.2.1<br>Analysis | Working Principle of the Improved $\Gamma$ ZSI with Extra Diode and its Circuit 72             |

|          | 4.3               | Pulse Width Modulation Strategy77                                                              |

|          | 4.4<br>diode      | Simulation Results of the Proposed Isolated Improved $\Gamma$ ZSI with additional 78           |

|          | 4.5               | Prototype Type based Validation81                                                              |

|          | 4.5.1             | Parameter Design of High Frequency Transformer81                                               |

|          | 4.5.2             | Experimental Results82                                                                         |

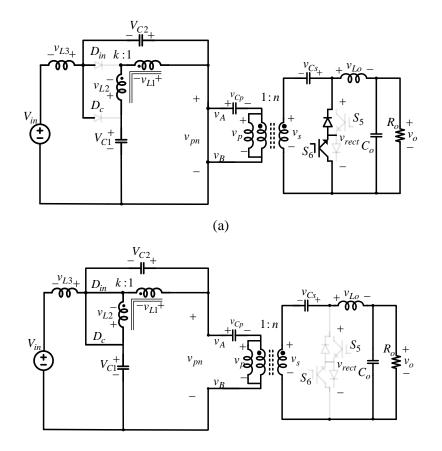

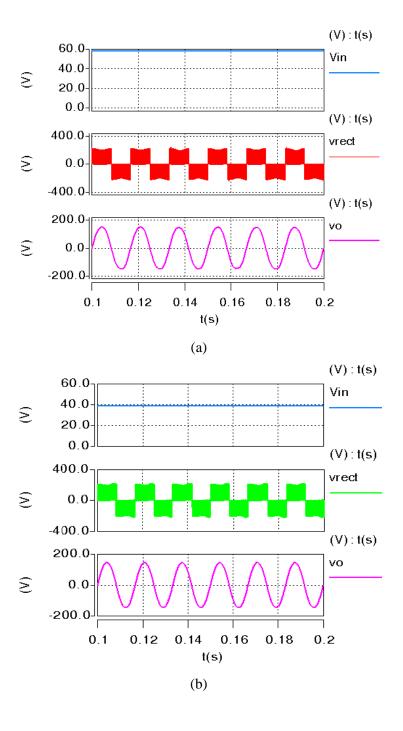

|          | 4.6               | Extension of the Proposed Technique to Magnetically Coupled ZSIs84                             |

|          | 4.6.1             | Simulation Results of the Proposed Isolated Inverters87                                        |

|          | 4.7               | Extension of the Proposed HF Isolation to Transformerless ZSIs90                               |

|          | 4.8               | Conclusions 93                                                                                 |

| 5. Chapter      | 5 Parallel Operation of Improved Z-Source Inverter based on Magnetic   |

|-----------------|------------------------------------------------------------------------|

| Coupling        | 95                                                                     |

| 5.1             | Introduction95                                                         |

| 5.2             | Proposed Parallel Operated Improved Z-Source Inverter Using Magnetic   |

| Coupling        | 96                                                                     |

| 5.2.1           | Working Principle of the Proposed Inverter and its Circuit Analysis97  |

| 5.3<br>Inverter | Interleaved Modulation Scheme for the Proposed Parallel Connected 99   |

| 5.4             | Extension of the Proposed Concept to N-parallel Connected Inverters100 |

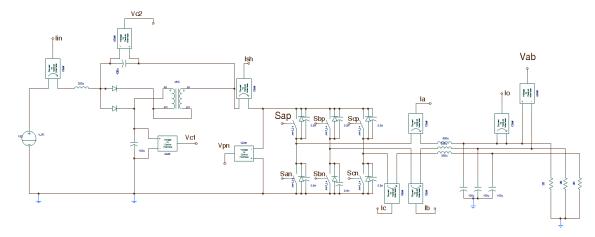

| 5.5             | Simulation Results                                                     |

| 5.6             | Prototyped Based Verification                                          |

| 5.7             | Extension of Paralleling Inverters Concept to Existing ZSIs107         |

| 5.8             | Conclusions 110                                                        |

| 6. Chapter      | 6 Single-Phase Z-Source AC-AC Converters Based on Transformers 111     |

| 6.1             | Introduction                                                           |

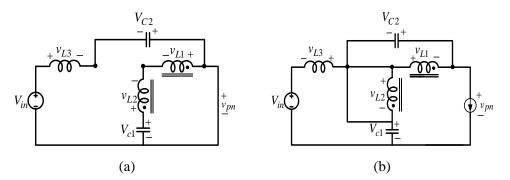

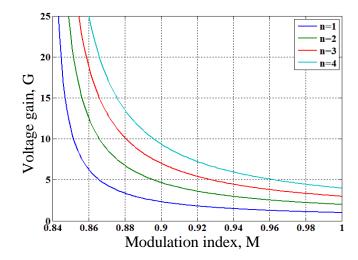

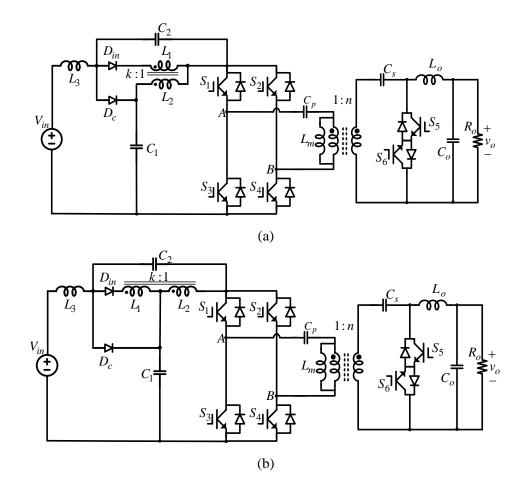

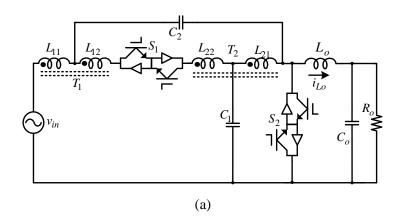

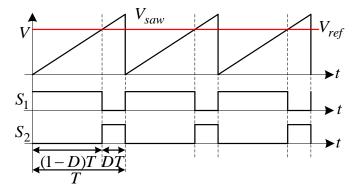

| 6.2             | Proposed Transformer based Z-Source Converters                         |

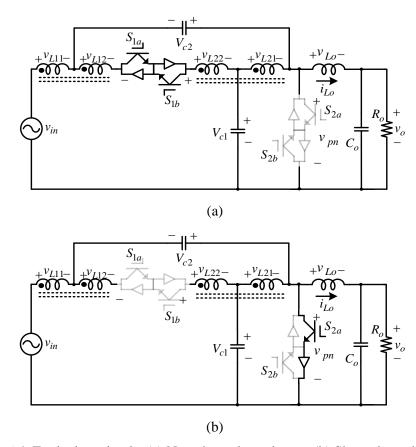

| 6.2.1           | Circuit Analysis of Configuration 1                                    |

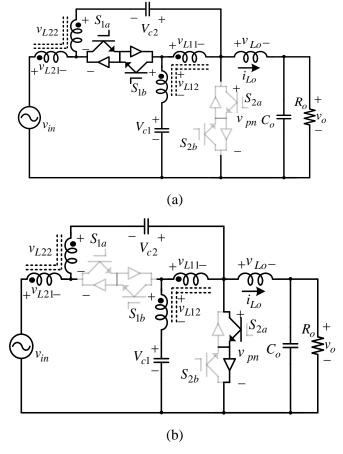

| 6.2.2           | Circuit Analysis of Configuration 2                                    |

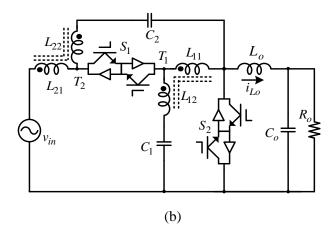

| 6.3             | Commutation Study                                                      |

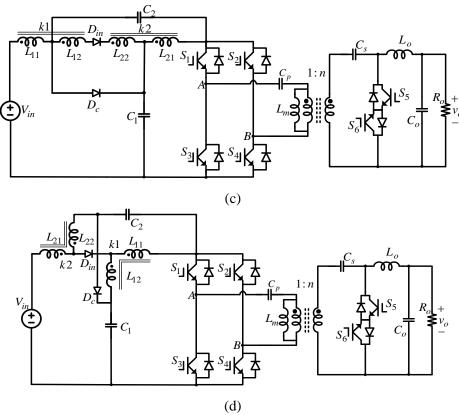

| 6.4             | Simulation Results                                                     |

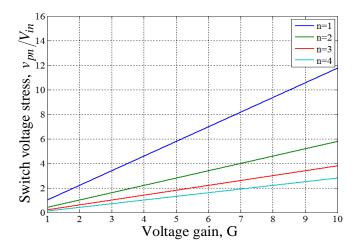

| 6.4.1           | Simulation Results of Circuit Configuration 2124                       |

| 6.4.2           | Simulation Results of Circuit Configuration 1124                       |

| 6.5             | Experimental Verifications                                             |

| 6.6             | Conclusions 135                                                        |

| 7. Chapt   | er 7 Conclusions and Recommendations                       | 136         |

|------------|------------------------------------------------------------|-------------|

| 7.1        | Overview of the Thesis                                     | 136         |

| 7.2        | Important Findings                                         | 138         |

| 7.3        | Recommendations and Future Work                            | 140         |

| Bibliograp | hy                                                         | 142         |

| Appendix . | A                                                          | 150         |

| Assemb     | ly of the Hardware Prototype of Improved ΓZSI with clampin | g diode 150 |

| Appendix   | В                                                          | 152         |

| Coding     | Protocols                                                  | 152         |

| Appendix   | C                                                          | 156         |

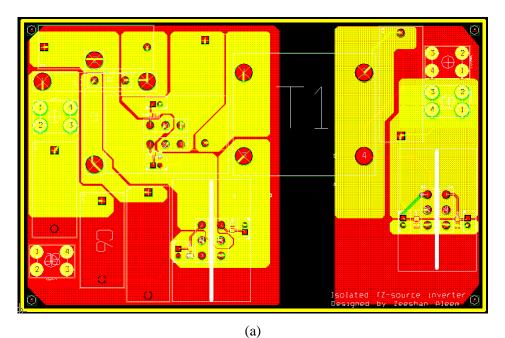

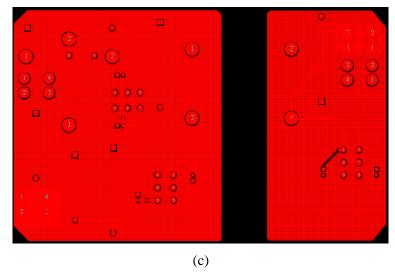

| PCB De     | esign of the Isolated Improved ΓZSI                        | 156         |

| Appendix   | D                                                          | 158         |

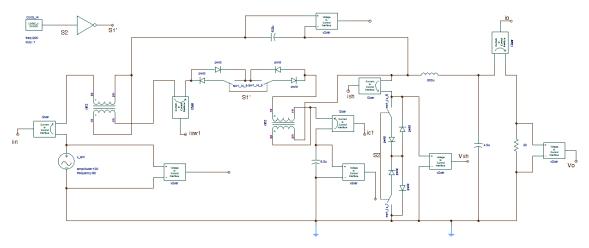

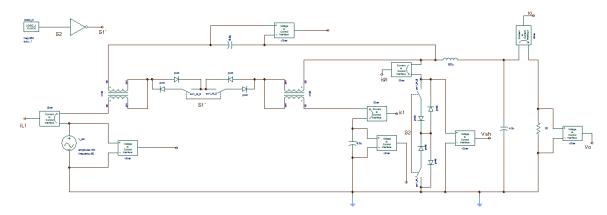

| Simulat    | ion Model of Circuit Configuration 1                       | 158         |

| Simulat    | ion Model of Circuit Configuration 2                       | 158         |

## **List of Tables**

| Table 2.1 | Summary of features of transformer based ZSIs                    | 47   |

|-----------|------------------------------------------------------------------|------|

| Table 3.1 | Summary of voltage stresses                                      | 57   |

| Table 3.2 | Efficiency parameters                                            | 66   |

| Table 4.1 | Electrical specifications for HFT isolated ΓZSI                  | 82   |

| Table 4.2 | Summary of magnetically coupled HF isolated ZSI voltage stresses | 87   |

| Table 4.3 | Summary of transformerless HF isolated ZSIs voltage stresses     | 93   |

| Table 5.1 | Electrical specifications for parallel connected improved ZSI    | with |

|           | magnetic coupling.                                               | .105 |

| Table 6.1 | Switching sequences                                              | 123  |

| Table 6.2 | Summary of AC-AC transformer based ZSIs voltage stresses         | .124 |

| Table 6.3 | Electrical specifications for configuration 1 AC-AC ZSI          | .125 |

| Table 6.4 | Electrical specifications for configuration 2 AC-AC ZSI          | .129 |

| Table A.1 | Electrical and magnetic components                               | .151 |

## **List of Figures**

| Fig. 1.1(a) | Voltage source inverter                             | 20 |

|-------------|-----------------------------------------------------|----|

| Fig. 1.1(b) | Current source inverter                             | 20 |

| Fig. 1.2    | Z-source inverter                                   | 20 |

| Fig. 1.3(a) | Two stage power conversion PV system                | 21 |

| Fig. 1.3(b) | Single stage power conversion PV system             | 21 |

| Fig. 1.4    | Flow chart of the planned research process          | 27 |

| Fig. 2.1(a) | Z-source inverter shoot-through state               | 32 |

| Fig. 2.1(b) | Z-source inverter non-shoot-through state           | 32 |

| Fig. 2.2    | Simple boost control                                | 34 |

| Fig. 2.3    | Voltage gain plot of simple boost control           | 35 |

| Fig. 2.4    | Voltage stress plot of simple boost control         | 35 |

| Fig. 2.5    | Maximum boost control                               | 36 |

| Fig. 2.6    | Voltage gain plot of maximum boost control          | 37 |

| Fig. 2.7    | Voltage stress plot of maximum boost control        | 37 |

| Fig. 2.8    | Maximum constant boost control.                     | 38 |

| Fig. 2.9    | Voltage gain plot of maximum constant boost control | 39 |

| Fig. 2.10   | Voltage stress comparison plot.                     | 40 |

| Fig. 2.11   | Quasi-Z-source inverter.                            | 41 |

| Fig. 2.12   | Diode-Assisted extended-boost ZSI                   | 41 |

| Fig. 2.13   | Capacitor-Assisted extended-boost ZSI               | 42 |

| Fig. 2.14   | Switched inductor ZSI                               | 42 |

| Fig. 2.15   | Switched inductor qZSI                              | 43 |

| Fig. 2.16   | Trans-ZSI                                           | 44 |

| Fig. 2.17   | LCCT-ZSI.                                           | 44 |

| Fig. 2.18   | Improved trans-ZSI                                  | 45 |

| Fig. 2.19   | TZSI                                                | 45 |

| Fig. 2.20   | ΓZSI                                                | 46 |

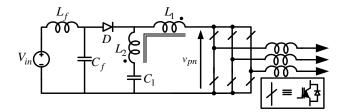

| Fig. 3.1    | ΓZSI with LC filter                                 | 49 |

| Fig. 3.2    | Improved ΓZSI with clamping diode                                            | .49  |

|-------------|------------------------------------------------------------------------------|------|

| Fig. 3.3    | Derivation of improved ΓZSI with clamping diode                              | 50   |

| Fig. 3.4(a) | Improved ΓZSI shoot-through state                                            | 51   |

| Fig. 3.4(b) | Improved ΓZSI non-shoot-through state                                        | 51   |

| Fig. 3.5(a) | Simplified circuit of improved ΓZSI shoot-through state                      | 52   |

| Fig. 3.5(b) | Simplified circuit of improved ΓZSI non-shoot-through state                  | .52  |

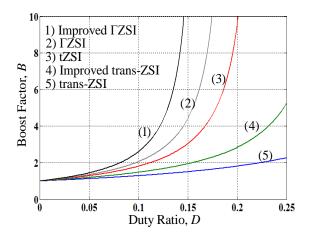

| Fig. 3.6    | Plot of boost factor versus duty cycle for improved ΓZSI                     | .54  |

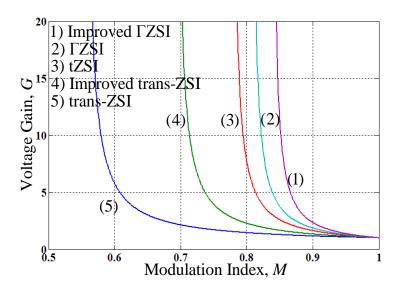

| Fig. 3.7    | Voltage gain against modulation index plot for improved ΓZSI                 | 55   |

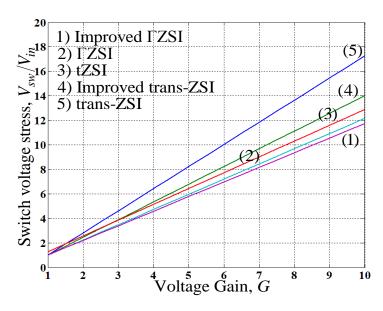

| Fig. 3.8    | Plot of switch voltage stress versus voltage gain for improved $\Gamma ZSI$  | .56  |

| Fig. 3.9    | Block diagram of simple boost control in saber simulation                    | .58  |

| Fig. 3.10   | Simulation results of the conventional ΓZSI                                  | 59   |

| Fig. 3.11   | Block diagram of improved ΓZSI with clamping diode in saber                  | 60   |

| Fig. 3.12   | Simulation results of the improved ΓZSI with clamping diode60                | -61  |

| Fig. 3.13   | Experimental results of input voltage, output voltage, output current        | and  |

|             | capacitor voltages of improved ΓZSI63                                        | -64  |

| Fig. 3.14   | Experimental results of input current and dc-link voltage (with and with     | out  |

|             | clamping diode) of improved ΓZSI                                             | .64  |

| Fig. 3.15   | Experimental waveforms of output inductor currents                           | .65  |

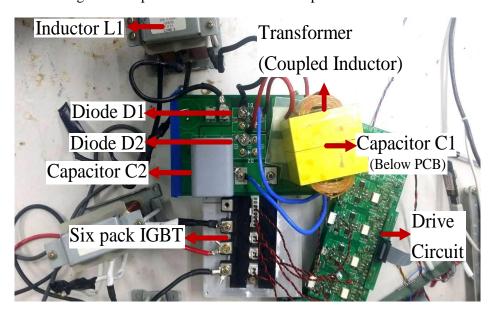

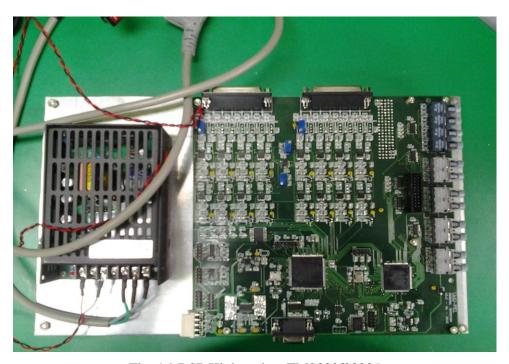

| Fig. 3.16   | Hardware prototype of improved ΓZSI with clamping diode                      | .65  |

| Fig. 3.17   | Efficiency comparison                                                        | 67   |

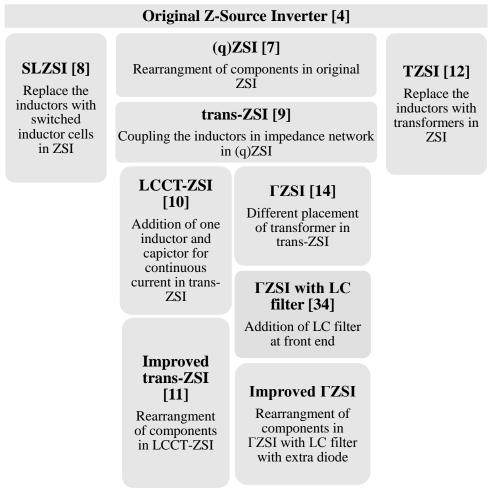

| Fig. 4.1    | Proposed isolated impedance source inverter                                  | .71  |

| Fig. 4.2    | Proposed isolated improved ΓZSI with extra diode                             | .72  |

| Fig. 4.3    | Equivalent circuits of proposed improved ΓZSI with extra diode72             | 2-73 |

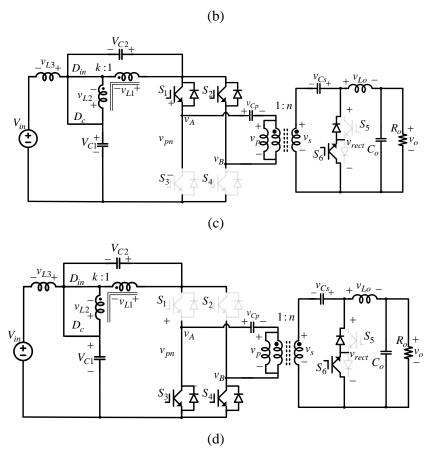

| Fig. 4.4    | Voltage gain versus modulation index plot for different values of $n$        | 76   |

| Fig. 4.5    | Voltage gain versus switch voltage stress plot for different values of $n$ . | 77   |

| Fig. 4.6    | PWM switching pattern for the proposed HFT isolated improved $\Gamma$ .      | ZSI  |

|             | with extra diode                                                             | .78  |

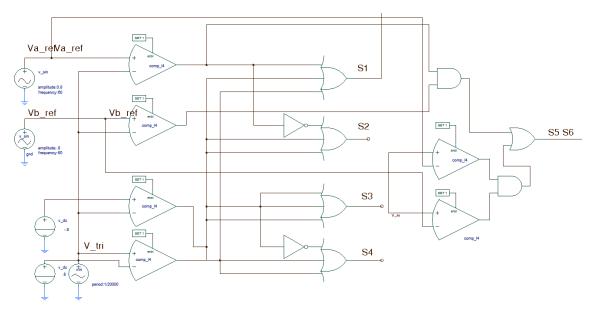

| Fig. 4.7    | Block diagram of control for the proposed class of HFT isolated ZSIs         | .79  |

| Fig. 4.8    | Simulation results of the proposed isolated improved $\Gamma ZSI$            | -80  |

| Fig. 4.9    | DSP Kit based on TMS320F28335                                                | 81   |

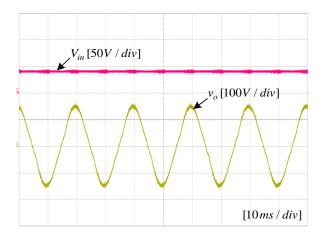

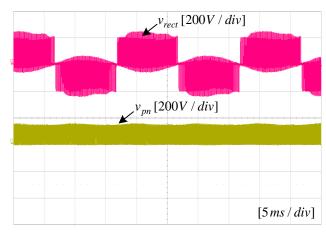

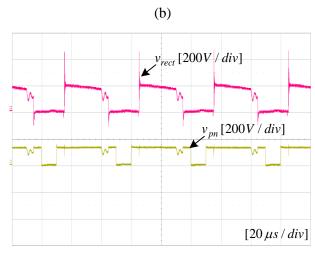

| Fig. 4.10    | Experimental waveforms of the proposed isolated improved $\Gamma ZSI$  | .83-84 |

|--------------|------------------------------------------------------------------------|--------|

| Fig. 4.11(a) | Proposed isolated LCCT-ZSI.                                            | 85     |

| Fig. 4.11(b) | Proposed isolated improved trans-ZSI                                   | 85     |

| Fig. 4.11(c) | Proposed isolated quasi-tZSI                                           | 86     |

| Fig. 4.11(d) | Proposed isolated ΣZSI                                                 | 86     |

| Fig. 4.12    | Simulation results of proposed magnetically coupled ZSIs               | .88-89 |

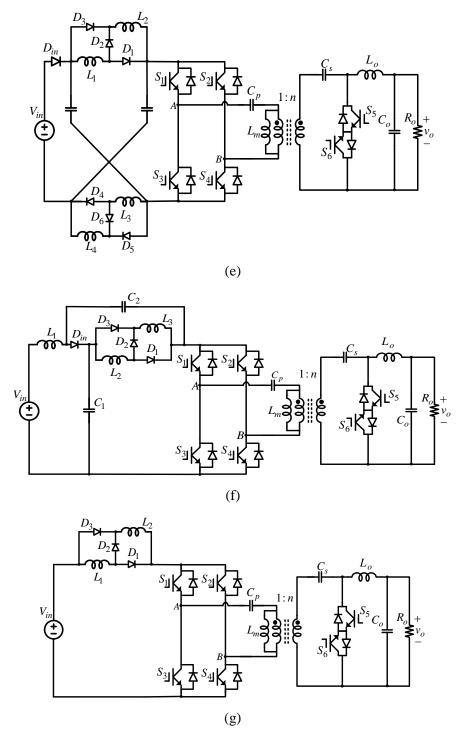

| Fig. 4.13(a) | Proposed isolated conventional ZSI                                     | 91     |

| Fig. 4.13(b) | Proposed isolated qZSI                                                 | 91     |

| Fig. 4.13(c) | Proposed isolated diode assisted extended boost ZSI                    | 91     |

| Fig. 4.13(d) | Proposed isolated capacitor assisted extended boost ZSI                | 91     |

| Fig. 4.13(e) | Proposed isolated SL-ZSI                                               | 92     |

| Fig. 4.13(f) | Proposed isolated SL-qZSI                                              | 92     |

| Fig. 4.13(g) | Proposed isolated LZSI                                                 | 92     |

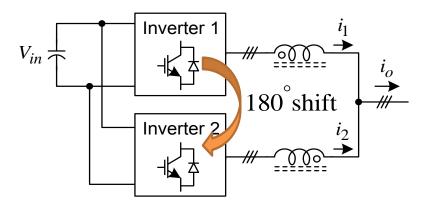

| Fig. 5.1     | Parallel operation of the inverters.                                   | 96     |

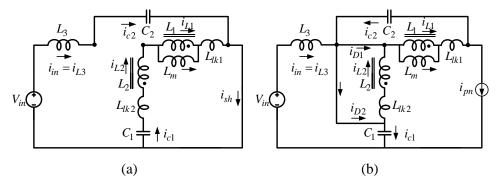

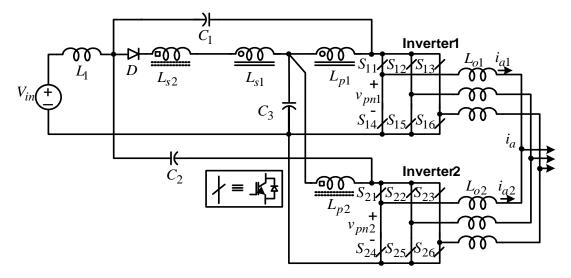

| Fig. 5.2     | Proposed parallel connected improved ZSI based on magnetic coupli      | ng97   |

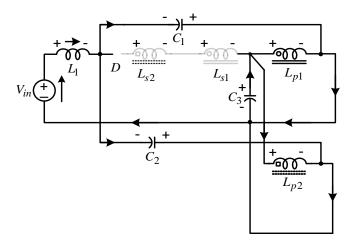

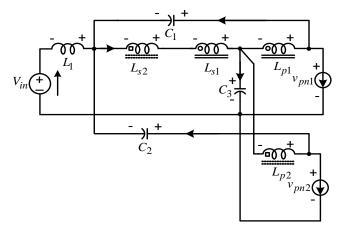

| Fig. 4.3     | Operation modes of the proposed parallel inverter                      | .97-98 |

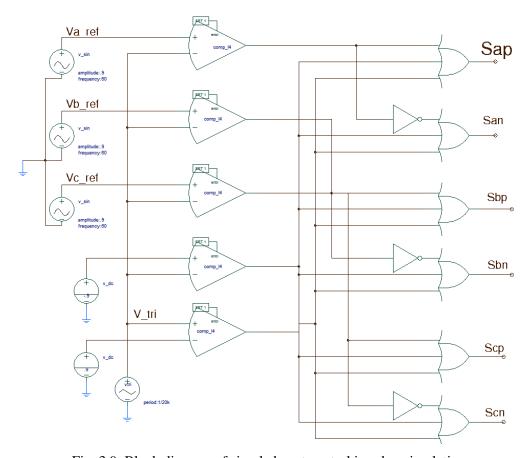

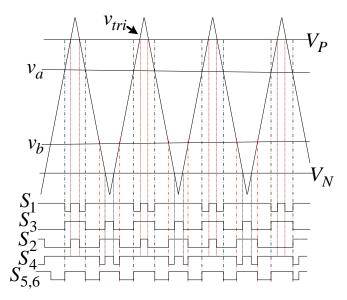

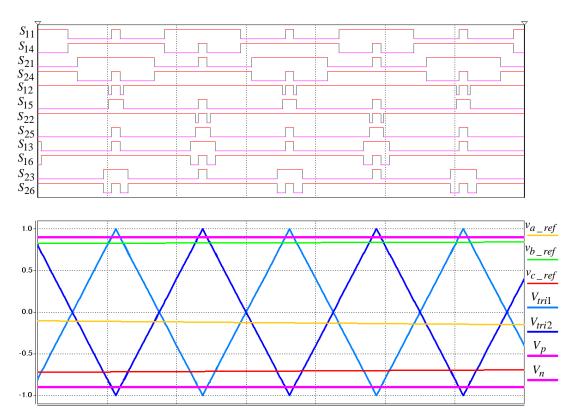

| Fig. 5.4     | Interleaved simple boost control of the proposed parallel inverter     | 100    |

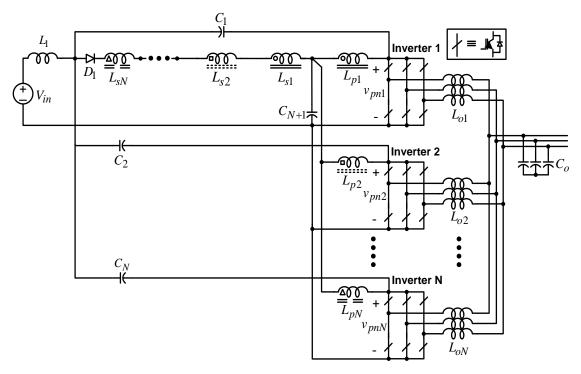

| Fig. 5.5     | Proposed N-parallel connected inverter                                 | 101    |

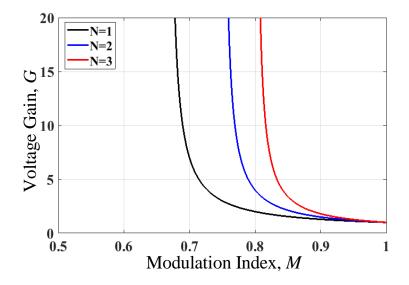

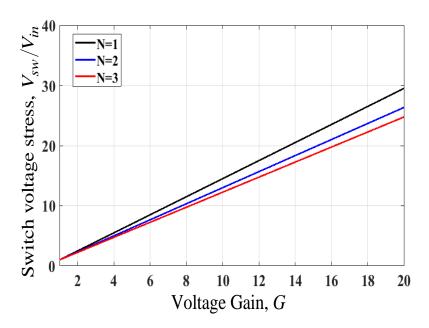

| Fig. 5.6     | Voltage gain versus modulation index plot for different values of $N$  | 102    |

| Fig. 5.7     | Voltage gain versus switch voltage stress plot for different values of | N103   |

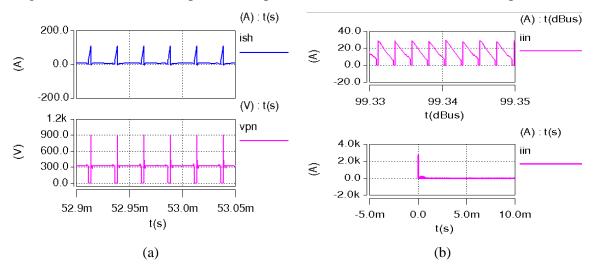

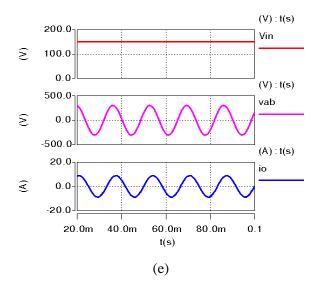

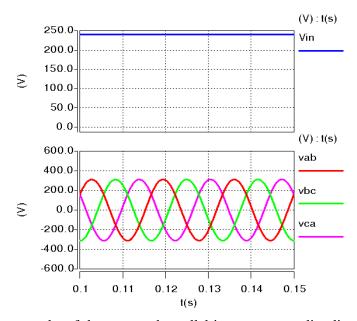

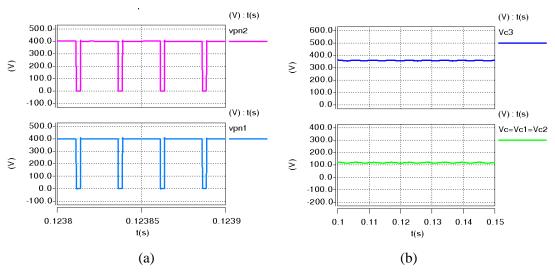

| Fig. 5.8     | Simulation results of the parallel inverter output and input voltage   | 104    |

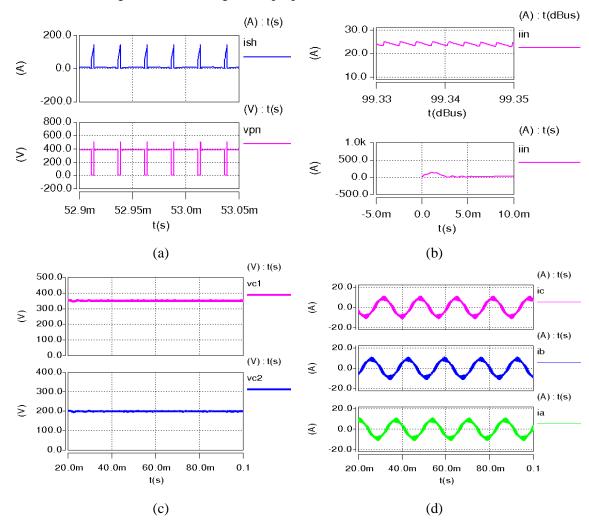

| Fig. 5.9     | Simulation results of dc-link voltages and capacitor voltages          | 104    |

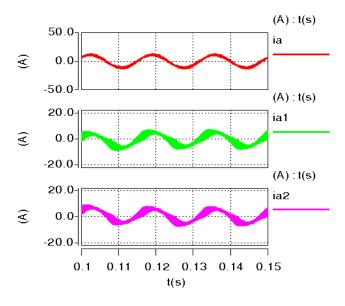

| Fig. 5.10    | Output filter inductor current simulation results                      | 105    |

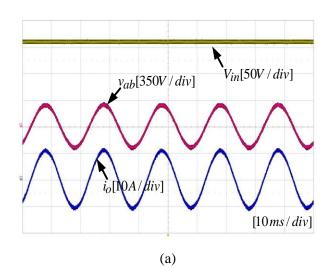

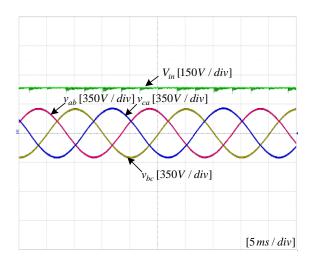

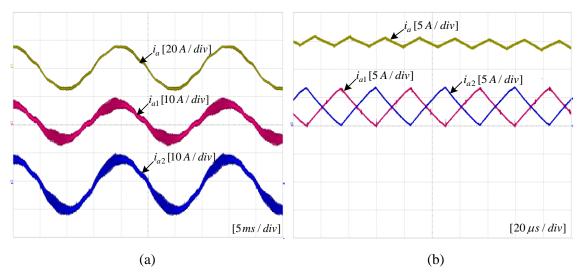

| Fig. 5.11    | Experimental waveforms of parallel inverter output and input voltage   | e106   |

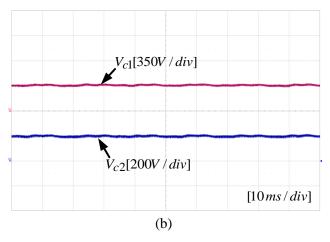

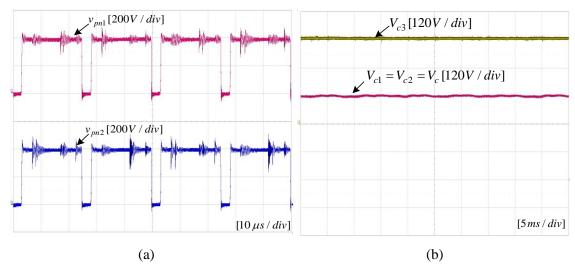

| Fig. 5.12(a) | Experimental results of DC-link voltages                               | 106    |

| Fig. 5.12(b) | Experimental results of capacitor voltages                             | 106    |

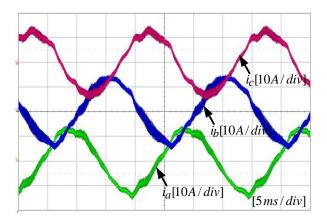

| Fig. 5.13    | Output filter inductor current experimental waveforms                  | 107    |

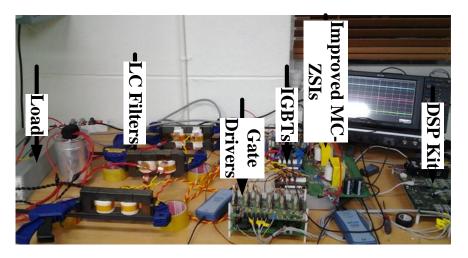

| Fig. 5.14    | Hardware prototype of parallel connected improved MC-ZSI               | 107    |

| Fig. 5.15(a) | Proposed parallel connected qZSI                                       | 108    |

| Fig. 5.15(b) | Proposed parallel connected SL-qZSI                                    | 108    |

| Fig. 5.15(c) | Proposed parallel connected capacitor assisted extended boost ZSI108          |

|--------------|-------------------------------------------------------------------------------|

| Fig. 5.15(d) | Proposed parallel connected diode assisted extended boost ZSI109              |

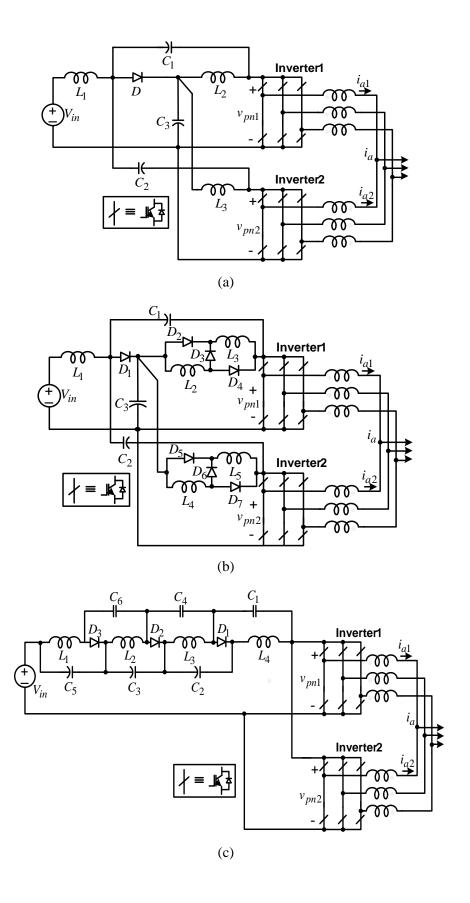

| Fig. 5.15(e) | Proposed parallel connected ΓZSI                                              |

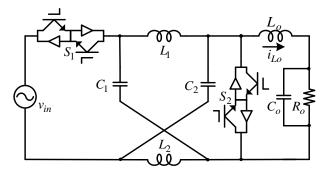

| Fig. 6.1     | Single-phase Z-source AC-AC converter                                         |

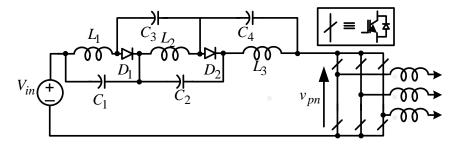

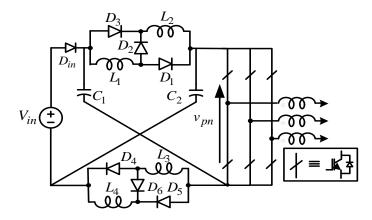

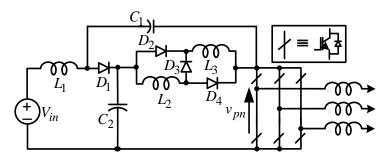

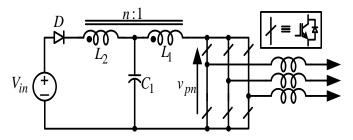

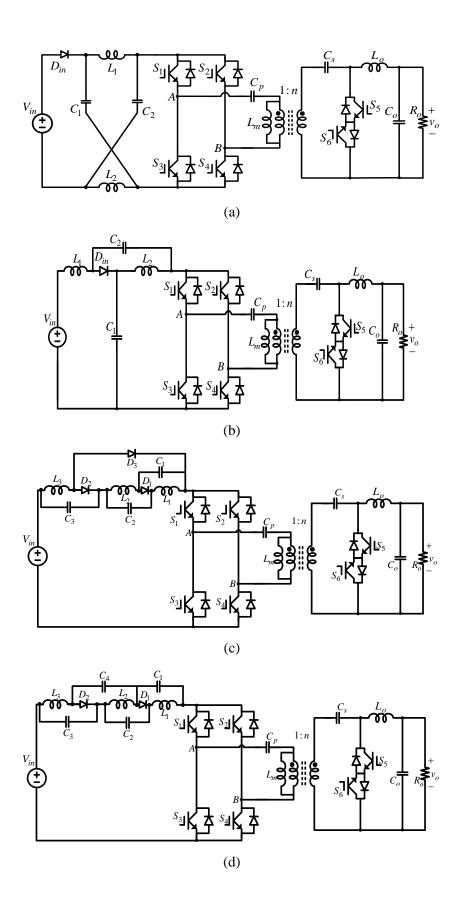

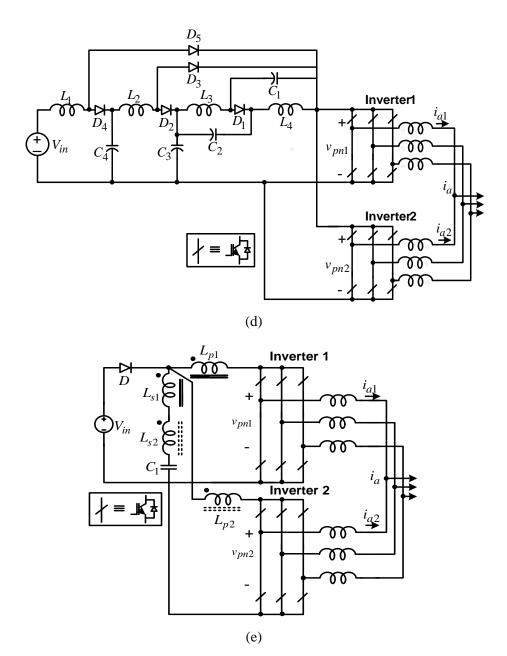

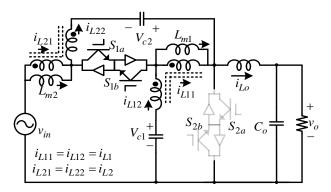

| Fig. 6.2     | Proposed Z-source AC-AC converters based on transformers113-114               |

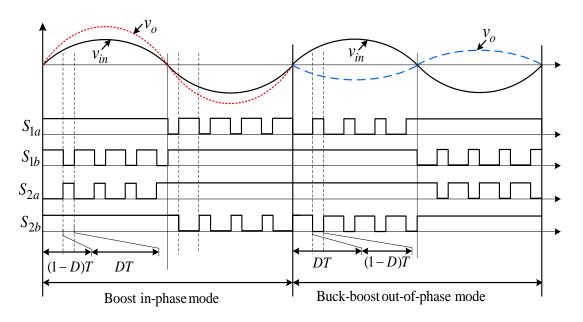

| Fig. 6.3     | Ideal PWM switching signals of the proposed converters114                     |

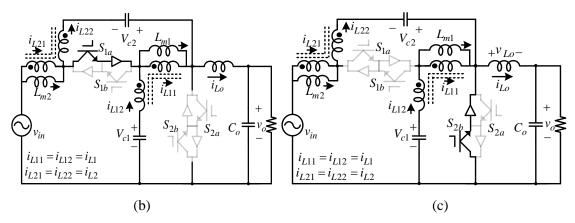

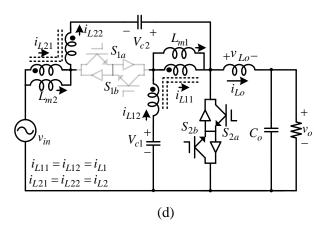

| Fig. 6.4     | Operation modes of proposed converter with configuration 1                    |

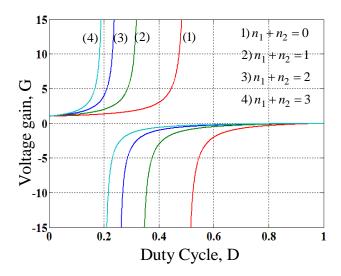

| Fig. 6.5     | Plot of voltage gain versus duty cycle of the proposed configuration 1        |

|              | converter with variable turns ratio                                           |

| Fig. 6.6     | Operation modes of proposed converter with configuration 2                    |

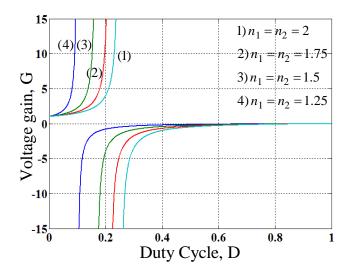

| Fig. 6.7     | Plot of voltage gain versus duty cycle of the proposed configuration 2        |

|              | converter with variable turns ratio                                           |

| Fig. 6.8     | Switching pattern with soft-commutation strategy for the proposed family      |

|              | of converters                                                                 |

| Fig. 6.9(a)  | Non-shoot-through state in boost in-phase mode when $v_{in} > 0$              |

| Fig. 6.9(b)  | Commutation state when $i_{L1} + i_{L2} > i_{Lo}$ in boost in-phase mode when |

|              | $v_{in} > 0$                                                                  |

| Fig. 6.9(b)  | Commutation state when $i_{L1} + i_{L2} < i_{Lo}$ in boost in-phase mode when |

|              | $v_{in} > 0$                                                                  |

| Fig. 6.9(d)  | Shoot-through state in boost in-phase mode when $v_{in} > 0$                  |

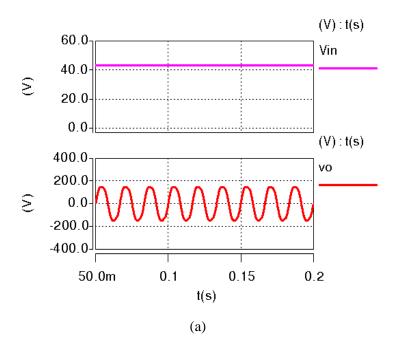

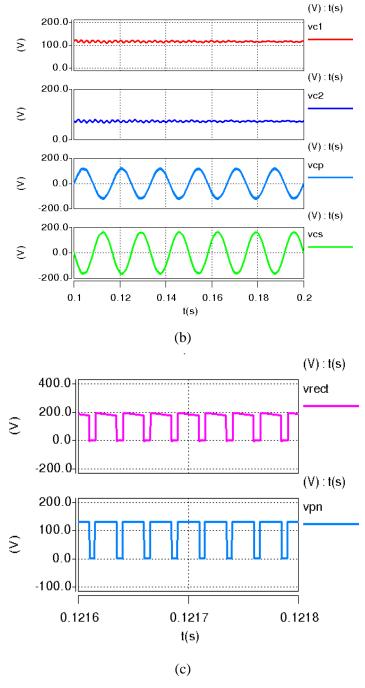

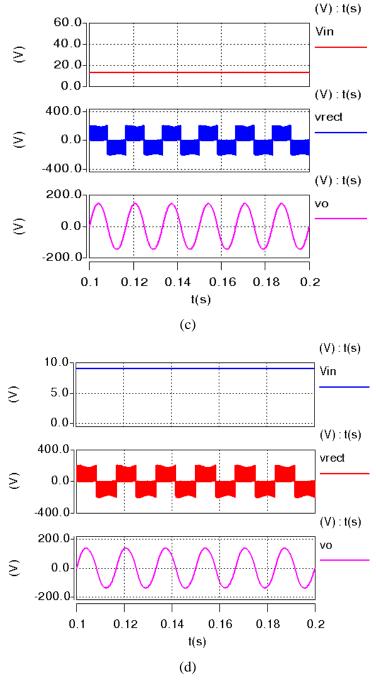

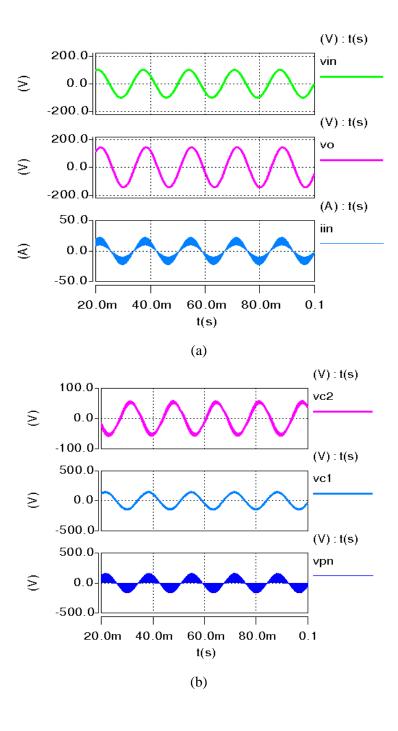

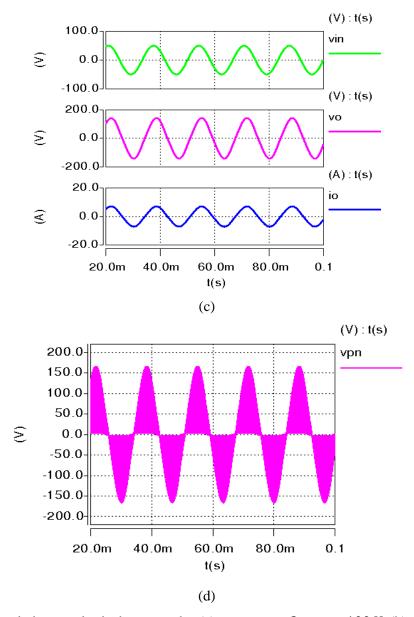

| Fig. 6.10    | Simulation results of configuration 1 circuit in boost mode126-127            |

| Fig. 6.11    | Simulation results of configuration 1 circuit in buck mode                    |

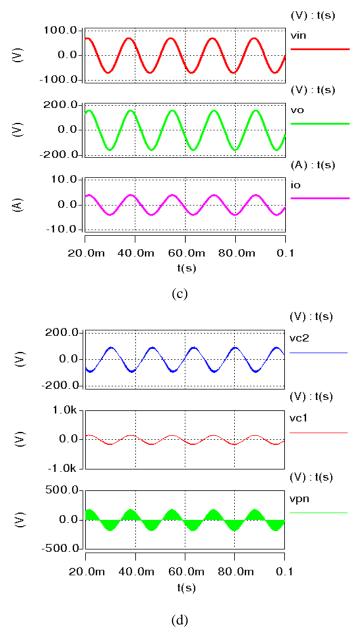

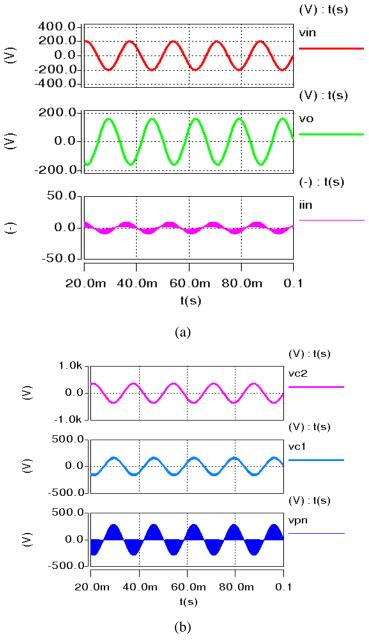

| Fig. 6.12    | Simulation results of configuration 2 circuit in boost mode130-131            |

| Fig. 6.13    | Simulation results of configuration 2 circuit in buck mode                    |

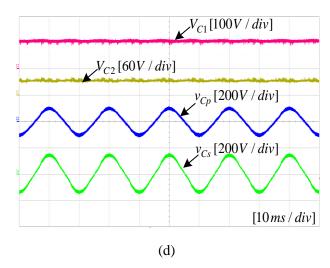

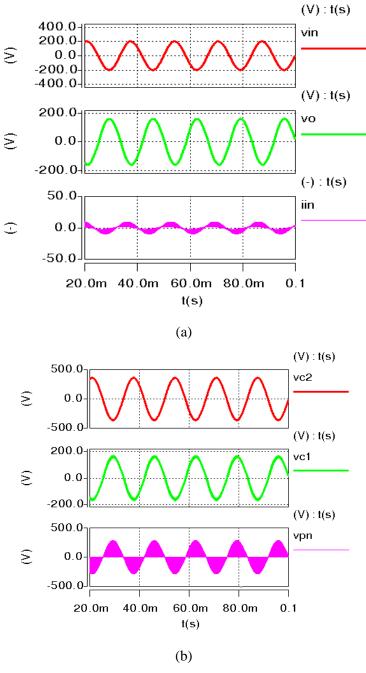

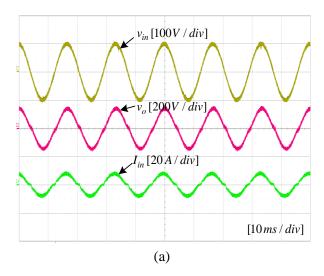

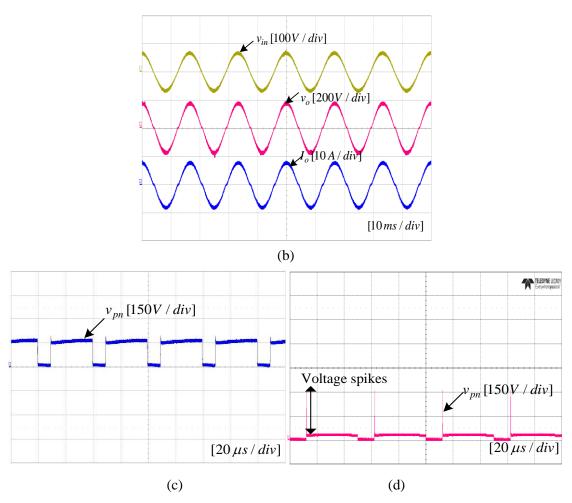

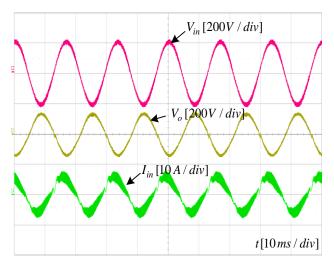

| Fig. 6.14    | Experimental results of configuration 2 circuit in boost mode133-134          |

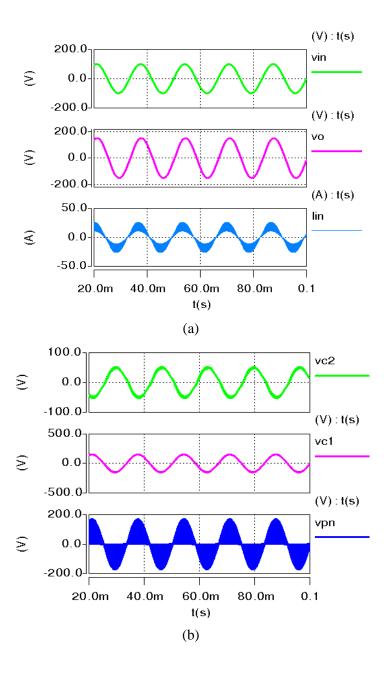

| Fig. 6.15    | Experimental results of configuration 2 circuit in buck mode                  |

| Fig. A.1     | Gate drive circuit                                                            |

| Fig. C.1     | PCB layout for the proposed isolated inverter                                 |

| Fig. D.1     | Saber simulation model of circuit configuration 1                             |

| Fig. D.2     | Saber simulation model of circuit configuration 2                             |

#### **Nomenclature**

Voltage Source Inverter VSI **CSI** Current Source Inverter **PVs** Photo-voltaic System **HEVs** Hybrid Electrical Vehicles **EMI** Electro-magnetic Interference ZSI Z-Source Inverter qZSI **Ouasi-Z-Source Inverter** M **Modulation Index STDC** Shoot-through Duty Cycle **THD Total Harmonic Distortion** В **Boost Factor** G Voltage Gain **PWM** Pulse Width Modulation Switched Inductor Z-source Inverter SL-ZSI SL-qZSI Switched Inductor Quasi-Z-source Inverter **CA-EBZSI** Capacitor Assisted Extended Boost Z-Source Inverter DA-EBZSI Diode Assisted Extended Boost Z-Source Inverter **LCCT Inductor Capacitor Capacitor Transformer DSP** Digital Signal Processor **HFT** High Frequency Transformer LC **Inductor Capacitor KVL** Kirchhoff's Voltage Law Volt-sec Voltage Second **IGBT Insulated Gate Bipolar Transistor** MC Magnetically Coupled **ZSAC Z-Source AC-AC Converter DVR** Dynamic Voltage Restorer

## **List of Symbols**

| $V_{in}$           | Input voltage                                      |

|--------------------|----------------------------------------------------|

| $v_o$              | Output voltage                                     |

| $v_{pn}$           | DC-link voltage                                    |

| $\widehat{v_{ph}}$ | Output peak phase voltage                          |

| $V_{sw}$           | Switch voltage stress                              |

| $V_{RMS}$          | Root mean square voltage                           |

| $v_a$              | Reference signal of phase A                        |

| $v_b$              | Reference signal of phase B                        |

| $v_c$              | Reference signal of phase C                        |

| $V_p$              | Upper envelop signal                               |

| $V_n$              | Lower envelop signal                               |

| $V_c$              | Voltage across capacitor                           |

| n                  | Turns ratio of the transformer (coupled inductor)  |

| $\Gamma$           | Gamma                                              |

| $T_1$              | Transformer 1                                      |

| $T_2$              | Transformer 2                                      |

| N                  | Number of inverters                                |

| kW                 | Kilo watt                                          |

| $v_L$              | Voltage across inductor                            |

| $v_{L_{sh}}$       | Voltage across inductor in shoot-through state     |

| $v_{L_{non}}$      | Voltage across inductor in non-shoot-through state |

| D                  | Duty cycle                                         |

| $V_D$              | Voltage across diode                               |

| $f_{sw}$           | Switching frequency                                |

| $L_o$              | Output inductor                                    |

| $C_o$              | Output capacitor                                   |

|                    |                                                    |

| $L_p$       | Primary inductance                |

|-------------|-----------------------------------|

| $L_s$       | Secondary inductance              |

| $L_{lkp}$   | Primary side leakage inductance   |

| $L_{lks}$   | Secondary side leakage inductance |

| $v_{ab}$    | Line-Line output voltage          |

| $i_o$       | Output current                    |

| $P_{fe}$    | Core loss                         |

| $P_{L\_cu}$ | Inductor copper loss              |

| $P_{T\_cu}$ | Transformer copper loss           |

| $K_{fe}$    | Proportionality constant          |

| $\Delta B$  | Flux density                      |

| $A_c$       | Cross sectional area              |

| $l_m$       | Mean core length                  |

| ho          | Resistivity                       |

| I           | RMS winding current               |

| $K_u$       | Winding fill factor               |

| $W_{A}$     | Core window area                  |

| $C_p$       | DC-blocking capacitor             |

| $C_s$       | Level shift capacitor             |

| S           | Switches                          |

| $v_{rec}$   | Rectified voltage                 |

| $v_{tri}$   | Triangular (carrier) wave         |

| $\Sigma$    | Sigma                             |

| $i_{a1}$    | Inductor current of inverter 1    |

| $i_{a2}$    | Inductor current of inverter 2    |

| $V_{saw}$   | Saw-tooth wave                    |

| $V_{ref}$   | Reference wave                    |

## 1. Chapter 1

#### Introduction

#### 1.1 Background

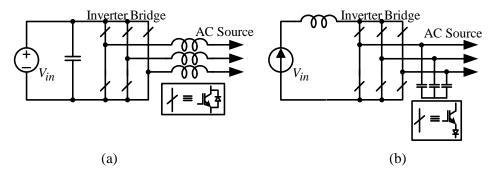

Traditionally there exist two types of power inverters for DC-AC conversion: voltage-source (VSI) and current-source (CSI) [1] as shown respectively in Fig. 1.1(a) and (b). Despite their huge demand in industrial applications, such as power distribution systems, photovoltaic (PV) systems and hybrid electric vehicles (HEVs), they suffer from some severe limitations [2-4] which makes them less preferable – some of the significant reasons for this, in terms of the using VSIs, are as follows:

- The obtainable output voltage is limited and cannot exceed the input DC voltage.

Therefore, VSI is a step-down (buck) inverter and requires an additional boost DC-DC converter where over-drive (high o/p voltage) is required.

- Another major concern with the traditional VSIs is the requirement of dead time between the switching components of the same leg of an inverter-bridge. The switches cannot be turned on concurrently either by purpose or electromagnetic interference (EMI). Otherwise it will short-circuit the input capacitor and high current spikes will cause severe damage to the switches

#### Similarly, in terms of using CSIs:

- The obtainable output voltage is always higher than the supplied input DC voltage.

Therefore, CSI is a step-up (boost) inverter and requires an additional buck dc-dc converter where reduced o/p voltage is required.

- CSIs requires an overlap between the switching components of the same leg of an

inverter-bridge. The switches cannot be turned off concurrently either by purpose or

electromagnetic interference (EMI). Otherwise it will open-circuit the input inductor

and high voltage spikes will cause severe damage to the switches. Therefore, an overlap time is always required for the safe commutation of inductor current.

Fig. 1.1 (a) Voltage source inverter (b) Current source inverter.

In addition both VSIs and CSIs have the common drawbacks such as they are either a buck or a boost power converter and thus requires additional dc-dc converter for a wide range of output voltage. This results in two stage power conversion and brings about additional switching losses and costs of the overall power system. Moreover, both have low reliability and are vulnerable to EMI noises resulting in poor output waveform qualities.

In order to address these issues, an impedance source inverter (ZSI) was proposed in 2002 [4] as shown in Fig 1.2. It efficiently utilizes the shorting (shoot-through) of the phase legs to boost the output voltage; it therefore provides single stage power conversion and has a better output waveform quality due to the elimination of dead time.

Fig. 1.2. Z-Source inverter

Nowadays ZSIs are widely employed in many applications, catering for all types of electric power conversion (AC-AC, AC-DC, DC-AC, DC-DC). However, these ZSIs have severe short comings that are discussed in the next section.

#### 1.2 Problem Statement

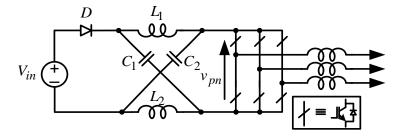

In PV generation systems, the voltage produced by a solar cell is very low (a single solar cell usually generates .5 volt). One way to increase the input voltage is the series connection of PV panels. However, this is not recommended practice because of the substandard power conversion efficiency and will reduce the lifetime of the PV panels [5]. To overcome this problem, modular systems have been proposed, such as the example shown in Fig 1.3(a) [6].

Fig. 1.3. PV systems (a) Two-stage power conversion (b) Single-stage power conversion

In these systems, an independent high step converter followed by conventional VSI was applied to the PV panel to increase the output voltage. However, due to the utilization of more switching devices and two stage power conversion, the cost and complexity of such a system increases. In order to replace these two stage power conversion systems with single stage power conversion, ZS inverters are utilized, as shown in Fig. 1.3(b). But the boost factor of these ZSIs needs to be enhanced in order to meet the desired output voltage while keeping in view the limitations of the components as well

Since the first publication of ZSI, many researchers have focused on developing new Z-source topologies with improved modulation schemes, boost capabilities, dynamics and control methods, and have introduced them in many diverse studies [7-45]. In [7] a family of quasi-Z-source inverters (qZSIs) were introduced, which have benefits over the ZSIs, such as sharing of common ground, improved input profiles and lower component voltage stresses. Despite these significant benefits and theoretical infinite voltage gains, all of these qZSIs suffer from one serious drawback: their practical boost abilities (B) are restricted due to higher component stresses and low output power quality, which is caused by the tradeoff between the modulation index (M) and the shoot-through duty cycle (D).

$$B = \frac{v_{pn}}{V_{in}} = \frac{1}{1 - 2D} \tag{1.1}$$

$$M = 1 - D \tag{1.2}$$

Equation (1) shows the relationship between the boost factor and the shoot-through duty cycle of the ZSI for a given value of input voltage. From (2), it can be inferred that the duty cycle and modulation index are interdependent, i.e. to achieve a higher boost factor, shoot-through duty cycle has to be increased which in turns consequently decreases the modulation index. Reduced modulation index results in lowering the quality of the output power, reduced power factor as it gives significant rise to total harmonic distortion (THD) while decreasing the AC output voltage fundamental component [8]. Furthermore, with the utilization of higher D and lower M, leads to higher voltage stresses across the passive (inductors, capacitors, diodes etc) and switching devices due to poor usage of dclink voltage.

Therefore, transformer based ZSIs were proposed [9-17]. They employs a transformer (coupled inductor) in the impedance network and utilizes its turns ratio to increase the boost factor while keeping the duty cycle lower. However, with the use of higher secondary windings isolation between the windings is increased which causes the leakage inductance to increase manifolds. Huge voltage spikes occurs across the switching devices and switching losses becomes more prominent, therefore addition of extra clamping circuits are required. Moreover, with higher turns ratio and increased secondary windings

the size of the magnetic component becomes significantly higher resulting in bulky and oversized power system.

Another major concern among ZSIs is that the typical existing circuits do not use any electrical isolation. Therefore, when these ZSIs are used in photo-voltaic modules as grid inverters, a DC current is injected in the grid which may cause saturation of the distribution transformer [46, 47] as well as poor power quality, higher loss, and overheating of the power system. According to IEEE Standard 1547-2003, the level of DC component injected into grid should be less than 0.5% of the rated output current [48-50]. In order to avoid this injection of DC current into the grid, and to fulfil safety standards, the conventional approach is to incorporate a line frequency transformer between the inverter and the grid. However, this low frequency transformer is bulky, heavy, expensive, and decreases the efficiency and power density of the system. Many other methods have also been developed to minimize the injection of DC currents into the grid within transformer-less inverters (e.g. existing ZSIs). Most of these methods for blocking DC currents include a DC capacitor [50], voltage and current detection-based techniques. However, they either use bulky and expensive capacitors, or voltage and current sensing circuitry, yet may not guarantee the safety standards are met.

These are the challenges needed to be addressed and overcome in developing a reliable, and minimal loss power converter system that will have an overall improved spectral performance compared to existing ZSI circuits.

#### 1.3 Aim and Sub-objectives

The overarching aim of this thesis is the improvement in variety of aspects of impedance source inverters and converters. This includes the output gain of the inverter, total cost of the system, complexity of the system, dynamic response of the inverter. Additionally, modulation strategies will be modified to effectively control the proposed inverter system. From this aim, the following research objectives were established for this work:

- 1. Develop understanding about the operating principles and features of impedance source inverters and converters.

- 2. Advancement in the circuitry of impedance source inverters (DC-AC) which results in improved voltage gains, less complexity and cost-efficient systems.

- 3. Implementation of high frequency electrical isolations resulting in protection, safety and avoids the injection of circulating currents into the grid with the utilization of higher modulation index.

- 4. Modifications in the modulation strategies for the advanced impedance source inverters resulting in simpler control.

- 5. Implementation of parallelising multiple inverters to the class of impedance source inverters which in turns results in increased output voltage, reduced component stress by sharing the currents, ease of maintenance, modularity facilitating plug and play, higher reliability, and (N+1) redundancy. Moreover, by parallel operation of inverters, output ripples can be reduced by utilizing interleaving mechanism, which will reduce the requirements for output filters.

- 6. Development of new class of transformer based impedance source AC-AC converters with novel control strategies to increase the voltage gains and to improve conglomerate characteristics of the converters.

- 7. Design and development of hardware laboratory prototypes of proposed structures to validate their advantages and benefits over existing topologies and improve their overall efficiencies.

All of the proposed structures will be comprehensively discussed with brief analysis and theoretical derivations will be done that would be the major focal point of this thesis. Saber models will be presented and simulations will be performed to verify their working principles. Comparisons with existing topologies will be made to show efficiency improvements of the proposed power converters. At the end, hardware prototypes are built to validate their advantages that is the second major task of the thesis project.

#### 1.4 Research Questions

The main idea of the proposed Z-source inverters is to overcome the drawbacks faced with the existing topologies such as leakage inductance problem, complex structure, low gain, low modulation index value, and high stress issue. Thus, to confirm the benefits claimed, efficiency plots are highly important.

The research questions to be answered in this thesis are:

- 1. How should the power losses and efficiencies be calculated?

- 2. What methods to applied for improving the voltage gain of the proposed inverters?

- 3. How will the voltage clamping technique be applied to the proposed inverters?

- 4. How should the dc circulating current be controlled in isolated impedance source inverters?

- 5. What control methods are applicable for the proposed isolated structures?

- 6. How to implement the interleaving mechanism in the existing modulation strategies of parallel operated impedance source inverters?

A more detailed description of these research questions are discussed in the proposed design plan and the procedures that are taken into account to achieve the required results.

#### 1.5 Methodology

The methodology focuses on planning the research steps followed for the modelling and design of an improved impedance source inverters and the implementation of electrical isolations and parallelization of ZSIs. It will also consider the measurement methods which are to be used for the analysis and process results with simulation modellings and the design of the experimental setup that is required for the physical testing.

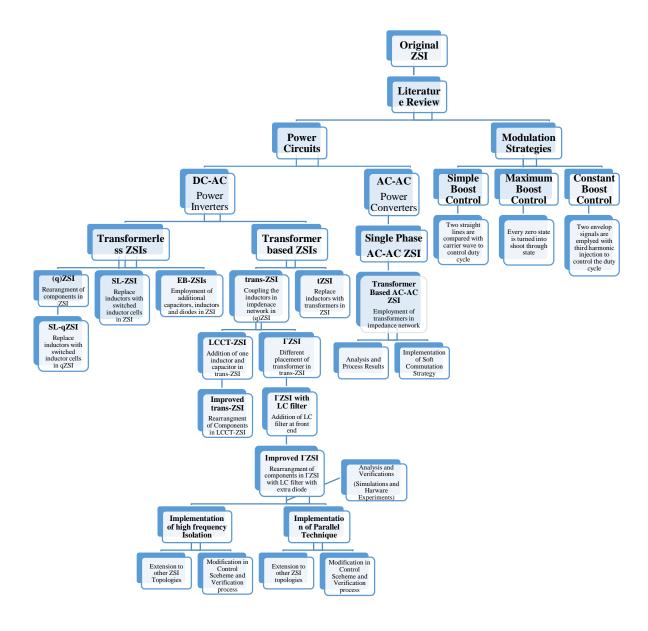

#### 1.5.1 Literature Review

The literature review will focus on studying impedance source inverters and their control techniques. This part of the project is discussed in much detail in Chapter 2 and it will investigate the operating principles and their working in a very comprehensive

manner and identify their significant features and contributions to the field of power electronics with their pros and cons and the motivation behind the thesis project.

#### 1.5.2 Research Plan

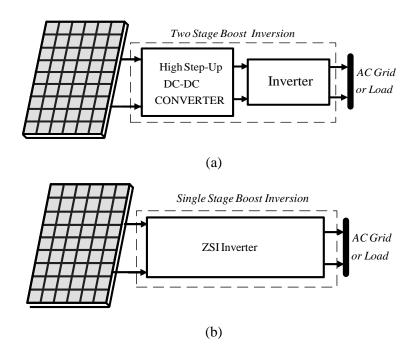

This research project is designed around the sequence of multiple steps as illustrated in Fig. 1.4 below. The figure provides detail of the research process in the form of a flow chart which will be carried out to achieve the research goals as described in Section 1.3. The flow chart shows the step by step approach to achieve the final goal of this thesis and the major phases of the project. It includes the measurement methods and techniques that will be used for the complete analysis and verifications of the impedance source inverters.

The major part of research plan consists of four significant contributions of the project. Initially, the research plan is to survey in detail the main Z-source topology, its features, applications and modulation (control) strategies followed up by comprehensive study of DC-AC, AC-AC Z-source power circuits. Afterwards, step by step approach for the derivation of improved  $\Gamma$ ZSI with clamping diode, implementation of HFT, parallelization of  $\Gamma$ ZSI and other ZSIs, and transformer based AC-AC ZSIs with brief analysis including detail testing will be carried out.

Fig. 1.4. Flow Chart of the Planned Research Process

#### 1.6 Research Outputs

This section lists the articles have been published from this thesis project, including those which are in press and anticipated to be published shortly. Refereed conference are

- indicated by the "(C)" numbers, and peer-reviewed journal are indicated by the "(J)" numbers. The outputs are as follows:

- C1. Z. Aleem, and M. Hanif, "Improved  $\Gamma$ -Z-Source Inverter," in *IEEE Energy Conversion Congress and Exposition*, Sep. 2016, pp. 1-5.

- **C2.** Z. Aleem, and M. Hanif, "A Class of Parallel Operated Impedance Source Inverters," in *IEEE Annual Southern Power Electronics Conference*, Dec. 2016, pp. 1-6.

- **C3.** Z. Aleem, and M. Hanif, "Single-Phase Transformers Based Z-Source AC-AC Converters," in *IEEE Annual Southern Power Electronics Conference*, Dec. 2016, pp. 1-6. (Received Paper Award).

- **C4.** Z. Aleem, S. Winberg, A. Iqbal and M. Al-Hitmi, "High Frequency Transformer Based Improved Gamma ZSI with Lossless Snubber," *IECON 2018 44th Annual Conference of the IEEE Industrial Electronics Society*, Washington, DC, 2018, pp. 3731-3736.

- **C5.** Z. Aleem, and M. Hanif, "Current-Fed Converters with Switching Cells," in *IEEE Energy Conversion Congress and Exposition*, Sep. 2016, pp. 1-7.

- **J1.** Z. Aleem and M. Hanif, "Operational Analysis of Improved  $\Gamma$ -Z-Source Inverter With Clamping Diode and Its Comparative Evaluation," in *IEEE Transactions on Industrial Electronics*, vol. 64, no. 12, pp. 9191-9200, Dec. 2017.

- **J2.** Z. Aleem, S. Winberg, A. Iqbal, M. A. Al-Hitmi and M. Hanif, "Single-Phase Transformer based HF-Isolated Z- Source Inverters with Voltage Clamping Techniques for Solar PV Applications," in *IEEE Transactions on Industrial Electronics*. doi: 10.1109/TIE.2018.2889615

- **J3.** Z. Aleem, S. Winberg, and H. F. Ahmad "A Class of Single-Phase Z-Source AC-AC Converters Based on Transformers with Safe-Commutation Strategy", (Submitted in IEEE transactions on Industrial Informatics).

#### 1.7 Organisation and Scientific Contributions of the Thesis

This research project contributed an overall approach to the modelling and development of advanced impedance source inverters with high frequency isolation technique and parallel connected inverter operations. Accordingly, this approach has involved tasks of reviewing relevant studies from the literatures, surveying industry standards, trends and practical implementation of these topologies in a specific and controllable manner. The chapters in this thesis are arranged according to the modelling techniques and methods used to propose and analyse designs, rather than following the historical progression of how this investigation proceeded.

Chapter 2 presents the literature overview of the Z-source power control topologies and their modulation strategies are discussed. The merits and demerits of these topologies are identified. It concludes by justifying the proposition of improved ZSIs with HFTs and parallel connection of ZSIs in this thesis.

In Chapter 3, the improved  $\Gamma$ ZSI with voltage clamping technique is proposed and detailed analysis is presented. Its comparative evaluations with the existing topologies are also discussed and verified its advantages over existing inverters through simulations. Efficiency plots are also given and in the end a hardware prototype is fabricated and experimental studies are investigated.

Chapter 4 the use of high frequency transformer is discussed and implemented. Its advantages in terms of protection and safety are elaborated. Then this HFT technique is applied to all existing ZSI topologies and their theoretical and virtual analysis are shown. New modulation method for the control of HFT-ZSIs is also proposed and voltage clamping diodes are implemented. In the end of this chapter an experimental setup of HFT-improved  $\Gamma$ ZSI is prepared and experiments are performed.

Parallel operation of improved ZSI with magnetic coupling is proposed and presented in Chapter 5 to increase the power of the system up to several KWs. This concept is extended to other ZSI topologies and extensive simulations are performed. Interleaving mechanism is used to lower the output filter requirements. A hardware prototype is fabricated based on DSP Kit TMS320f28335 for the control of switching devices. The

interleaving method is implemented through DSP programming by phase shifting the switches of inverter bridge 2 by 180°.

Chapter 6 focuses on the development of new class of transformer-based impedance source AC-AC converters. The proposed converters provides a wide range of step up and step down functions with maintaining or reversing the phase angle. It can produce a higher boost factor than existing Z-source AC-AC converters with continuous input currents and improved input profiles. A soft commutation strategy is also discussed. The operation of the proposed converters is validated mathematically, virtually through simulations and through experimental hardware prototypes and results.

Finally, Chapter 7 concludes this thesis by summarizing the main findings and presenting significant observations. The last section provides recommendations for future research.

### 2. Chapter 2

# Review of the Z-Source Converter Topologies and their Modulation Strategies

Various converter topologies have been developed, according to recent literature, to overcome the limitations and problems of the traditional voltage source, classical buck/boost, unidirectional, and bidirectional converter topologies [51-55]. Proper implementation of the impedance-source network (ZSI) with appropriate switching configurations and topologies reduces the number of power conversion stages in the system power chain, which may improve the reliability and performance of the power system.

#### 2.1 Z-Source Inverter (ZSI)

The basic impedance-source network can be generalized as a two-port network with a combination of two basic linear energy storage elements, i.e., L and C (dissipative components (R) are generally omitted). However, different configurations of the network are possible to improve the performance of the circuit by adding different nonlinear elements into the impedance network, e.g., diodes, switches, and/or a combination of both.

A three-phase voltage-fed ZSI, as shown in Fig. 2.1, is used as an example to briefly illustrate the operating principle as described previously. The three-phase ZSI bridge has nine permissible switching states (six active states, two zero states, and one shoot-through state) shown in Fig. 2.1 unlike the traditional three-phase VSI which has eight (six active states, two zero states) [1].

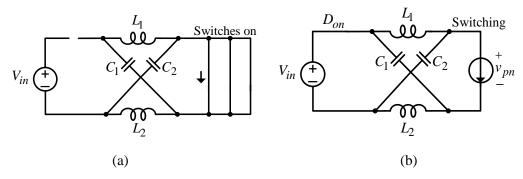

Fig. 2.1. Operation modes (a) Shoot-through state (b) Non-shoot-through state

During zero states, the upper three or lower three switches of the inverter bridge are turned on simultaneously, thus shorting the output terminals of the inverter and producing zero voltage across the load. During one of the six active states, the DC voltage is impressed across the load, positively or negatively. However, during shoot-through states, the load terminals are shorted through both the upper and lower devices of any one-phase leg, any two phase legs, and all three-phase legs producing zero voltage across the load. This shoot-through state has the same effect, i.e., producing zero voltage across the load as the traditional zero states; however, these shoot-through states can boost the output voltage. The shoot-through state is forbidden in the traditional VSI, because it would cause a short circuit across the dc link and damage the inverter. The Z-source network and the shoot-through zero state provide a unique buck-boost capability for the inverter by varying the shoot-through time period and modulation index M of the inverter. Theoretically, the output voltage of the inverter  $(\widehat{v_{ph}} = MB/2 = M[1 - 2D_{sh}]^{-1}V_{in}/2)$  can be set to any value between 0 and  $\infty$ . However, some practical aspects and performance of the converter need to be considered for large voltage buck or boost operation, (as discussed in section 1) e.g., to avoid exceeding device limitations.

## 2.2 Pulse Width Modulation Strategies for Z-Source Inverters

Many PWM methods have been developed for the control of three phase voltagesource inverters. Traditionally voltage-source inverters have eight switching states, six active states in which energy is transferred to load, and two zero states in which either the upper switches or lower switches of all the legs are switched off and thus the output voltage to the load is zero.

The ZSI has an additional zero state, which is forbidden in the voltage-source inverters. Insertion of this zero-state became the focal point of these control schemes. Three different PWM schemes are proposed in [21-24] are discussed in the next section.

#### 2.2.1 Simple Boost Control

As in (2.1) the gain of the Z-source inverter is expressed as

$$B = \frac{1}{1 - 2D} \tag{2.1}$$

$$\widehat{v_{ph}} = MB^{V_{in}}/2 \tag{2.2}$$

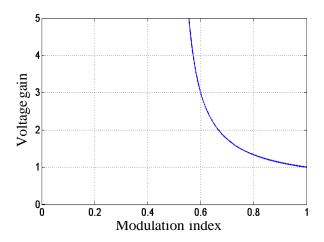

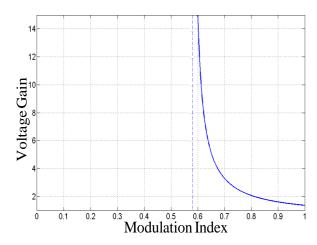

Where, D is the shoot-through duty of the switches, which is defined in (1.2) as M = 1 - D. It can be seen that the modulation index and shoot-through duty are interdependent. Fig. 2.2 illustrates the simple boost control scheme for Z-source inverter [4, 24]. It employs a straight line equal to or greater than the peak value of three phase references to control the duty ratio. In simple boost control, the modulation index decreases significantly with the increase in shoot-through duty. In order to have a large boost gain, a smaller modulation index has to be used which results in high voltage stress on the inverter bridge. For any desired voltage gain the maximum modulation index can be achieved is

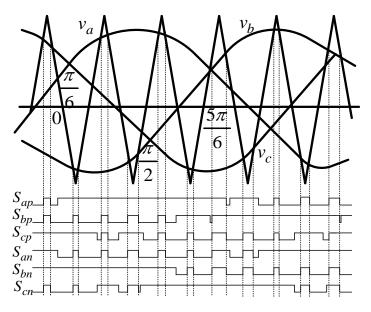

Fig. 2.2 Simple boost control

$$M = \frac{G}{2G - 1} \tag{2.3}$$

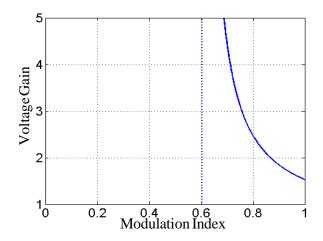

Whereas G is the gain of the inverter. Fig 2.3 shows the plot curve of modulation index versus the voltage gain of the inverter with simple boost control. The voltage stress  $V_s$  across the switches are as follows

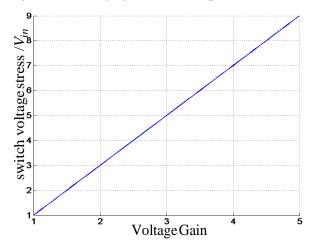

$$V_{sw} = BV_o(2G - 1)V_o (2.4)$$

From this equation, it can be inferred that in simple boost control the voltage stress across the switches is quite high which will restrict the voltage gain because of the limitation of device voltage rating. The curve of switches voltage stress versus the voltage gain is plotted in Fig. 2.4.

Figure 2.3 Voltage gain of the simple boost control

Figure 2.4 Switch voltage stress versus the voltage gain

#### 2.2.2 Maximum Boost Control

In simple boost control, the obtainable shoot-through duty decreases with the increase in modulation index as given by (1.2). Moreover, from Fig. 2.4 it can be inferred that switch voltage stress is quite high which restricts the achievable voltage gain of the inverter due to the limitation of the device voltage rating.

Reducing the voltage stress while keeping gain higher becomes important for the control of Z-source inverter. To attain this objective, the shoot-through duty should be as large as possible with enough modulation index to minimize the voltage stress across the switches. Fig. 2.5 shows the strategy of maximum boost control [21].

Fig. 2.5 Maximum boost control

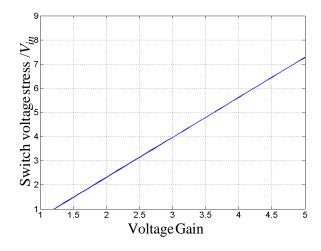

It is similar to the traditional carrier-based PWM scheme. It maintains all the active states unchanged and turn all the zero states into shoot-through states, thus maximum boost factor is achieved for any given modulation index. From Fig. 2.5, the circuit is in shoot-through state whenever the triangular carrier wave is either greater than or lower than the reference sinusoidal waveforms. The shoot-through duty in maximum boost control varies each cycle and this zero state repeats periodically every  $\frac{\pi}{3}$ . Thus the voltage gain can be expressed as:

$$G = MB = \frac{\pi M}{3\sqrt{3}M - \pi} \tag{2.5}$$

The curve of voltage gain versus modulation index is shown in Fig. 2.6. As can be seen output voltage increases when M decreases and reaches to infinity when M approaches to  $\frac{\pi}{3\sqrt{3}}$ . On the other hand a higher modulation index for any voltage gain results in lower voltage stress. Thus the voltage stress is given by

$$V_{sw} = BV_{in} = \frac{3\sqrt{3}G - \pi}{\pi}V_{in}$$

(2.6)

The voltage stress versus the voltage gain curve is shown in Fig 2.7. Compared to simple boost control the voltage stress across the switches in maximum boost control is much lower. With maximum boost PWM scheme the inverter can be operated to achieve a higher voltage gain for given active devices.

Fig. 2.6 Voltage gain of the maximum boost control

Fig. 2.7. Switch voltage stress versus the voltage gain

#### 2.2.3 Maximum Constant Boost Control

As compared to simple boost control the voltage stress across the switches in maximum boost control is much lower as it turns all the zero states into shoot-through states. However, this control scheme has a serious drawback, the shoot-through duty cycle is not constant in this method which introduces a low-frequency current ripple that is associated with the output frequency of the inductor current and capacitor voltage. This

ripple increases the requirements of passive components when the output frequency is very low which in turns effects the overall efficiency of the system in terms of cost and size. In order to address this problem, constant shoot-through duty is needed to eliminate this low output frequency ripple. Consequently, a greater modulation index with high enough duty cycle is required to achieve both lower voltage stress and high gain of the inverter. In 2006 [22], maximum constant boost control scheme was proposed. Fig. 2.8 shows the sketch map of this control scheme.

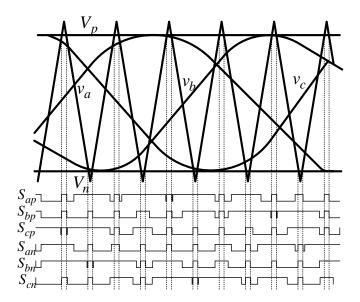

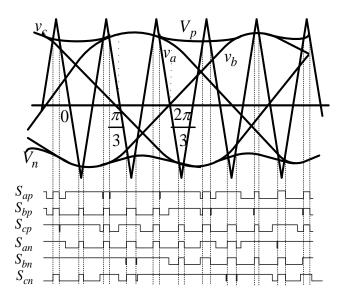

Fig. 2.8 Maximum constant boost control

As can be seen from the Fig, there are five modulation curves in this scheme, three reference signals  $v_a$ ,  $v_b$ , and  $v_c$ , and two shoot-through envelop signals  $V_p$ , and  $V_n$ . When the carrier wave is greater than or lower than these envelop signals the inverter is turned into shoot-through states. The shoot-through duty must be kept same from switching cycle to switching cycle to have a constant boost. The voltage gain is expressed as follows

$$G = MB = \frac{M}{\sqrt{3}M - 1} \tag{2.7}$$

Fig. 2.9 shows the curve of voltage gain versus modulation index, as it is shown voltage gain approaches to infinity when M decreases to  $\frac{\sqrt{3}}{3}$ .

Fig. 2.9 Voltage gain of the constant boost control

Similarly, all the PWM schemes can be implemented using third harmonic injection. Third harmonic injection is usually used in three phase inverter systems to increase the modulation index range. It can be utilized here to increase the modulation index range which would result in increased voltage gain range.

#### **2.2.4 Summary**

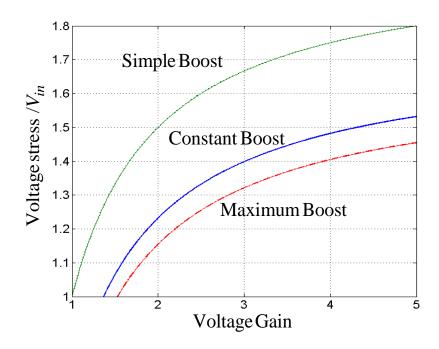

Three control methods: Simple boost control, maximum boost control and constant boost control were presented in this chapter. The ratios of the voltage stress to the equivalent input DC voltage of simple, maximum and constant boost control are summarized as:

$$\frac{V_s}{GV_{in}} = 2 - \frac{1}{G}$$

for simple control (2.8)

$$\frac{V_s}{GV_{in}} = \frac{3\sqrt{3}G - \pi}{\pi} \qquad \text{for maximum control}$$

(2.9)

$$\frac{V_s}{GV_{in}} = \sqrt{3} - \frac{1}{G}$$

for constant control (2.10)

Fig. 2.10 shows the voltage stress ratios of the three modulation schemes. From Fig. it can be inferred that the constant boost control has a much lower voltage stress across the switches than simple boost control but have a slightly higher stress than maximum boost control.

Fig. 2.10 Voltage stress comparison

#### 2.3 Transformer-less ZSIs

This section will provide a brief overview of the existing ZSIs, reviewing in particular the following approaches: the quasi(q)-ZSI [7], extended boost ZSIs [20] (capacitor assisted, diode assisted), switched inductor(SL)-ZSI [8], SL-qZSI [28], trans-ZSI [9], LCCT-ZSI [10], improved trans-ZSI [11], TZSI [12], and gamma( $\Gamma$ )-ZSI [14] together with a discussion of their pros and cons.

#### 2.3.1 Quasi-ZSI (qZSI)

QZSI is derived by rearranging the components in original ZSI circuit. Fig. 2.11 shows the basic structure of how qZSI is implemented [7]. As can be seen from the Fig. 1.2, the capacitor  $C_2$  and input voltage share the common ground. Therefore, C2 can be moved to top side and then the voltage across  $C_2$  is reduced from  $V_{c2}$  to  $(V_{c2} - V_{in})$  in the new configuration. Once this alteration is made,  $L_1$  is connected in series with  $V_{in}$ . Rearranging the circuit leads to the qZSI shown in Fig. 2.11.

Fig. 2.11. Quasi-Z-source inverter

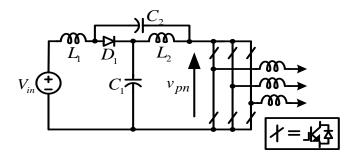

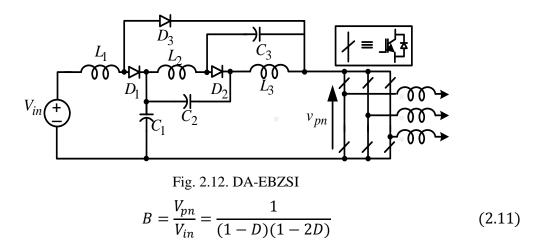

#### 2.3.2 Diode-Assisted Extended-Boost ZSI (DA-EBZSI)

To overcome the gain limitation as discussed earlier without further reducing the modulation index extended boost ZSIs were proposed [20]. Fig. 2.12 shows the basic topology of extended boost diode-assisted ZSI. This topology adds additional two diodes, one inductor, and one capacitor in the Z-source topology to have higher gain than original ZSI.

Equation (2.11) shows the boost factor of the extended boost diode assisted ZSI which is higher than the original ZSI at the expense of more diodes, inductors and capacitors which increases the cost and complexity of the overall system.

#### 2.3.3 Capacitor-Assisted Extended-Boost ZSI (CA-EBZSI)

Fig. 2.13 shows the basic topology of extended boost capacitor assisted ZSI. As compared to the previous topology this structure adds additional two capacitors, one

inductor, and one diode (as the name suggests) in the Z-source topology to have slightly higher gain than DA-EBZSI.

Fig. 2.13. CA-EBZSI

$$B = \frac{V_{pn}}{V_{in}} = \frac{1}{1 - 3D} \tag{2.12}$$

Similarly, CA-EBZSI have more capacitors instead of diodes in the impedance network compared to DA-EBZSI. But both of these circuits have large no. of components only to increase the boost factor of the inverter circuit.

#### 2.3.4 Switched Inductor ZSI (SL-ZSI)

The SL-ZSI is shown in Fig. 2.14, which is obtained by replacing the two inductors  $L_1$  and  $L_2$  in the classical ZSI with SLs [8], each of which consists of two inductors and three diodes. By adding six additional diodes and two inductors, it obtains a boost factor of (1+D)/(1-3D), which is much larger than that of the classical (q)ZSIs.

Fig. 2.14. SL-ZSI

#### 2.3.5 Switched Inductor qZSI (SL-qZSI)

Due to the drawbacks faced by SL-ZSI, such as huge inrush current, discontinuous input current, absence of common ground between input voltage and inverter bridge and large number of components, switched inductor quasi Z-source inverter was proposed [28] shown in Fig. 2.15.

Fig. 2.15. SL-qZSI

The SL-qZSI inverter is obtained by replacing inductor  $L_2$  in the classical qZSI with the same SL as that used in the SL-ZSI. Compared to the SL-ZSI, it has continuous input current, common ground between the dc-voltage source and the inverter-bridge, and has no startup inrush current. Nevertheless, its boost ability is  $(1 - D)/(1 - 2D - D^2)$ , which is significantly lower than that of the SL-ZSI, and, hence, dilutes its other advantages over SL-ZSI.

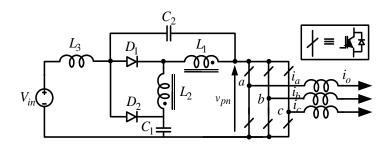

#### 2.4 Transformer Based ZSIs

Despite having higher gains, the boost capability remains limited, and its further enhancement requires the use of multiple extensions of the same components, which increases the volume and cost of the inverters and effects of the parasitic components become more severe. To overcome these issues, transformer based impedance source inverters are proposed [9-17] to achieve high voltage gains by keeping the component count as low as possible. These inverters induce a coupled inductor in the Z-source network and utilize the turns ratio of the magnetic component to increase the voltage gain of the inverters. This section reviews the different transformer based ZSI topologies presented in literature.

#### 2.4.1 Trans-ZSIs

The trans-Z-source [9] inverter induces a coupled inductor in the impedance network and the voltage of inductor  $L_1$  is reflected to inductor  $L_2$  through magnetic coupling, therefore capacitor  $C_2$  can be removed from the impedance network. The boost factor B (ratio of dc-link  $v_{pn}$  to input voltage) of the trans-Z-source inverter is defined as

$$B = \frac{V_{pn}}{V_{in}} = \frac{1}{1 - (1+n)D} \tag{2.13}$$

where, *n* is the turns ratio of the coupled inductor and can be adjusted according to the desired output value. Fig. 2.16 shows the basic structure of trans-ZSI.

Fig. 2.16. Trans-ZSI

#### 2.4.2 LCCT-ZSI

Fig. 2.17 shows an inductor-capacitor-capacitor transformer (LCCT) ZSI [10] which adds one additional inductor and capacitor to offer some benefits over the trans-Z-source inverter such as continuous input profiles and reduced inrush current at startup. However, these benefits are attained at the expense of more components while retaining the same voltage gain and other features of trans-ZSI.

Fig. 2.17. LCCT-ZSI

#### 2.4.3 Improved trans-ZSI

In, [11], improved trans-ZSI was proposed as shown in Fig. 2.18. The improved trans-ZSI overcomes the issues of trans-ZSI which are discontinuous input current, inrush current at startup and unlike LCCT-ZSI, the improved trans-ZSI also provides higher voltage gain compared to LCCT and trans-ZSI. The boost factor is as follows

Fig. 2.18. Improved trans-ZSI

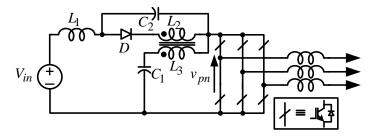

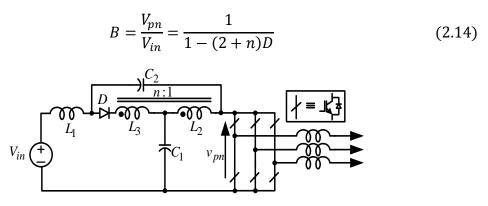

#### **2.4.4 TZSIs**

Similarly, in 2013 a new family of TZ-source inverters was proposed [12] as shown in Fig. 2.19. These inverters replace the inductors with the transformers ( $T_1$  and  $T_2$ ) to achieve a higher gain than conventional trans-Z-source and improved trans-Z-source inverters. The boost ability of the TZSI is expressed as

where,  $n_1$  is the turns ratio of  $T_1$  and  $n_2$  is the turns ratio of  $T_2$ . The voltage gain of the inverter is adjusted by varying the turns ratio of the transformers. Even with a turns ratio of 1 ( $n_1 = n_2 = 1$ ) the TZSIs produces higher gain than the trans-ZSIs.

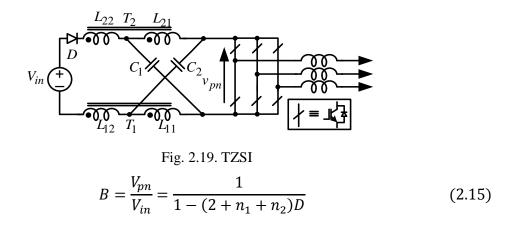

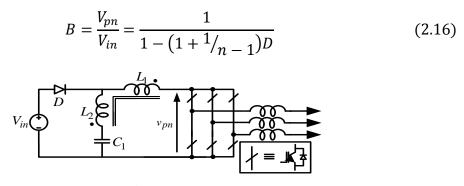

#### 2.4.5 Γ-Z-Source Inverter (ΓΖSI)

The  $\Gamma$ ZSI shown in Fig. 2.20 boosts the output voltage by lowering the turns ratio of the transformer rather than increasing it. As compared to other transformer based impedance source topologies, the  $\Gamma$ ZSI [14] uses the same or less number of components for producing higher voltage gain while utilizing a higher modulation index and consequently a lower shoot-through duty ratio. Moreover, the output voltage of the  $\Gamma$ ZSI is adjusted by varying the turns ratio of the magnetic component within a narrow range of  $1 < n \le 2$ . This leads to lesser winding turns and confined transformer size to achieve higher gain which makes it more preferable in the industrial applications. The boost ability of the inverter is expressed as:

Fig. 2.20. ΓZSI

Although the inverters discussed earlier are attractive and have several significant features, the transformer turns ratio might become too high for obtaining high voltage gain which leads to oversized and bulky transformers. Additionally, there are several short comings associated with these inverters, e.g. discontinuous input currents, huge inrush current at startup in the case of trans-ZSI, TZSI, and ΓZSI thus requiring additional LC filter at the front end [33], absent common ground b/w input and inverter bridge in TZSI, addition of more components in TZSI, improved trans-ZSI, LCCT ZSI resulting in increased cost of the overall system. In all other transformer based Z-source topologies, to get higher boost larger turns ratios are needed, which requires more isolation between

the windings, which will in turn cause the leakage inductance to increase manifolds. This leakage inductance is directly in series with inverter-bridge without any snubber circuit in between and, therefore, large di / dt caused by the switching of the windings currents results in large switch-voltage spikes. In this thesis, new structures for the ZSIs are discussed to improve several features of the impedance source topology including voltage gains and then voltage clamping technique is implemented to overcome the voltage overshoots. These proposed structures of ZSIs can utilize higher modulation index and thus have improved output power quality and efficiencies. High frequency electrical isolations and parallel operating methods are also implemented which can provide more safety and protection in terms of meeting IEEE safety standards by providing galvanic isolation, redundancy and modularity.

Table 2.1 summarizes the features of different transformer based ZSIs discussed earlier.

**TABLE 2.1**

|                                          | Trans-ZSI                                                | LCCT-ZSI             | Improved trans-ZSI                                   | TZSI                                                           | ΓZSI                                                 | ΓΖSI with LC                         |

|------------------------------------------|----------------------------------------------------------|----------------------|------------------------------------------------------|----------------------------------------------------------------|------------------------------------------------------|--------------------------------------|

| Boost Factor                             | $\frac{1}{1-(1+n)D}$                                     | $\frac{1}{1-(1+n)D}$ | $\frac{1}{1-(2+n)D}$                                 | $\frac{1}{1 - (2 + n_1 + n_2)D}$                               | $\frac{1}{1 - (1 + \frac{1}{n-1})D}$                 | $\frac{1}{1 - (1 + \frac{1}{n-1})D}$ |

| Components<br>in<br>impedance<br>network | 3                                                        | 5                    | 5                                                    | 5                                                              | 3                                                    | 5                                    |

| Gain                                     | Higher<br>than ZSI<br>with<br>increase in<br>turns ratio | Same as<br>trans-ZSI | Higher than<br>trans-ZSI<br>with same<br>turns ratio | Higher than<br>improved trans-<br>ZSI with same<br>turns ratio | Gain is increased<br>by decreasing the<br>turn ratio | Same as ΓZSI                         |

| Input current                            | Discontinu<br>ous                                        | Continuous           | Continuous                                           | Discontinuous                                                  | Discontinuous Cor                                    |                                      |

| Inrush<br>current                        | High                                                     | Low                  | Low                                                  | High                                                           | High                                                 | Low                                  |

| Share<br>ground                          | Yes                                                      | Yes                  | Yes                                                  | No                                                             | Yes                                                  | Yes                                  |

| Leakage<br>inductance<br>problem         | Yes                                                      | Yes                  | Yes                                                  | Yes                                                            | Yes                                                  | Yes                                  |

## 3. Chapter 3

# Improved FZSI with Clamping

### **Diode**

#### 3.1 Introduction

The  $\Gamma$ -Z-source inverter shown earlier in Fig. 2.20 boosts the output voltage by lowering the turns ratio of the transformer rather than increasing it resulting in small transformer size and lower cost making it more preferable as compared to other transformer based ZSI topologies. However, despite having these features, the  $\Gamma$ -Z-source inverter suffers from several serious drawbacks:

- 1. The input current is discontinuous, thus requiring an additional LC filter at the front end of the  $\Gamma$ -Z-source inverter as shown in Fig 3.1 [33], to eliminate the discontinuity of the input current and protect the energy source.

- 2. There is huge inrush current at startup and the resulting voltage and current spikes can damage the devices. It appears due to large resonant current flowing in to the input diode, transformer windings, capacitor, and body diodes of the IGBTs.

- 3. The Γ-Z-source inverter uses the same number of components as of trans-ZSI but with a different transformer placement. This difference in dot polarities of the magnetic component causes the capacitor C1 current to bypass, which is very high. This leads in the increment of current ratings and cost of the switching devices.

- 4. The leakage inductance of the transformer is utilized to minimize the current of capacitor C1, however the leakage inductance is in series with the inverter bridge without any snubber circuit causing large voltage spikes due to the switching of the winding currents.

Fig. 3.1. ΓZSI with LC filter

To resolve these severe shortcomings and improving the reliability of the power system, this chapter proposes and analyses the improved  $\Gamma$ -Z-source inverter that enhances upon the conventional  $\Gamma$ -Z-source inverter to overcome the aforementioned drawbacks of existing topologies. Fig. 3.2 shows the basic structure of the improved  $\Gamma$ -Z-source inverter with clamping diode  $D_2$ .

Fig. 3.2. Improved  $\Gamma$ ZSI with clamping diode

This chapter shows the step by step derivation of improved  $\Gamma$ ZSI with clamping diode from the conventional ZSI using a flow chart, and presents the detailed analysis of the proposed inverter. Then it discusses the benefits of the proposed inverter over existing transformer based ZSI topologies and shows its comparative evaluations through Matlab plots. Finally, experimental hardware of the proposed inverter is shown with validated results and efficiency plot.

#### 3.2 Advantages of Improved ΓZSI with Clamping Diode