## An Electrical Power System for CubeSats

Presented by: Benjamin C. de V. Sheard

Supervisor: Mr. Samuel I. Ginsberg Dept. of Electrical and Electronics Engineering University of Cape Town

Submitted to the Department of Electrical Engineering at the University of Cape Town in partial fulfilment of the academic requirements for a Master of Science degree in Electrical Engineering.

August 2015

The copyright of this thesis vests in the author. No quotation from it or information derived from it is to be published without full acknowledgement of the source. The thesis is to be used for private study or non-commercial research purposes only.

Published by the University of Cape Town (UCT) in terms of the non-exclusive license granted to UCT by the author.

## Declaration

I know the meaning of plagiarism and declare that all work in this document, save for that which is properly acknowledged, is my own.

### Abstract

The advent of CubeSats has provided a platform for relatively low-budget programmes to realise space missions. In South Africa, Stellenbosch University and the Cape Peninsula University of Technology have impressive space programmes and have been involved in numerous successful satellite launches. A number of CubeSat projects are currently in progress and commercial-grade Attitude Determination and Control Systems (ADCS), and communications modules, are being developed by the respective universities. The development of a CubeSat-compatible Electrical Power System remains absent, and would be beneficial to future satellite activity here in South Africa.

In this thesis, some fundamental aspects of electronic design for space applications is looked at, including but not limited to radiation effects on MOSFET devices; this poses one of the greatest challenges to space-based power systems. To this extent, the different radiation-induced effects and their implications are looked at, and mitigation strategies are discussed.

A review of current commercial modules is performed and their design and performance evaluated. A few shortcomings of current systems are noted and corresponding design changes are suggested; in some instances these changes add complexity, but they are shown to introduce appreciable system reliability.

A single Li-Ion cell configuration is proposed that uses a 3.7 V nominal bus voltage. Individual battery charge regulation introduces minor inefficiencies, but allows isolation of cells from the pack in the case of cell failure or degradation. A further advantage is the possibility for multiple energy storage media on the same power bus, allowing for EPS-related technology demonstrations, with an assurance of minimum system capabilities.

The design of each subsystem is discussed and its respective failure modes identified. A limited number of single points of failure are noted and the mitigation strategies taken are discussed. An initial hardware prototype is developed that is used to test and characterise system performance. Although a few minor modifications are needed, the overall system is shown to function as designed and the concepts used are proven. Overall system design is concluded to be reliable and efficient, with a few hardwarebased recommendations made to bring its power capabilities in line with current offerings and, indeed, the initial specifications. Active Maximum Power Point Tracking (MPPT) functionality is tested under a variety of irradiance and temperature conditions and although performance is not yet optimal, control stability and the possibility for high conversion efficiency is demonstrated.

Additional software development is still required to fully optimise the system. Nevertheless, after further testing, performance characterisation and full environmental qualification, it is anticipated that the goal of producing a realistic alternative to commercial-grade EPS modules will be met.

### Acknowledgements

I'd like to begin by extending my sincerest thanks to my supervisor, Mr. Samuel Ginsberg, for his invaluable help, contributions, enthusiasm, humour and guidance throughout the course of this project.

Next, I'd like to thank Dayne Kemp, in part for his motivation that led me down this two-year adventure but also the advice, help and encouragement that he's given.

Thanks must also go to the students from Stellenbosch University's Electronic System Laboratory for suggesting the project and providing an initial set of specifications.

Closer to home, my colleagues from UCT's Electronic Systems Laboratory — for your encouragement, your help and for providing much-needed distractions throughout the year.

Acknowledgement to the National Research Foundation (NRF) must also be given for their financial assistance over the past two years.

To all my friends and family who have provided encouragement and distractions at different points throughout this period, it is all so appreciated.

Finally, but most certainly not least, to my parents — your continuous encouragement, help and everything you have done for me is most gratefully appreciated.

## Contents

| 1        | Inti | roduction                                  | 1  |

|----------|------|--------------------------------------------|----|

|          | 1.1  | Objectives                                 | 2  |

|          | 1.2  | Scope and Limitations                      | 2  |

|          | 1.3  | Outline of the Report                      | 3  |

| <b>2</b> | Des  | igning for Space & Other Background Theory | 4  |

|          | 2.1  | CubeSats                                   | 5  |

|          | 2.2  | The Space Environment                      | 9  |

|          | 2.3  | Photovoltaic Cells                         | 13 |

|          | 2.4  | Energy Storage                             | 21 |

|          | 2.5  | Electronic Design and Failure Analysis     | 25 |

|          | 2.6  | MOSFETs in a Radiation Environment         | 29 |

| 3        | Exi  | sting Systems                              | 35 |

|          | 3.1  | Clyde Space                                | 36 |

|          | 3.2  | GomSpace                                   | 42 |

| 4 | $\mathbf{Sys}$ | tem Design                               | 45  |

|---|----------------|------------------------------------------|-----|

|   | 4.1            | Specifications                           | 46  |

|   | 4.2            | Energy Storage Design                    | 50  |

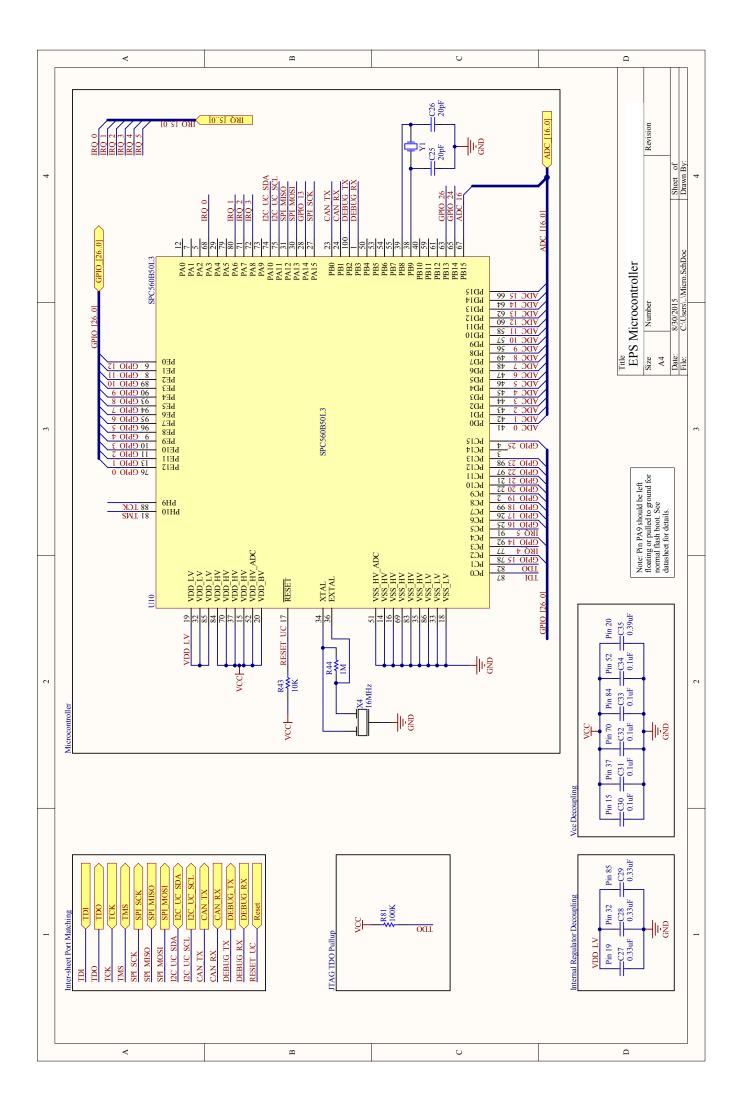

|   | 4.3            | Solar Input Design                       | 57  |

|   | 4.4            | Microcontroller Selection                | 60  |

|   | 4.5            | High-level Design                        | 64  |

| 5 | Haı            | rdware Design                            | 66  |

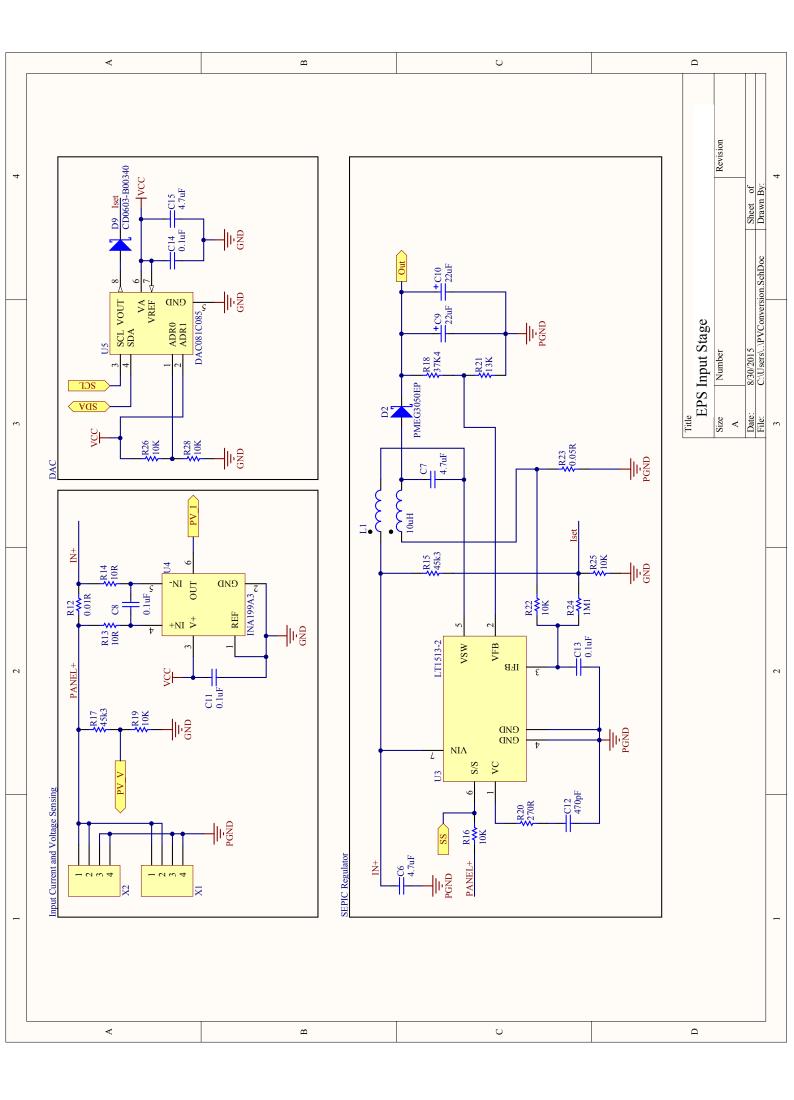

|   | 5.1            | Input Stages                             | 67  |

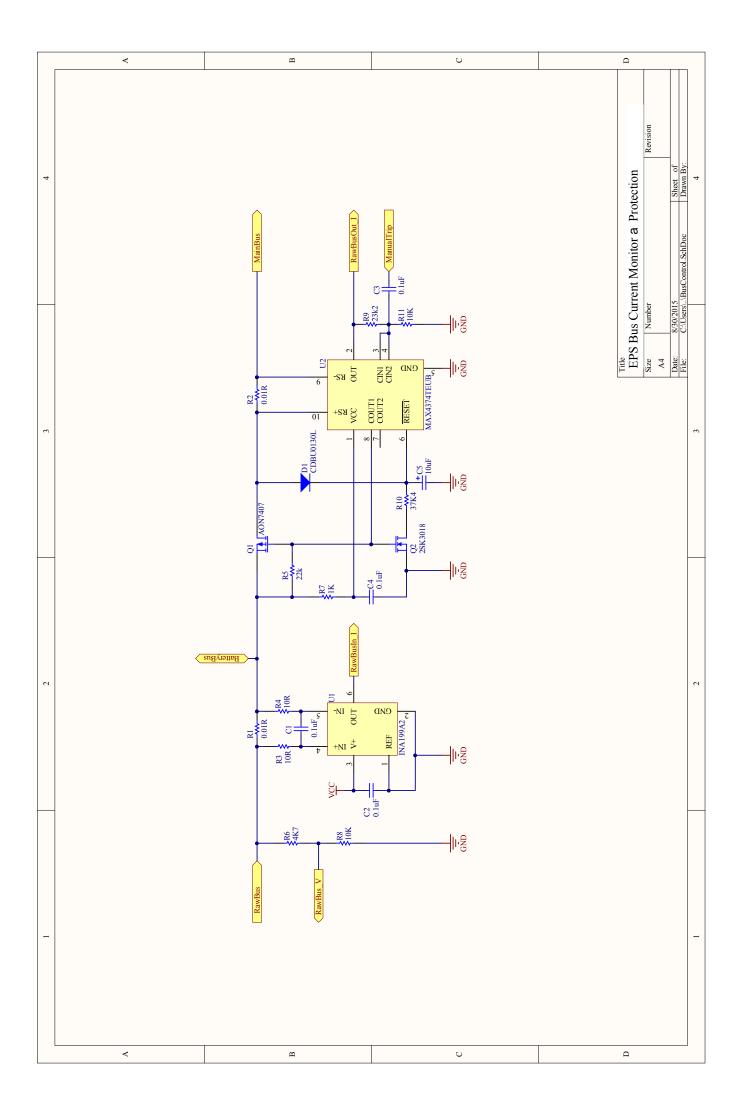

|   | 5.2            | The Bus                                  | 77  |

|   | 5.3            | Kill Switch                              | 83  |

|   | 5.4            | Regulators                               | 88  |

|   | 5.5            | Payload Switches                         | 92  |

|   | 5.6            | Lithium-Ion Cells                        | 95  |

|   | 5.7            | Supporting Circuitry                     | 104 |

|   | 5.8            | PCB Design                               | 107 |

| 6 | Sof            | tware Design                             | 108 |

|   | 6.1            | Microcontroller Features and Peripherals | 109 |

|   | 6.2            | Functions                                | 114 |

|   | 6.3            | Maximum Power Point Tracking             | 125 |

|   | 6.4            | Payload Monitoring                       | 132 |

|              | 6.5 | System Monitoring                   | 135 |

|--------------|-----|-------------------------------------|-----|

|              | 6.6 | Housekeeping                        | 136 |

|              | 6.7 | Pre-emption and Priority Management | 137 |

| 7            | Res | ults & Analysis                     | 139 |

|              | 7.1 | Maximum Power Point Tracking        | 140 |

|              | 7.2 | Performance and Efficiencies        | 148 |

|              | 7.3 | Output Capabilities                 | 153 |

| 8            | Con | clusions                            | 157 |

|              | 8.1 | Reliability                         | 158 |

|              | 8.2 | Functionality                       | 158 |

|              | 8.3 | Power Capabilities                  | 159 |

|              | 8.4 | Efficiency                          | 159 |

|              | 8.5 | Supporting Software                 | 160 |

|              | 8.6 | Cost                                | 160 |

| 9            | Rec | ommendations                        | 161 |

|              | 9.1 | Hardware Revision                   | 161 |

|              | 9.2 | Software Refinement                 | 163 |

|              | 9.3 | Further Testing                     | 164 |

| $\mathbf{A}$ | The | EPS Module                          | 171 |

|              | A.1            | External Connections                  | 171 |

|--------------|----------------|---------------------------------------|-----|

|              | A.2            | Communications Configuration          | 175 |

|              | A.3            | Specifications                        | 175 |

|              | A.4            | Photographs                           | 175 |

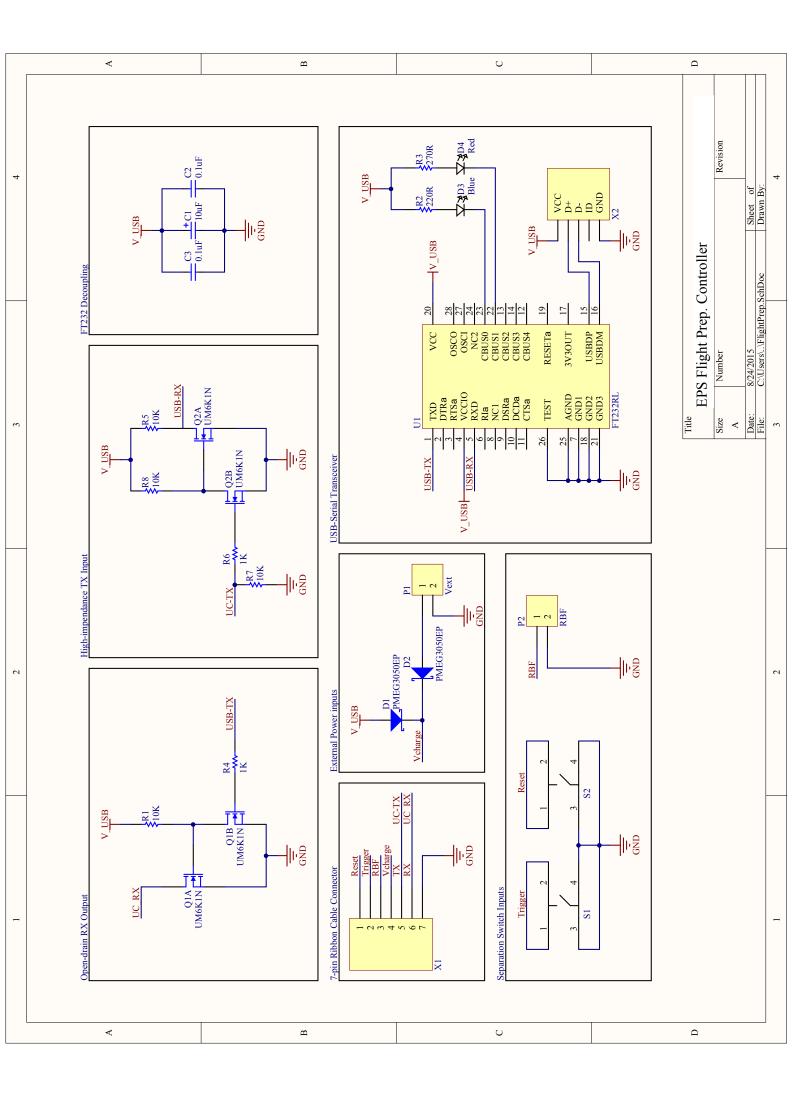

| в            | Flig           | ht Preparation                        | 178 |

|              | B.1            | The Physical Interface                | 178 |

|              | B.2            | The Software Interface                | 180 |

| С            | Sola           | r Simulation & Panel Characterisation | 183 |

|              | C.1            | Simulator Design                      | 183 |

|              | C.2            | Solar Panel Characterisation          | 184 |

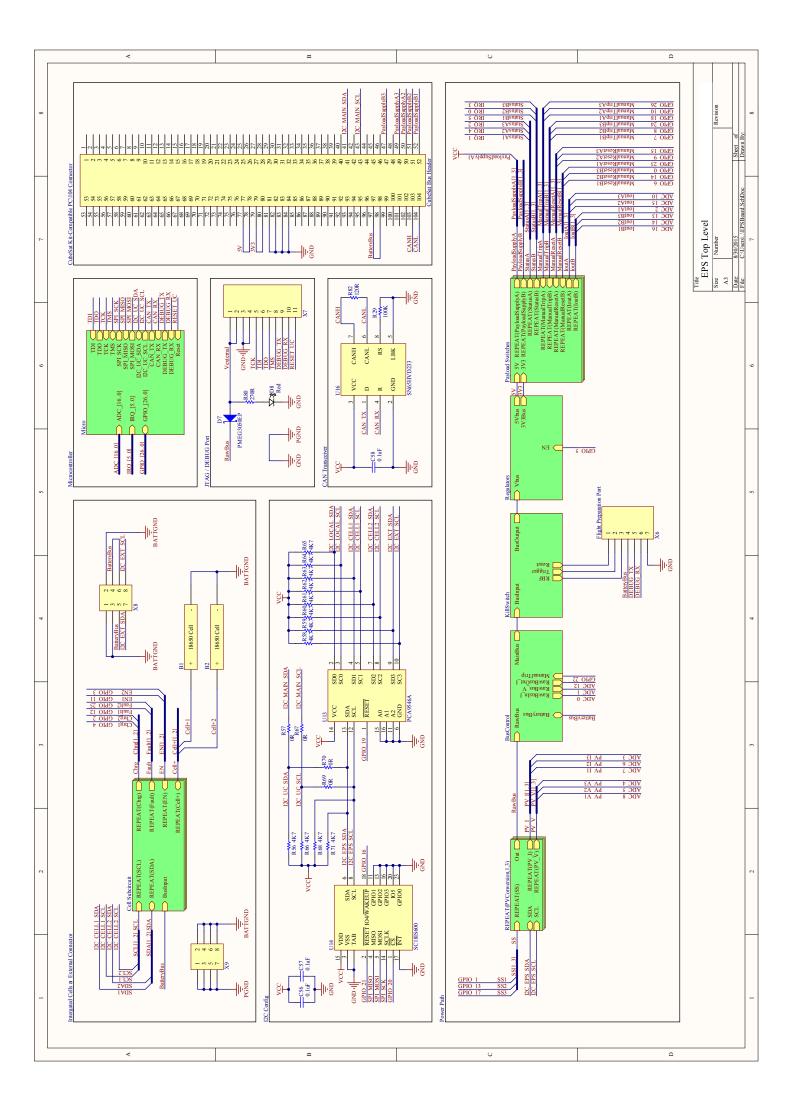

| D            | Sche           | ematics                               | 188 |

|              | D.1            | Electrical Power System               | 188 |

|              | D.2            | Flight Preparation Controller         | 198 |

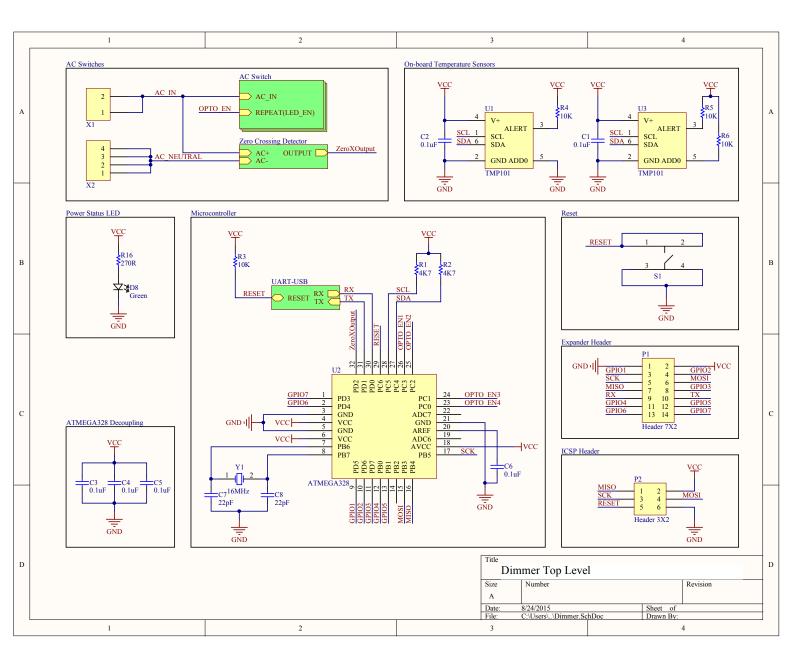

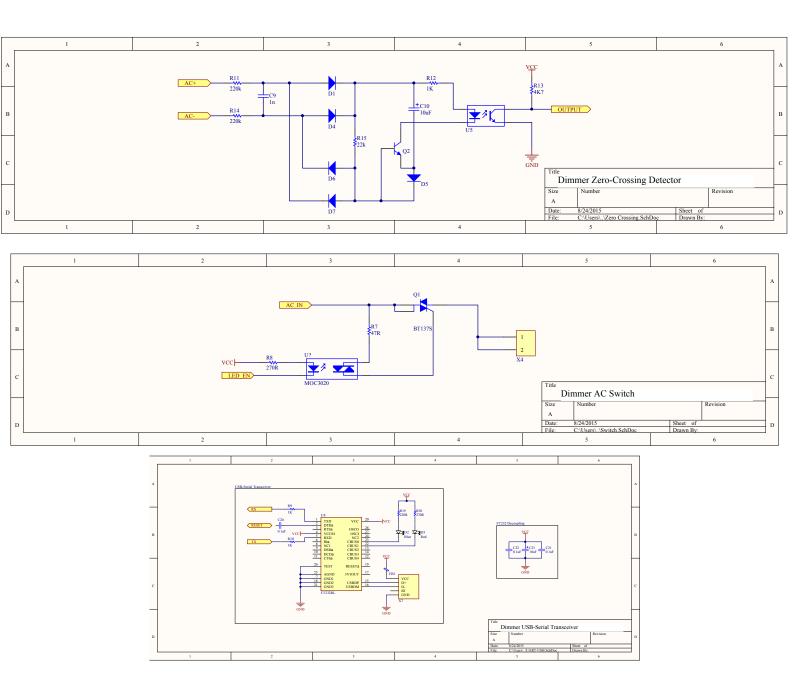

|              | D.3            | AC Dimmer Board                       | 200 |

| $\mathbf{E}$ | Dev            | elopment Toolchain                    | 203 |

|              | E.1            | Development Board                     | 203 |

|              | E.2            | Toolchain                             | 204 |

| $\mathbf{F}$ | $\mathbf{Eth}$ | ics Form                              | 205 |

# List of Figures

| 2.1 | Computer render of ZACube-1                                                                                                                                          | 8  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

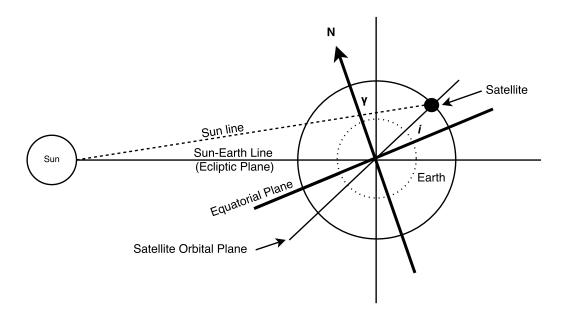

| 2.2 | Diagram depicting the geometry of the Sun-Earth-satellite system                                                                                                     | 11 |

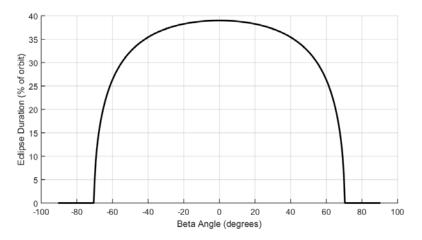

| 2.3 | Variation in a spacecraft's eclipse period with beta angle at a 400 km altitude                                                                                      | 12 |

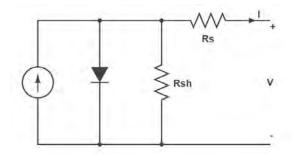

| 2.4 | Equivalent circuit of a solar cell                                                                                                                                   | 15 |

| 2.5 | Plots showing the variations in a solar cell's I-V curve with varying cell parameters.                                                                               | 16 |

| 2.6 | Annual total dose versus shielding for different qualification levels                                                                                                | 27 |

| 2.7 | Plot showing the threshold voltage of <i>n</i> - and <i>p</i> -channel MOSFETs as a function of radiation dose, for devices biased 'on' and 'off' during irradiation | 34 |

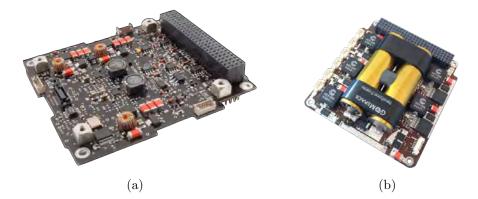

| 3.1 | CubeSat EPS modules available from Clyde Space and GomSpace                                                                                                          | 35 |

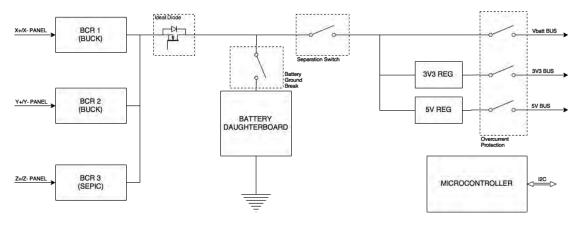

| 3.2 | Block diagram of the Clyde Space 1U CubeSat EPS                                                                                                                      | 37 |

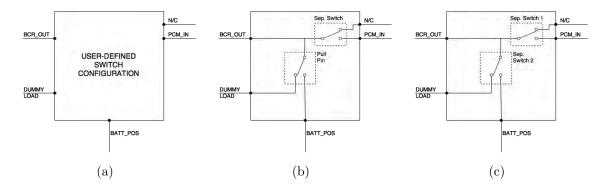

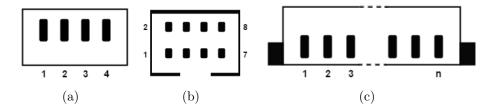

| 3.3 | Switch configuration options for Clyde Space's EPS modules                                                                                                           | 38 |

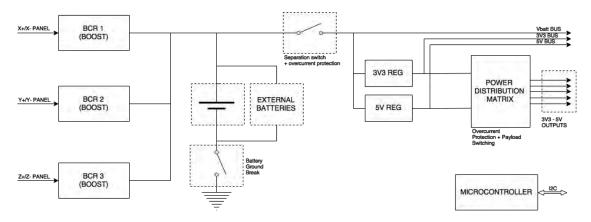

| 3.4 | Block diagram of the Gomspace CubeSat EPS                                                                                                                            | 43 |

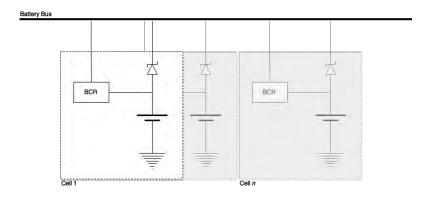

| 4.1 | High level block diagram for a single-cell battery configuration with independent charging.                                                                          | 54 |

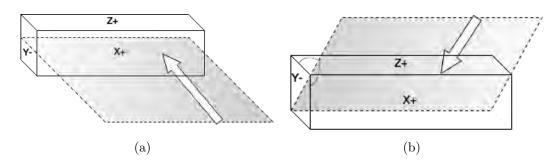

| 4.2  | Diagrams depicting different cases of irradiance angles                                                 | 58  |

|------|---------------------------------------------------------------------------------------------------------|-----|

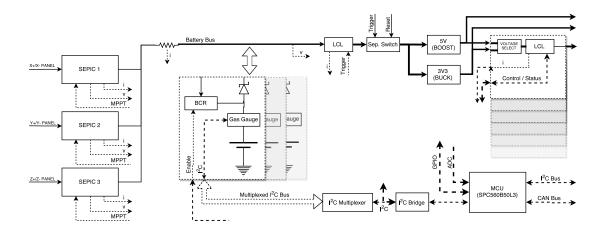

| 4.3  | High-level block diagram for the full EPS                                                               | 65  |

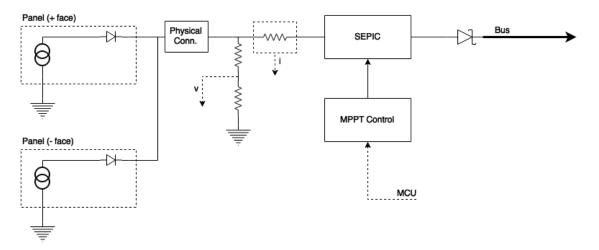

| 5.1  | Block diagram for the input stage                                                                       | 67  |

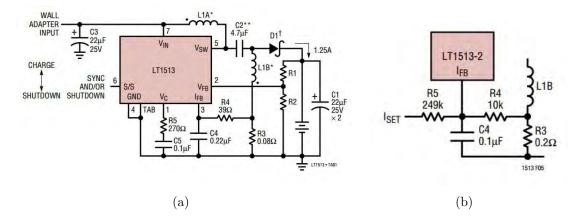

| 5.2  | Datasheet-suggested schematic design for the LT1513                                                     | 69  |

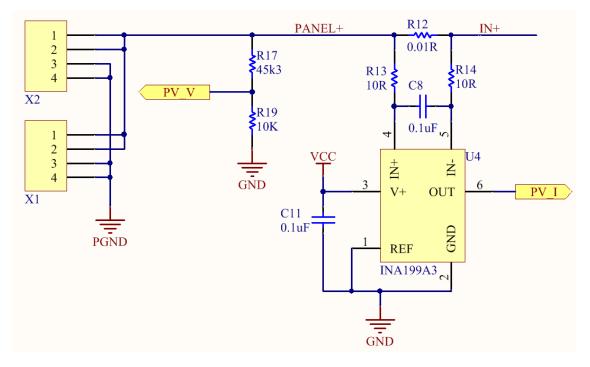

| 5.3  | Schematic of the input connectors and current and voltage sensing.                                      | 71  |

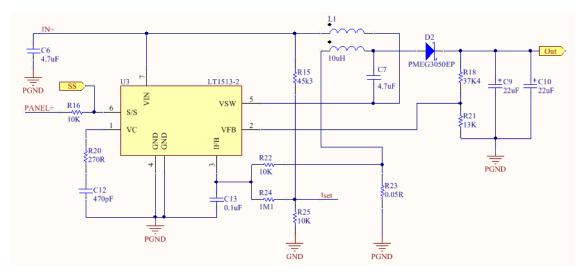

| 5.4  | Schematic of the input stage LT1513-2 regulator.                                                        | 72  |

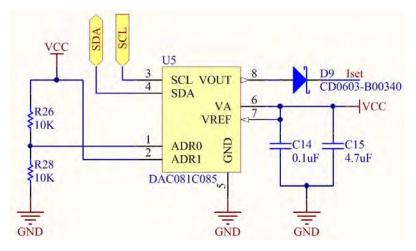

| 5.5  | Schematic of the input stage DAC.                                                                       | 74  |

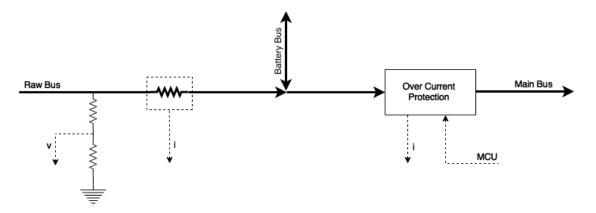

| 5.6  | Block diagram for bus monitoring and overcurrent protection sub-<br>system                              | 77  |

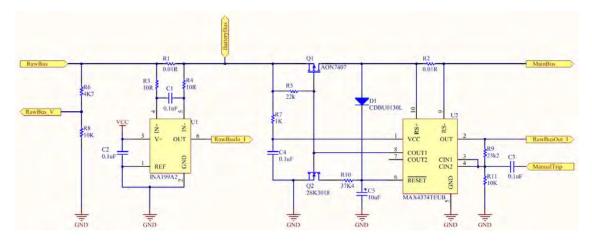

| 5.7  | Schematic of the bus current monitoring and overcurrent protection subsystem                            | 79  |

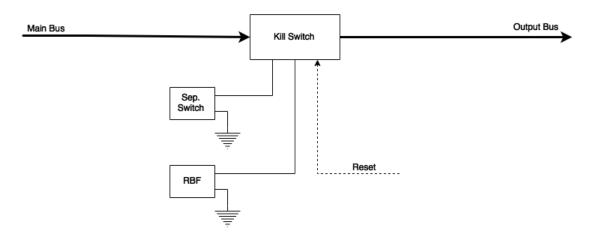

| 5.8  | Block diagram for the kill switch subsystem.                                                            | 83  |

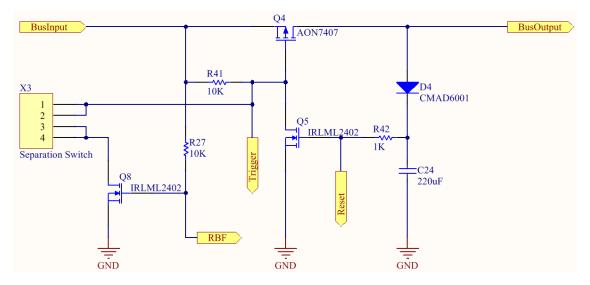

| 5.9  | Schematic of the kill switch subsystem.                                                                 | 85  |

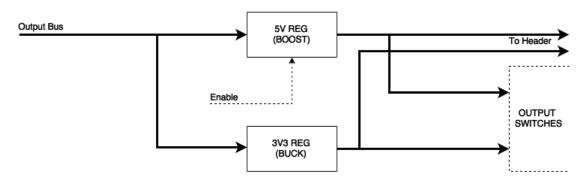

| 5.10 | Block diagram for the switch-mode regulators                                                            | 88  |

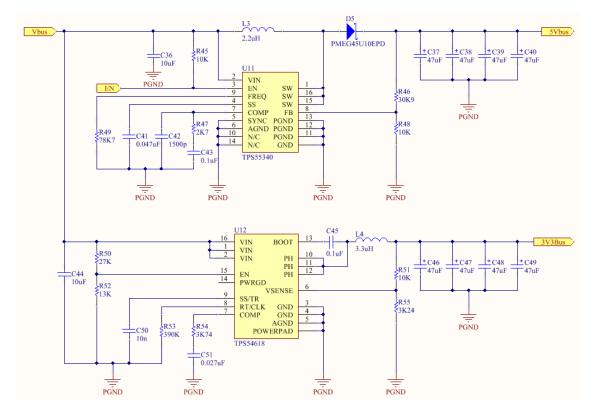

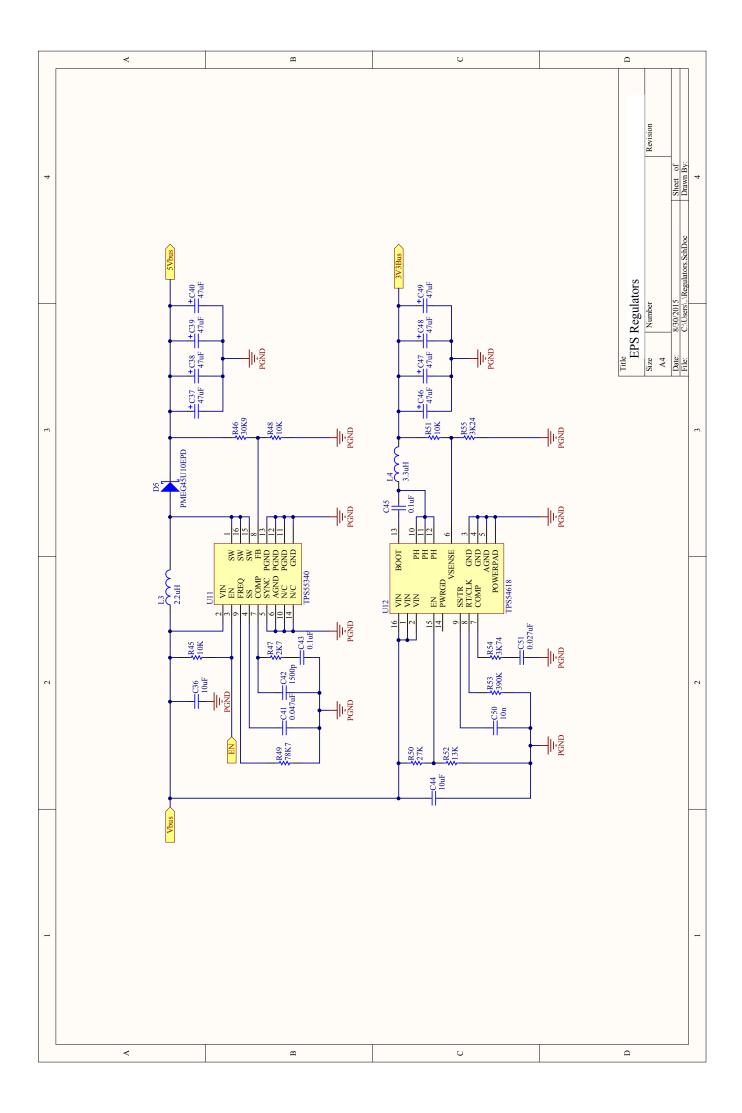

| 5.11 | Schematic of the switch-mode regulators                                                                 | 89  |

| 5.12 | Block diagram for the payload switch subsystem.                                                         | 92  |

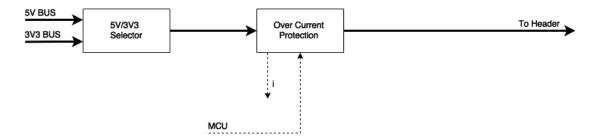

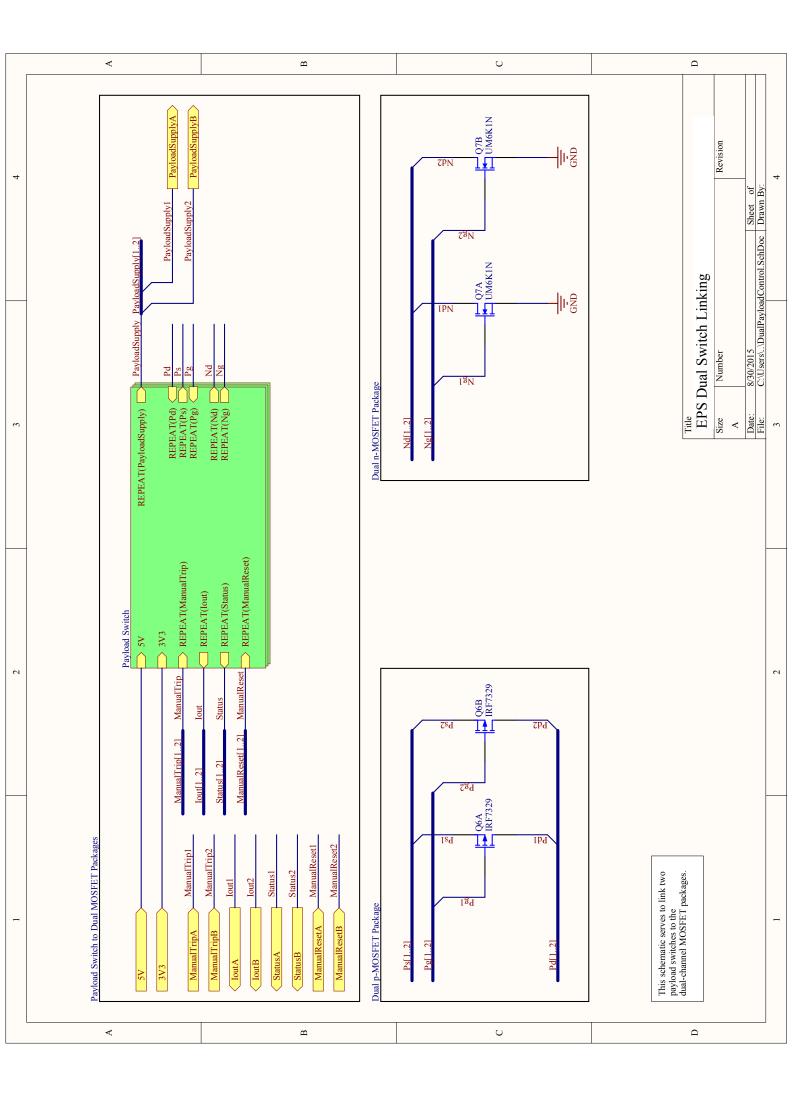

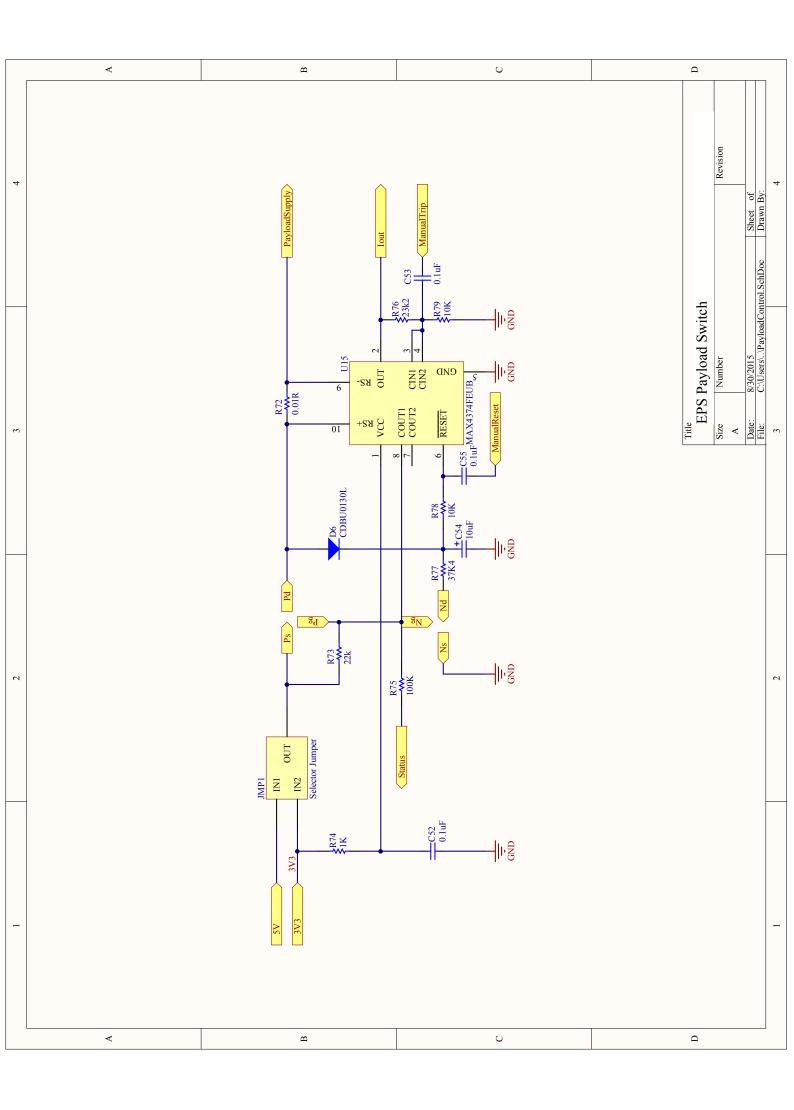

| 5.13 | Schematic of the payload switch subsystem.                                                              | 93  |

| 5.14 | Block diagram for the integrated cell subsystems, including the in-<br>terface to external cell modules | 95  |

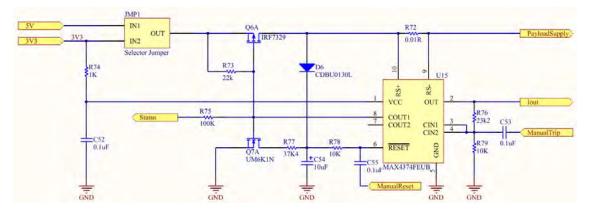

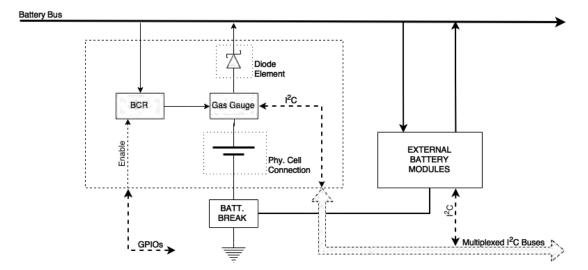

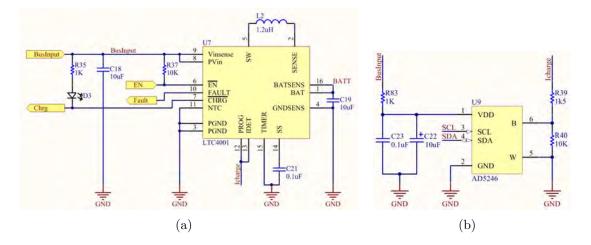

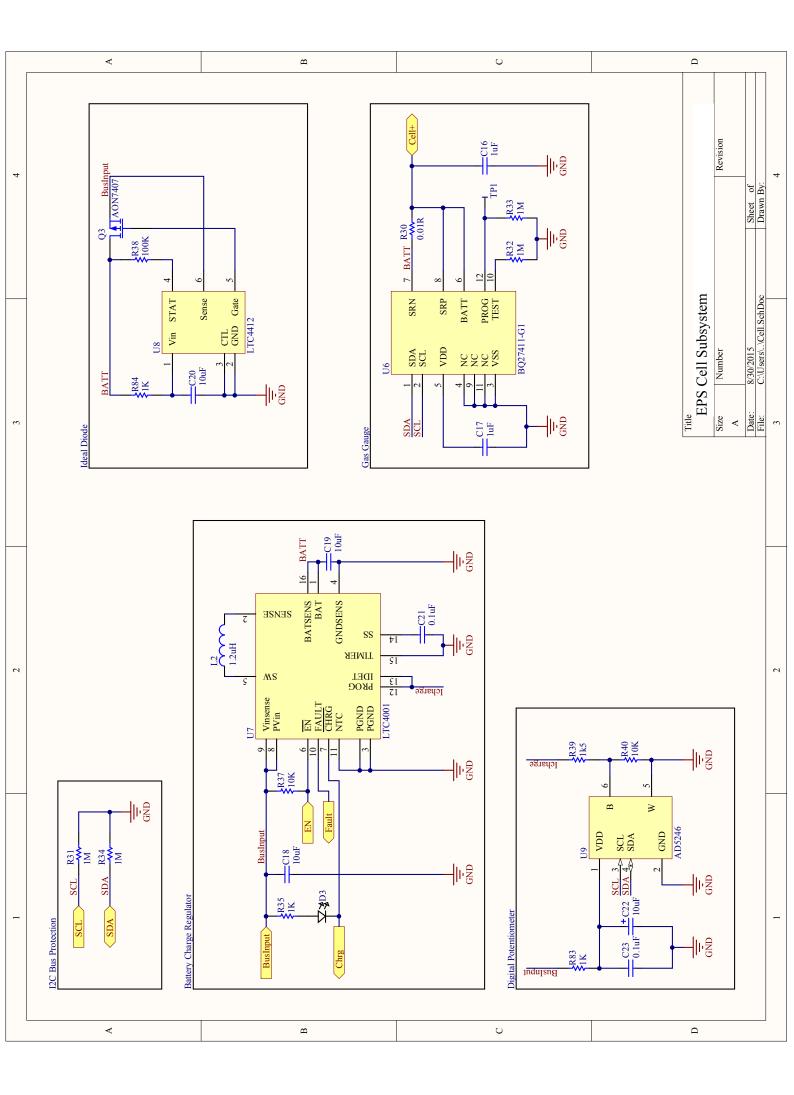

| 5.15 | Schematic of the cell subsystem's battery charge regulator and digital potentiometer.                   | 98  |

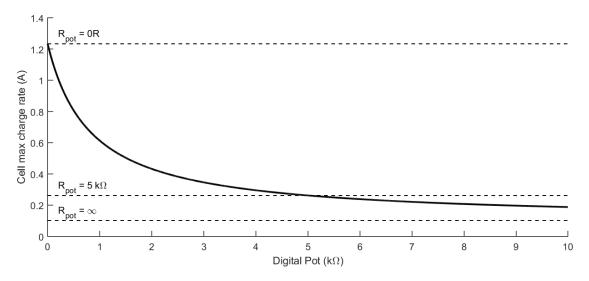

| 5.16 | Variations in cell charge current over the digital potentiometer range.                                 | 100 |

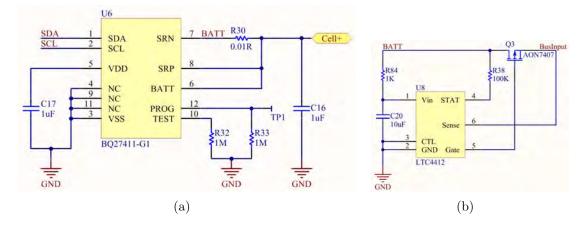

| 5.17 | Schematic of the cell subsystem's gas gauge and ideal diode controller                      | .101 |

|------|---------------------------------------------------------------------------------------------|------|

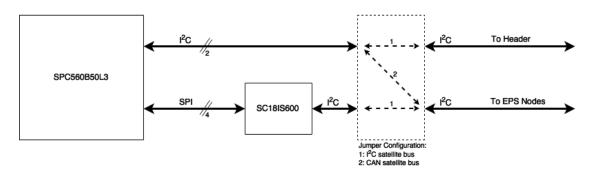

| 5.18 | Block diagram for $I^2C$ bus configurations                                                 |      |

| 5.19 | Copper layer of the solder jumper design                                                    | 107  |

| 6.1  | Characterisation of operating point control showing different DAC setpoints.                | 126  |

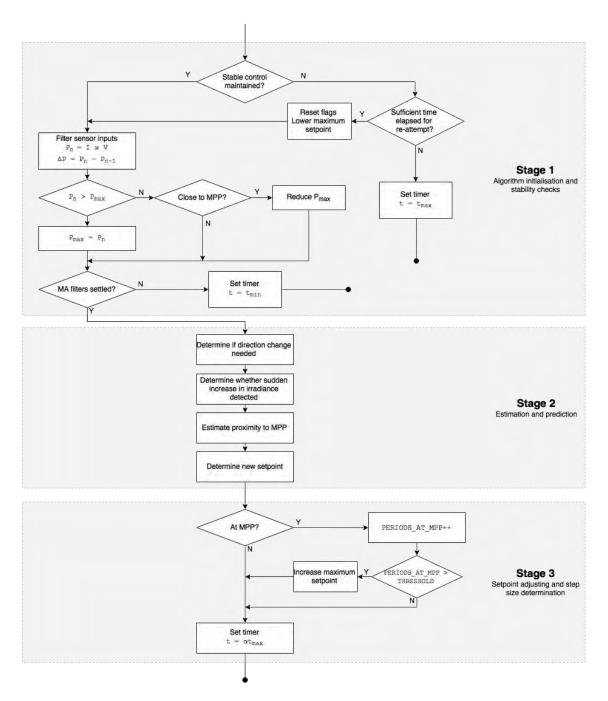

| 6.2  | Depiction of the MPPT algorithm.                                                            | 129  |

| 6.3  | Depiction of the payload monitoring system                                                  | 134  |

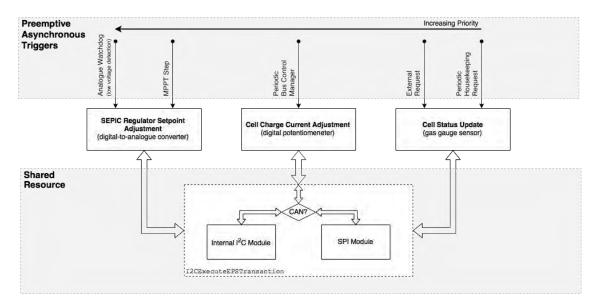

| 6.4  | Sources and priorities of triggers to the $\mathrm{I}^2\mathrm{C}$ module                   | 137  |

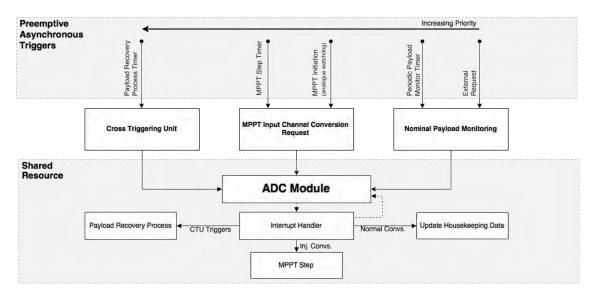

| 6.5  | Sources and priorities of triggers to the ADC module                                        | 138  |

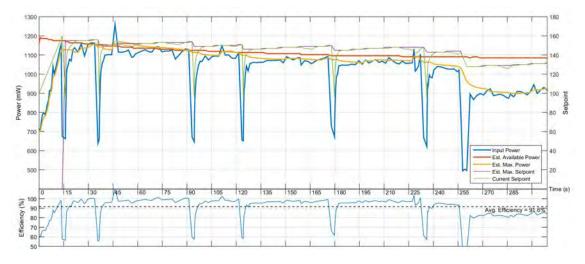

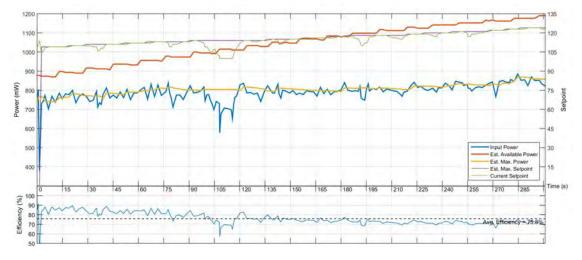

| 7.1  | MPPT algorithm performance plot for a fixed irradiance                                      | 141  |

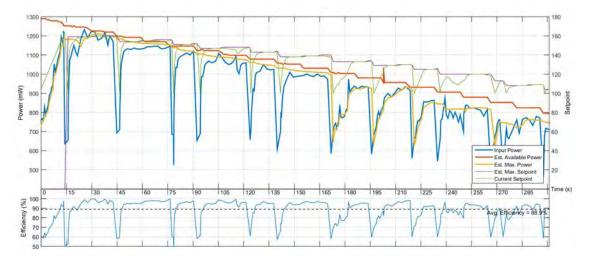

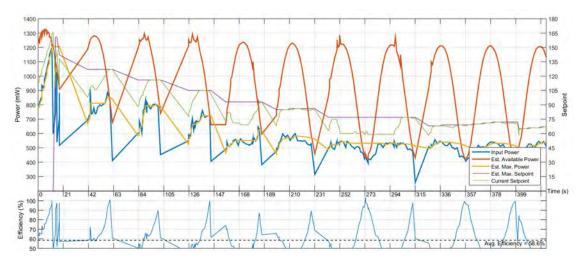

| 7.2  | MPPT algorithm performance plot for periodic step decreases in irradiance                   | 142  |

| 7.3  | MPPT algorithm performance plot for periodic step increases in irradiance.                  | 143  |

| 7.4  | MPPT algorithm performance plot for a spinning satellite                                    | 144  |

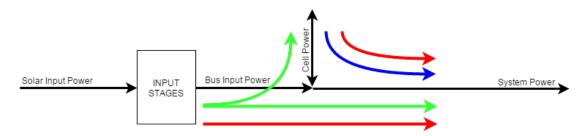

| 7.5  | Bus power flow cases                                                                        | 148  |

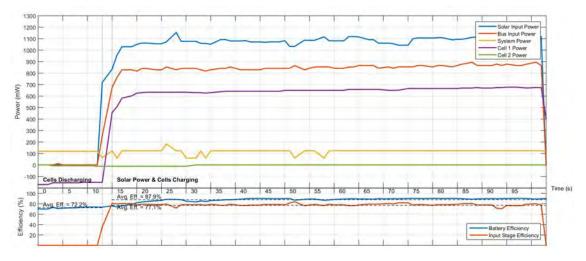

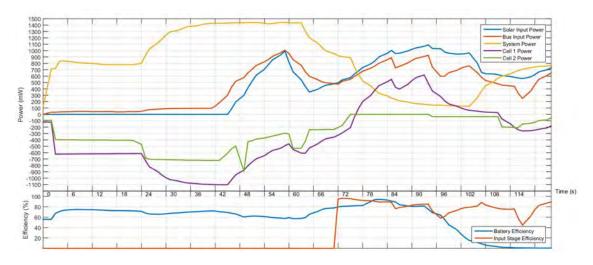

| 7.6  | Power flow through the different bus branches showing input and cell charging efficiencies. | 149  |

| 7.7  | Power flow through the different bus branches for varying load cases.                       | 150  |

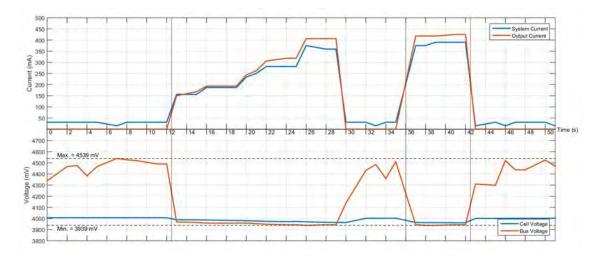

| 7.8  | Power bus response to small system loads                                                    | 153  |

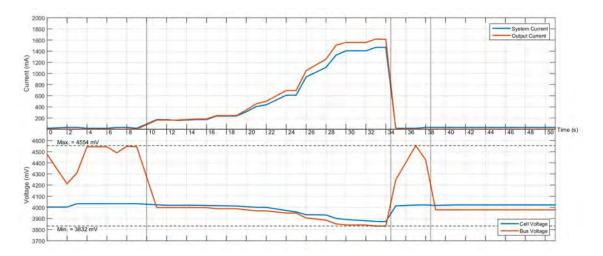

| 7.9  | Power bus response to large system loads.                                                   | 154  |

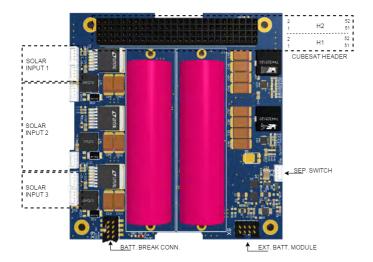

| A.1 | Position of physical connectors on the topside of the module                                   | 172 |

|-----|------------------------------------------------------------------------------------------------|-----|

| A.2 | Pin numbering of the Molex Picoblade connectors and the eight-pin FCI connectors               | 172 |

| A.3 | Pin numbering of the CubeSat Kit Header connector                                              | 174 |

| A.4 | Position of the communications-bus jumpers on the PCB                                          | 175 |

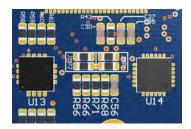

| A.5 | Photographs of the prototype module.                                                           | 177 |

| D 1 |                                                                                                | 170 |

| В.1 | Photograph of the Flight Preparation Controller interface                                      | 179 |

| B.2 | Screenshot of the Flight Preparation GUI.                                                      | 182 |

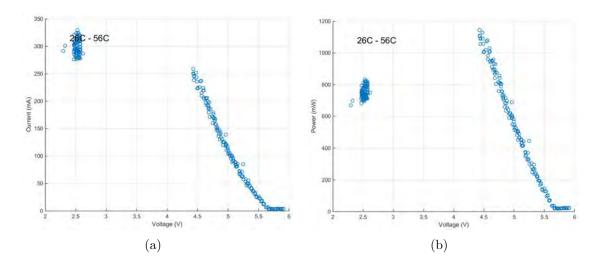

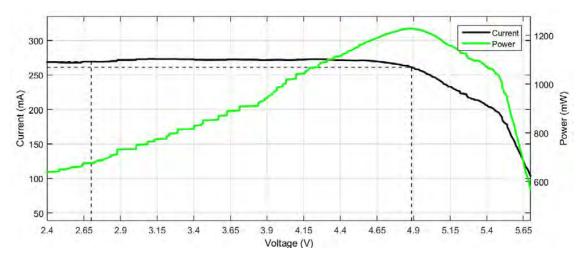

| C.1 | I-V and P-V curves of the solar panels used during testing                                     | 185 |

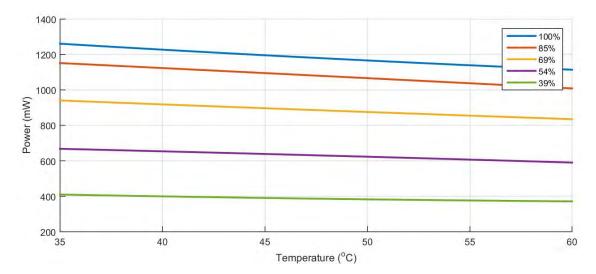

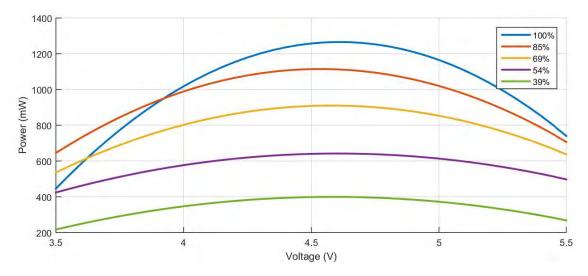

| C.2 | Variation in maximum panel output power with temperature for dif-<br>ferent irradiance levels. | 196 |

|     |                                                                                                | 100 |

| C.3 | Variation in the panel's P-V curve with different irradiance levels at                         | 100 |

|     | $35^{\circ}$ C                                                                                 | 186 |

## List of Tables

| 2.1 | Beginning-of-Life (BOL) specifications for the Clyde Space 1U solar panel. | 14  |

|-----|----------------------------------------------------------------------------|-----|

| 3.1 | Specifications for the Clyde Space range of EPS modules                    | 40  |

| 3.2 | Specifications for the Gomspace range of EPS modules                       | 44  |

| 4.1 | Specifications for the BCAP1500 Maxwell supercapacitor                     | 51  |

| 4.2 | Specifications for a variety of suitable microcontrollers                  | 63  |

| 6.1 | Payload channel settings available within the system settings              | 132 |

| A.1 | EPS specifications for the current hardware revision                       | 176 |

| B.1 | Pin definitions for the Flight Preparation Controller interface            | 179 |

| B.2 | Commands available in preparation mode                                     | 181 |

| C.1 | Commands available for the solar-simulation controller                     | 184 |

## Acronyms

- **ADC** Analogue-to-Digital Converter.

- **ADCS** Attitude Determination and Control System.

- BCR Battery Charge Regulator.

- **BOL** Beginning-of-Life.

- **CAN** Controller Area Network.

- $\mathbf{C}\mathbf{C}$  Constant Current.

- **COTS** Commercial off-the-Shelf.

- **CPUT** Cape Peninsula University of Technology.

- **CRC** Cyclic Redundancy Check.

- **CV** Constant Voltage.

- **DMA** Direct Access Memory.

- **DOD** Depth of Discharge.

- **ECC** Error Correcting Code.

- **EDAC** Error Correction and Detection.

- **EM** Electro-magnetic.

- **EPS** Electrical Power System.

- **ESR** Equivalent Series Resistance.

F'SATI French South African Institute of Technology.

${\bf IR}\,$  Infrared.

- LCL Latching Current Limiter.

- ${\bf LEO}~{\rm Low}$  Earth Orbit.

MPPT Maximum Power Point Tracking.

- **MTBF** Mean Time Between Failures.

- ${\bf RBF}\,$  Remove Before Flight.

- ${\bf RTG}\,$  Radioisotope Thermoelectric Generator.

- SAA South Atlantic Anomaly.

- **SCR** Silicon Controlled Rectifier.

- **SEB** Single Event Burnout.

- **SEC-DED** Single Error Correction, Double Error Detection.

- **SEE** Single Event Effect.

- **SEL** Single Event Latchup.

- **SEU** Single Event Upset.

- **SOC** State of Charge.

- **SUN** Stellenbosch University.

- **TID** Total Ionising Dose.

.

## Chapter 1

## Introduction

The field of electronics is ever-evolving; new applications require new technology, and innovative ways are found to use this technology. While the application of electronics to space exploration is inherent and has existed for over fifty years, opportunity for innovative and/or new electronic space systems was limited, given that space missions were, for a long time, associated with high budgets and long timeframes.

It was the advent of the nanosatellite category and the subsequent CubeSat concept that, in 1999, opened up the field of space technology to universities and similar institutions. Very quickly, it became possible for low-budget missions to realise a launch, at low cost, within a reasonable timeframe.

In South Africa, an increasing level of satellite work is being seen: both the Cape Peninsula University of Technology (CPUT) and Stellenbosch University (SUN) have been involved with successful nano- and micro-satellite launches, and have active space-based research programmes. Impressive work is being done on Attitude Determination and Control Systems, as well as communications systems, with these modules seeing international commercial availability.

The development of a CubeSat-compatible Electrical Power System (EPS) module serves two purposes: it initiates the University of Cape Town's contribution to the field of space technology, and also makes available a local EPS module for use on future CubeSat missions; no such module is currently available.

### 1.1 Objectives

The objectives of this work are thus to design a CubeSat-compatible EPS that is a realistic alternative to the commercial modules currently used for local satellite projects. Although the scope will show that having a flight-ready module as the initial aim is impractical for a variety of reasons, this remains the ultimate goal; thus, this work serves to produce such a system that, after some further development and testing, can achieve this end goal.

In light of this, the objectives are thus to design a system that takes into account the reliability, efficiency and functionality needed, in such an application, at each fundamental design step. Functionality and performance should match or exceed that of comparable modules which necessitates a review of such modules.

Sufficient testing of the system must be done to quantify its suitability to meeting the end goal.

## **1.2** Scope and Limitations

Work is initiated with the intention to develop a fully-functional EPS module that has the potential to be used on CubeSat missions. However, the long time frames that are associated with full qualification and testing, make the production of a flight-ready module impractical, and thus it is not the immediate goal.

Having the system evolve into one that is flight-ready, nevertheless, remains the ultimate purpose of this work; thus, sufficient scope is given to produce a system, ready for initial (ground-based) field testing, and to validate its suitability to Cube-Sat missions. Full consideration for this end goal should be given, at each step of the design process, to prevent fundamental compromises being made.

### 1.3 Outline of the Report

This report begins with a review of relevant background theory, literature and aspects of electronic design, in the context of space-based applications. Particular focus is placed upon different energy storage technologies, the harvesting of solar power and the effects of radiation on electronics.

A brief but detailed review is then done of existing EPS modules that have seen popularity amongst international, but more importantly local, CubeSat missions. The functionality and performance of these modules is used initially as a guideline for the EPS design, and later as a benchmark for performance analysis.

The work then shifts to the preliminary specifications and high-level design of the module. Few assumptions are started with and each subsystem is carefully specified and its implementation discussed. Where relevant, consideration is given to maintaining compatibility with current designs. By the end of System Design, a high-level design is presented that has each subsystem well defined and specified.

Chapter 5 presents the schematic design of each subsystem: component choice is argued, the low-level operation is discussed where relevant, and a detailed analysis is performed that identifies points of failure.

The design of the application software is then discussed, with a high-level approach taken to present the flow of operation. A number of key software features are discussed, as well as an overview of the high-level tasks that are performed.

Results and accompanying analyses follow, with emphasis placed upon the capabilities and efficiencies of the system. Certain aspects of the system are discussed with respect to improvements that are needed.

The work concludes with conclusions and recommendations, before a series of appendices provide summaries of system functions, along with additional work that was performed.

## Chapter 2

# Designing for Space & Other Background Theory

Compared to other nanosatellite subsystems, the EPS appears to have very little research devoted to it. This may be because the design of scientific payloads, advanced communications systems and the like, is far more appealing than that of the underlying power system. Moreover, its critical role may also be a deterring factor: with mission designers unwilling to risk new power systems over those with flight heritage, there is little opportunity for new research to be put into practice.

EPS-based innovation, at least for CubeSats and nanosatellites, appears to be limited to university designs for student CubeSat projects. It has been noted that such EPS designs are often overly complex, due to a need and/or desire for innovation [1], which may be the reason for the suggestion of the power system being the leading cause of CubeSat failure [2, p. 807]. Thus, something could be said for innovation being an improvement upon the fundamental reliability of the system.

Given this, and an aim to produce a system that is a realistic alternative to commercially-available, flight-proven systems, this chapter will focus on some fundamentals to allow a truly reliable and flexible end product be designed.

### 2.1 CubeSats

Nanosatellites are a category of small satellites typically weighing between 1 and 10 kg. CubeSats, a subset of nanosatellites, are characterised by complying with a specific set of design rules and constraints. This standardisation is what drives down their cost and development time, and allows the possibility for "plug-and-play" modules. This section looks at said standardisation, as well as past, present and future CubeSat activity in South Africa.

#### 2.1.1 Specifications

CubeSats take their name from, and indeed are characterised by, the ten centimetre cubes that make up their structure. These cubes are referred to as "units", with a basic one-unit structure known as a "1U CubeSat". Usually only expandable along one axis — in multiples of these cubes and limited to a total of three such cubes — variations on this, such as 0.5U and 6U, have been seen. The limitation comes from the fact that multiple CubeSats are deployed using a standard deployment mechanism; as a result, they must conform to very specific sizing constraints.

With the CubeSat design philosophy suggesting low cost, electronic components are usually limited to Commercial off-the-Shelf (COTS) devices that are far cheaper, and more widely available, than their radiation-hardened counterparts. To make operation with such components more reliable, CubeSats are generally limited to Low Earth Orbit (LEO) with altitudes ranging from around 100–600 km. At these low altitudes, the spacecraft is still under appreciable protection from the Earth's magnetosphere, making exposure to ionising radiation tolerable [3].

Nevertheless, the lifespan of CubeSats is typically limited to 24 months. Besides radiation-induced electronic degradation, the multiple daily eclipse periods — a result of being in Low Earth Orbit (LEO) — means that on-board batteries suffer thousands of cycles over any extended period. The Colorado Student Space Weather Experiment (CSSWE) CubeSat is one such example where severe battery degradation, after 24 months, meant there was no longer sufficient power for the transmitter to function [4].

#### 2.1.2 The Electrical Power System

The primary function of the EPS is to deliver electrical power to other subsystems, with power generation the first step of this process. While solar energy is most frequently used — it is reliable, cheap, safe and predictable — satellites with higher power requirements, as well as spacecraft heading to the outer solar system, may rely on other methods such as a Radioisotope Thermoelectric Generator (RTG). An RTG generates heat from the slow decay of a radioactive element and is a very effective method for large spacecraft — *Voyager 1* for instance, launched in 1977 and currently passing through the outer threshold of our solar system and into interstellar space, has RTGs that still generate a constant 225 W of power, down from 470 W at launch [5].

In order to effectively distribute power, the generated power needs to be stored as well as regulated. An on-board processor will typically perform some power management, including but not limited to overcurrent protection, turning subsystems on and off and providing housekeeping data to the communications bus.

A detailed power budget would be drawn up by the mission designer. From this, a set of power requirements can be determined in order to specify the size of solar panels and energy storage. These power requirements need to take into account the anticipated orbital parameters as these influence the number and length of eclipse periods. The tight sizing constraints also mean that solar panels are usually limited to being mounted on the body, although a driving need for more power has seen an increase in the use of deployable panels [2, pp. 807-808].

#### 2.1.3 The CubeSat Kit Standard

The popularity of CubeSats and their use for fast turnaround missions has led to a number of commercially-available EPS modules. *GomSpace* and *Clyde Space* both provide a good range of products that are widely used, and Chapter 3 looks at their range of EPS modules in detail.

As a result of said popularity a form of standard has evolved, known as CubeSat Kit. While essentially a prototyping platform, allowing the development of missionspecific modules including both software and hardware, it also defines a structure and set of requirements to allow different modules to connect to one another and interact through a defined bus system [6].

Modules that comply to CubeSat Kit are based on a PC/104 mechanical design. The characteristic stack-through connector and physical size makes it well-suited to CubeSats, with the connector allowing a "bus" structure that has pin functionality fairly well defined.

Inter-subsystem communications are typically carried out over an  $I^2C$  bus available on the header, although with no specification as to data packets or how subsystems should communicate. A central processor, usually apart of a "motherboard", manages communications and acts as the bus master — it will run mission-specific software that issues commands to and requests data from subsystems, which it then prepares for downlink via the communications system.

#### 2.1.4 Launch Requirements

The standardisation of the CubeSat deployment process means that a few launch requirements exist [7]. At a minimum, a CubeSat is required to have one 'kill switch' that disables the CubeSat during launch. A separation switch will usually be positioned on the top plate of the CubeSat and use the deployment rails to keep it depressed. As the CubeSat is automatically released, this switch is activated and can allow the satellite to turn on. Depending on implementation, this separation switch may be the kill switch, or, rather, be used to trigger a separate kill switch.

In addition, the CubeSat requires a Remove Before Flight (RBF) pin that keeps the satellite deactivated during shipping and launch preparation. This pin usually functions such as to prevent the separation switch from triggering a separate kill switch.

#### 2.1.5 South African CubeSat Work

CubeSats are relatively new to the South African scene with the first locally-built CubeSat launched in 2013. Named ZACube-1, the 1U CubeSat was built through a collaboration by the French South African Institute of Technology (F'SATI) based at the CPUT, SUN and the South African National Space Agency (SANSA) [8].

ZACube-1's Attitude Determination and Control System (ADCS) and RF communications system were developed by CPUT. The on-board computer (OBC) module and EPS were both purchased from Pumpkin Inc. and Clyde Space respectively [9].

Although ZACube-1 is experiencing problems with its primary payload, it is still responsive and transmitting. Meanwhile, work is underway on ZACube-2, a 3U CubeSat that will serve as a technology demonstrator for a Software Defined Radio (SDR) platform. ZACube-2 will feature an ADCS developed by SUN, an RF communications module developed by CPUT, and a Clyde Space EPS [10].

ZA-AeroSat is a 2U CubeSat under development by SUN as apart of QB50, an initiative by the Von Karman Institute in Belgium that aims to simultaneously launch 50 CubeSats in early 2016 [11]. This CubeSat will use an innovative passive aerodynamic attitude control system, developed by the university.

Apart from these projects, SUN and CPUT are continuing development and research on their respective ADCS and RF communications modules and related work. It seems work on an EPS remains absent, and that such a module would help contribute to a future CubeSat that is entirely South African-developed.

Figure 2.1: Computer render of ZACube-1. Image Credit: F'SATI.

### 2.2 The Space Environment

One of the most significant differences between systems designed for terrestrial use versus space is their operating environment. Radiation is probably the greatest threat to electronics, with further stress coming from large temperature variations and being in a near-vacuum. In addition, an EPS needs to take into account solar availability and strength, and implications the orbital path has on this.

#### 2.2.1 Radiation

The harsh radiation environment in space presents a significant challenge to the design of space-destined electronics. Trapped protons and electrons within the Van Allen belts, heavy ions trapped within the magnetosphere, cosmic ray protons and heavy ions, and protons and heavy ions from solar flares are all sources of radiation, and are the predominant sources of energetic particles within the space environment [12]. While the specifics of each of these sources is not of immediate interest, what should be noted is that the amount of radiation experienced by a satellite will vary depending on numerous factors, including coinciding solar activity and the satellite's specific orbital path.

For low-altitude satellites, the dominant radiation source will be the Van Allen belts. Orbital inclinations of  $0^{\circ} < i < 30^{\circ}$  give rise to the greatest variation in particle fluxes along the orbital path, while inclinations greater than  $60^{\circ}$  see an almost constant level of radiation. Variations with altitude are most pronounced within the LEO range, and the greatest threat within this range is the South Atlantic Anomaly (SAA) [12, pp. 2-3].

The specific effects that radiation has on electronic devices will be discussed in later sections, with particular emphasis on power MOSFETs due to their likelihood of being a single point of failure within the system.

#### 2.2.2 Temperature Variations

The absence, or at least near-absence, of gasses within the space environment causes objects to experience extreme temperature fluctuations; when exposed to the sun, the object's temperature will rise rapidly and, when in shadow, will radiate its heat back into space. Larger satellites will generally have advanced active thermal control systems, including heaters and radiators, to precisely regulate spacecraft temperature. In contrast however, CubeSats will typically rely on innovative thermal design using insulation and other techniques that keep the internal components within a range of  $-30-+30^{\circ}$ C [2, pp. 685-690] [2, pp. 809-810] [13]. Thermal design is separate from the design of the EPS and other payloads however and its presence, and thus a suitable thermal environment, will be assumed.

Solar panels will almost always cover the outer surface of the six CubeSat facets and thus form the thermal boundary between the satellite and the environment [2, pp. 805-807] [14]. Although reports differ slightly on the temperatures seen by body-mounted solar panels, the fluctuations are in the range of -80–+100°C, with the extremes seen at the end and beginning of the eclipse period respectively [2, p. 645] [14]. The effect of these fluctuations, and implications for the EPS, will be discussed in subsequent sections.

#### 2.2.3 Solar Strength

The solar constant is a level of solar irradiance (power per unit area, denoted  $E_e$ ) equal to 1368 W/m<sup>2</sup>; this is the amount of incident solar power received by a surface, perpendicular to the sun line<sup>1</sup>, at the top of Earth's atmosphere [2]. Solar radiation power decreases with the inverse-square law, and is the reason why spacecraft heading towards the outer solar system typically do not rely on solar energy to power their systems.

In terms of solar panels and a fixed solar irradiance, the effective panel area is reduced by the angle that it makes with the sun line. This relationship closely

<sup>&</sup>lt;sup>1</sup>The  $Sun \ line$  is an imaginary line from the object of interest to the Sun.

Figure 2.2: Diagram depicting the geometry of the Sun-Earth-satellite system. Adapted from [15, p. 17].

follows the cosine law [15, p. 22], giving

$$E_{effective} \approx E_e \cos\theta \tag{2.1}$$

For  $\theta > 80^{\circ}$  however, the panel should not be expected to generate any usable power [15, p. 112].

#### 2.2.4 Orbital Implications

The specific orbital path that a spacecraft takes through the atmosphere affects not only the radiation environment it will experience, but also the availability of sunlight. While the angle  $\theta$  in (2.1) refers to the angle between a given surface (ie. a solar panel) and the sun line, a further angle exists — the beta angle — that describes the angle that the Sun-Earth line makes with the orbital plane [15, p. 19]. This angle varies seasonally in a range given by  $\beta = \pm (i + \gamma)$ , where *i* is the orbit inclination and  $\gamma$  the angle between the sunline and ecliptic plane (23.45°). These angles are shown in Fig. 2.2. Given a beta angle, the percentage of the eclipse period of the entire orbital period (for a circular orbit) can be determined by [16]

#### 2.2. THE SPACE ENVIRONMENT

$$f_e = \frac{1}{\pi} \arccos\left\{\frac{\sqrt{h^2 + 2R_E h}}{(R_E + h)\cos\beta}\right\}$$

(2.2)

where h is the orbit altitude and  $R_E$  the radius of the Earth. Fig. 2.3 shows the variation in percentage with the beta angle. Note that this is for an altitude of 400 km; it is not representative of any particular mission, but it can be seen that the eclipse period can vary from 0% to around 40% of the orbital period.

The orbital inclination will affect the average eclipse time, and thus the anticipated orbit is a crucial consideration when designing a spacecraft's power system. Although such design is performed only when sizing the solar panels and energy storage in order to fulfil a particular mission's power requirements, this emphasises the need for flexibility in terms of power capabilities.

Figure 2.3: Variation in a spacecraft's eclipse period with beta angle at a 400 km altitude.

### 2.3 Photovoltaic Cells

Photovoltaic cells, or solar cells, generate the power for the vast majority of satellites. Their simplicity, reliability and relative low cost make them ideal for a wide range of spacecraft. While much of this section will be of more concern to a mission designer — they choose the types of panels to be used — the data will be important when simulating the EPS's performance in a typical environment and understanding the inputs that the EPS can expect.

#### 2.3.1 Solar Cell Fundamentals

Cells are named and categorised according to the semiconductor material used, with materials differing in the portion of the Electro-magnetic (EM) spectrum that they absorb. In order to convert as much solar radiation as possible, the material should realistically absorb the entire visible, and part of the Infrared (IR), range. By combining two or more semiconductor material layers within a cell, the cell's EM absorption range can be increased; these are known as *multi-junction* cells, due to the multiple P-N junctions now present within the cell [17]. The inherent added complexity in manufacturing multi-junction cells makes them significantly more expensive than their single-junction counterparts; however, they have found wide use in space applications where a high performance-to-cost ratio is justified through a superior power-to-weight ratio [2]. Degradation of cells from the radiation they are exposed to is also of concern, especially in the space environment.

The efficiency of a cell is an important metric that relates to the percentage of the incident solar energy it can convert into electrical energy. Specifically, it refers to the cell's output power when exposed to  $1368 \text{ W/m}^2$  (the solar constant). In practice however, a cell is not exposed to these conditions and will rather receive a fraction of this: *irradiance* is a measure of actual solar energy striking a given area per unit time. The amount of power generated by the cell will increase as irradiance increases [18].

Each cell develops a potential of between 0.5–1 V under open-circuit  $(V_{oc})$  conditions, and can output in the order of tens of milliamps when short-circuited  $(I_{sc})$ . While the amount of current is useful, the voltage may be inadequate for the major-

| Parameter | Temperature (°C) | 1U Module          |

|-----------|------------------|--------------------|

| $V_{oc}$  | -40              | 6.13 V             |

| $V_{mpp}$ | -40              | $5.58 \mathrm{~V}$ |

| $V_{mpp}$ | +80              | $4.02 \mathrm{V}$  |

| $V_{mpp}$ | +28              | 4.70 V             |

| $P_{mpp}$ | -40              | $2.46 \mathrm{W}$  |

| $P_{mpp}$ | +80              | $1.79 \mathrm{W}$  |

| $P_{mpp}$ | +28              | $2.08 \mathrm{W}$  |

Table 2.1: Beginning-of-Life (BOL) specifications for the Clyde Space 1U solar panel. Data from [23].

ity of applications. Thus, it is common for cells to be connected in series, known as *strings*, which can then be paralleled together to form a *module* [19, 2]. It is common amongst the literature to see nanosatellite applications using module configurations with  $V_{oc} = 5$  V and  $I_{sc} \approx 500$  mA.

#### 2.3.2 Use On Satellites

Solar cells have been employed to provide power to satellites since the fourth successful satellite ever launched. While the first three, *Sputnik 1 and 2*, and the USA's *Explorer 1* relied on chemical batteries that ran flat after a few months, the USA's *Vanguard 1 (TV4)* contained a solar-powered transmitter that allowed transmissions to continue for a further six years [20, pg. 9] [21].

With the aforementioned importance placed on the power-to-weight ratio (cost a relatively insignificant factor), along with the need to have good endurance in space's radiation environment, Gallium Arsenide (GaAs)-based cells have found themselves the standard amongst the majority of space applications [2, pp. 643-644] [22].

Triple-junction GaAs cells, consisting of wafers of Indium gallium phosphide (In-GaP), Indium gallium arsenide (InGaAs) and Germanium (Ge), have efficiencies approaching 30% [2, p. 645] [19]. Radiation exposure in the upper atmosphere causes a 15% reduction in output power over a span of up to 33 years, with other commercially-available cells seeing the same degradation over a period of approximately ten years [2, p. 645].

The Beginning-of-Life (BOL) properties for Clyde Space solar modules are listed in Table 2.1. These modules are commonly used on CubeSats, and in particular for local CubeSat missions.

#### 2.3.3 I-V Curve

A solar cell can be approximated by a current source in parallel with a diode, along with a couple of parasitic elements. Fig. 2.4 gives the equivalent circuit of a solar cell. The model contains an ideal current source producing the *photocurrent*  $(I_L)$ , a parallel diode, a parallel shunt resistance  $R_{sh}$  and a series resistance  $R_s$  [24].

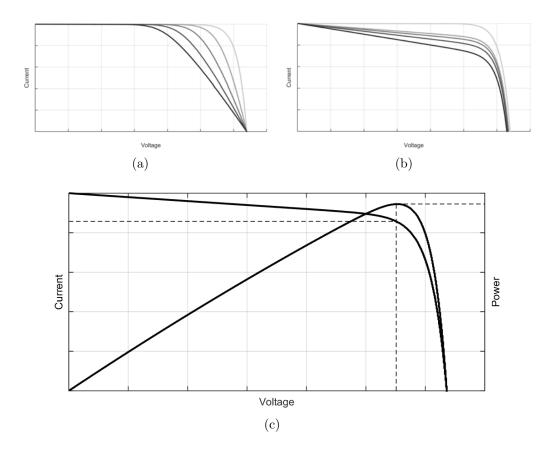

The diode is characteristic of the P-N structure of the cell, while the series resistance models losses from the transfer of current from the cell material to the electrical contacts. The series resistance also includes resistive losses through the contacts themselves, and the shunt resistance models the leakage current within the cell. Variations in these parameters give rise to the current-vs-voltage curves in Fig. 2.5 [19]. The magnitude of the photocurrent is proportional to irradiance.

It is clear from the shape of the I-V curve in Fig. 2.5 that the power extracted from the cell will vary depending on the load voltage, V, and the corresponding current, I, drawn. The combination of V and I is known as the *operating point* of the cell/module, with maximum power available when the operating point is such that  $V \times I$  is maximal. This point is known as the *global maximum*, and will be discussed further in Sec. 2.3.5.

Partial shading of panels can cause multiple *local maxima* that makes finding the global maximum more complex. In the context of a CubeSat, such partial shading

Figure 2.4: Equivalent circuit of a solar cell.

#### 2.3. PHOTOVOLTAIC CELLS

Figure 2.5: Plots showing the variations in a solar cell's I-V curve with varying cell parameters. (a) Lines darken with increasing  $R_s (R_{sh} \to \infty)$ , (b) lines darken with decreasing  $R_{sh} (R_s = 0)$ , and (c) a typical cell's I-V and corresponding P-V curve at a specified irradiance.

may be caused by deployable panels, antennae and/or external sensors for scientific experiments, that cast shadows on the body of the satellite.

#### 2.3.4 Temperature Variation

Irradiance is not the only factor influencing the photocurrent generated by a cell, with environmental conditions also having a significant effect. A change in temperature of the cell or panel can have three effects on the I-V curve, namely [2]:

- A scaling of the curve along the current axis;

- A translation of the curve along the voltage axis; and

- A change in the roundness of the knee region.

The extent to which these affect the output depend upon a cell's *temperature coefficient* which is characteristic of the type of cell and the array configuration; however, an increase in temperature will always reduce cell performance [2, p. 645] [24].

#### 2.3.5 Maximum Power Point Tracking

The non-linear I-V curve seen in Fig. 2.5 describes a power curve that will have a "peak" that corresponds to the knee of the I-V curve. Fig. 2.5c shows the power curve overlaid over a typical I-V curve; such a characteristic has the implication that, in order to extract the maximum possible power from a panel, the operating point needs to be set to the appropriate voltage,  $V_{mpp}$ , and corresponding current,  $I_{mpp}$ .

For an unobstructed panel, the position of the global maximum  $(V_{mpp})$  stays roughly proportional to  $V_{oc}$  with changes in irradiance. The introduction of environment effects however, such as variations in temperature and non-uniform irradiance, causes the  $V_{mpp}/V_{oc}$  relationship to deviate from proportionality [18, 25]. Thus, while simple enough under constant operating conditions, in practice, this task of choosing and/or finding the optimal operating point becomes more complex. A Maximum Power Point Tracking (MPPT) technique is typically employed, the aim of which is maintaining a panel voltage that gives maximum power output.

When used in conjunction with batteries however, a simpler technique is connecting the panel directly to a regulated (or battery) bus, known as *direct energy transfer*. This technique minimises losses by avoiding an intermediate DC-DC converter (inherent to MPPT implementations), but the panel will almost always be operating sub-optimally if environmental conditions are constantly changing. Because the panels will either be operating at the battery voltage (battery bus topology) or a predetermined bus voltage (regulated bus topology), the panels will need to be sized to output this voltage at minimum power output.

To maintain this bus voltage, power will need to be shunted off at all other times. While both methods are ineffective in LEO with large and regular temperature swings, these topologies remain popular in systems designed for geosynchronous orbits where panels can be sized for a fairly-constant equilibrium temperature [26]. Given this inefficiency, the need for active MPPT presents itself. There exist a number of different methods and/or techniques; some of these are in widespread use, but each are suited to different applications and the relevant ones will be briefly discussed below. In addition to these 'standard' techniques, many authors have proposed variations on these with some of particular interest.

#### **Constant Voltage**

Simplest of the MPPT methods is the Constant Voltage (CV) method, which maintains a fixed panel voltage — usually some constant factor of the open-circuit voltage — such that:

$$V_{mmp} = kV_{oc} \tag{2.3}$$

By briefly interrupting the load  $V_{oc}$  can be measured, with the load then reconnected at the calculated  $V_{mpp}$ . While being very fast and simple to implement, the calculated operating point is approximate and does not factor in environmental conditions as previously discussed [18]. Constant Current (CC) is a similar method, although based on the relationship between  $I_{mpp}$  and  $I_{oc}$ .

Both of these methods suffer from the same disadvantage in that the load is periodically interrupted while  $V_{oc}$  is taken. If batteries are present this is usually not a problem but, if not, and including when the batteries have reached their End-of-Life (EOL) and can no longer hold charge, this would cause subsystems to continuously reset.

#### Perturb and Observe

A more robust technique calculates the panel's output power and then adjusts, or steps, the panel's operating voltage. The direction of the step is based upon the calculated power before the previous step — if output power is increasing, the direction remains unchanged; if power is decreasing, the direction is reversed. Known as the *perturb and observe* (P&O) method, its popularity has been attributed to its ease of implementation and relative low cost [27]. Similar to P&O is the *hill*

*climbing* method that, instead of adjusting the panel's operating voltage, adjusts the duty cycle of a DC-DC converter, thereby perturbing the current drawn from the array [28].

A fundamental drawback of this technique is the inherent oscillations around the peak power point [28]. To counter this, a variable-size step can be used that reduces the perturbations around the peak; such a method is proposed by [27]. Rapidly-changing levels of irradiance in certain applications will also pose a limitation, as discussed by [27], who goes on to reference proposed counter-measures including an optimised (or simply high) sampling rate, with a weighted comparison between multiple power readings. In its basic form, the technique can also suffer from becoming stuck on a local power maxima.

#### **Incremental Conductance**

The incremental conductance (IncCond) method exploits the shape of the V-P curve and the fact that the slope is positive for  $V < V_{mpp}$ , negative for  $V > V_{mpp}$  and zero for  $V = V_{mpp}$ . Given the instantaneous panel parameters I and V, along with their time-derivatives  $\Delta I$  and  $\Delta V$ , the derivative of interest  ${}^{dP}/{}_{dV}$  can be re-written in terms of said parameters and subsequently interpreted as [28]:

$$\begin{cases} \Delta I/\Delta V = -I/V & \text{at MPP} \\ \Delta I/\Delta V > -I/V & \text{left of MPP} \\ \Delta I/\Delta V < -I/V & \text{right of MPP} \end{cases}$$

(2.4)

For sufficiently-small increments, the inherent oscillations of the P&O method can be avoided by maintaining the operating point when  $\Delta I = 0$ . However, small increments subject the method to similar performance limitations in rapidly-changing conditions as was described for P&O. Esram [28] notes proposed implementations using a CV method to initially approximate the operating point that largely avoid these limitations.

#### 2.3. PHOTOVOLTAIC CELLS

#### Other Methods

Fuzzy logic-based and neural network controllers have also been seen in implementations; however, these controllers require complex design with parameters that are closely linked to the system configuration [28]. With a flexible and adaptive system the goal of this thesis, these methods will not be considered.

## 2.3.6 MPPT Implementations

With active MPPT, the operating voltage of the panels and of the system will differ, and thus a DC-DC converter is needed. This gives rise to two control loops, one controlling the operating point of the converter that maintains a fixed output current or voltage, and another loop controlling the operating point of the panel. Seeing that the converter is adjusting its duty cycle in order to maintain the desired output, it is fundamentally varying the current drawn from the input.

The voltage-current curve seen in Fig. 2.5 shows a steep drop in voltage as current increases past the knee. This suggests that unless fine control is available, the input voltage to the converter may suddenly and/or unexpectedly drop below its minimum operating voltage. In this case, the system may become unstable: as the converter shuts off, input voltage will increase, allowing the converter to function once again, but then repeating the cycle. This would result is oscillations around this point that may or may not reach some sort of equilibrium. For this reason, care should be taken to avoid such a situation.

# 2.4 Energy Storage

The *specific energy* of an energy storage medium refers to its energy per unit mass; this is an important metric in satellite applications where mass is a critical consideration. Energy density — the energy per unit volume — should also be considered, as space is also a crucial constraint.

The energy storage capacity of a given medium will inevitably diminish over time, with capacity degradation exacerbated through varying factors that depend upon the medium. *Cycle life* is a characteristic that is thus also important, and refers to the number of charge/discharge cycles the medium can sustain with a capacity that is useful to the system [29].

## 2.4.1 Battery Storage

Batteries are characterised by the electrochemical process that takes place during the storage and release of electrical energy. They are a combination of one or more (fundamental) *cells* — each cell consisting of two electrodes surrounded by an electrolyte — and can have varying terminal voltages or capacities by connecting cells together in series or parallel respectively [29].

Various different combinations of chemicals can be employed, and the specific combination of these chemicals is known as the cell or battery's *chemistry*. In terms of rechargeable batteries, lead-acid, nickel-based and lithium-based chemistries are currently prevalent with each suited to different applications. Lead-acid, nickelbased and lithium-based cells have specific energies around 30 Wh/kg, 50–80 Wh/kg and 100–150 Wh/kg respectively; from this metric, it is obvious why lithiumbased batteries, or more specifically lithium-ion batteries, seem to have dominated rechargeable applications in recent times. While lead-acid batteries have a good cycle life (1200–1800 cycles is typical [29]), their low energy density does not make them feasible for space- or weight-constrained applications.

Before the advancements in Li-Ion batteries in the late 1990s, Nickel-Cadmium (NiCd) (pre-1980s) and Nickel Hydrogen (NiH<sub>2</sub>) (1980s-1990s) were the predominant battery types used on satellites due to their comparatively-long cycle life

#### 2.4. ENERGY STORAGE

(> 1000 cycles), good performance at low temperatures and general ruggedness [2, pp. 650-651]. However, once Li-Ion batteries became more widespread and reliable, their far-superior energy density quickly made them an attractive replacement. Indeed, almost all the literature points to the use of Li-Ion batteries, with [2] describing them in 2011 as likely to become the preferred rechargeable battery for all spacecraft missions.

Li-Ion batteries have a subset type known as Lithium-Ion-Polymer, often abbreviated to Lithium-Polymer and LiPo. These employ a variation on the electrolyte used and the construction of the battery. From the clear advantages of lithium batteries over other types, only Li-Ion and LiPo batteries will be considered.

#### Lithium-Ion

Li-Ion batteries have a nominal terminal voltage of 3.7 V and can typically be charged to a maximum of 4.2 V. Over-charging them, allowing them to discharge too deeply or operation at high temperatures severely affects their ageing process. However, these limitations are overshadowed by their high energy density and a lifetime upwards of 1500 cycles should conservative operating conditions be maintained [2, 29]. Furthermore, a protection circuit is often built into the battery pack to ensure safe operating conditions [29].

In terms of charging, a CC/CV profile is required that sees the charging current taper off at a pre-determined float voltage. There are many ICs available from manufacturers such as Texas Instruments and Linear Technology that safely manage the charging of this chemistry. Note that Li-Ion is used here as an umbrella term for various differing Li-Ion technologies such as Lithium Manganese Oxide (LiMn<sub>2</sub>O<sub>4</sub>) and Lithium Iron Phosphate (LiFePO<sub>4</sub>).

#### Lithium-Polymer

While there are chemical differences between LiPo and Li-Ion cells, one of the major and relevant differentiating factors between the two is in the battery's construction: very thin cells, a result of the polymer technology, allow for thin, flat batteries, as well as a battery moulded to a very specific shape. While this can be a major advantage in certain applications, the chemical differences result in a cycle life, energy density and operating-conditions range that is slightly lower than that of Li-Ion batteries [29]. Furthermore, test results of a typical CubeSat LiPo battery that are included in [30] show them to have a significantly higher Equivalent Series Resistance (ESR) than that of a tested Li-Ion cell. This will have an impact upon the cell's ability to deliver high-current pulses.

That being said, *Clyde Space* seem to have found success in LiPo batteries with LiPo the only energy storage medium used across their various product offerings [1]. The popularity of Clyde Space's EPSs is evident amongst the reviewed CubeSat missions, although there is little independent data available on their success and/or performance over the full length of successful missions.

#### Cell Combinations & Charge Equalisation

To increase the storage capacity of a battery system, multiple batteries can be combined in series and/or parallel. However, variations within each battery mean that some form of charging regulator should be present to ensure each battery is charged correctly: Li-Ion batteries in particular are highly sensitive to over- and under-discharge which can lead to catastrophic failure [31].

In both series and parallel combinations, individual cells can have unequal terminal voltages as a result of variations in internal resistances and State of Charges (SOCs), as well as differences in the ambient temperature gradient during charge/dischange and natural age-induced degradation [31].

In a series combination, unequal terminal voltages can cause a cell to be overcharged if it tapers off at a voltage lower than the other(s). A cell could also be overdischarged if it was initially charged to a lower SOC than the other(s) [31]. To avoid damage to cells in this configuration, cell balancing circuitry (or a cell balancer IC) is usually used that ensures charge is equally distributed amongst mismatched cells.

Although careful matching of cells — in terms of SOC and other characteristics — can mostly avoid these complications, it does not mitigate the effect of variations in natural ageing, and slight temperature variations over thousands of cycles. Proper balancing of cells also contributes to improving their useful life [31].

# 2.4.2 Supercapacitors

Supercapacitors can be thought of as occupying the space between capacitors and rechargeable batteries; with energy densities in the range of 0.5–15 Wh/kg, they can be charged and discharged at extremely high rates while being able to withstand  $\gg 100\ 000$  charge cycles [29, 32]. Characterised by capacitances in the order of 1000 F, supercapacitors are however limited to terminal voltages of around one to three volts. Placed in series though, a more useful terminal voltage can be achieved and, as opposed to batteries, supercapacitors can be cycled through a 100% Depth of Discharge (DOD).

The need for the rapid charge and discharge of energy in hybrid vehicles has seen much development of supercapacitor technology in recent years, as evidenced by the abundant literature on the topic. They have also found use in space applications with the European Space Agency and NASA both investigating their applicability to space EPSs over the past decade [33, 34]. Barde [34] suggests that supercapacitors are however more suited to spacecraft pyrotechnics (burning of deployables' fuses), and assisting in power averaging for payloads that have large differences between their peak and average power requirements (e.g. radar and telecommunications payloads).

#### Flight Heritage

There appears to be little data on the actual performance of supercapacitors in space applications, with most of the available literature addressing their *potential* use in satellite EPSs. *TurkSat-3USat* was a 3U CubeSat built by the Istanbul Technical University that incorporated both a COTS EPS from Clyde Space and an EPS with supercapacitors as the storage medium, developed in-house, serving as a backup [35]. Unfortunately, reports suggest that the satellite went silent after one day of successful operation with no indication as to the cause of the failure [36].

A hybrid Li-ion and supercapacitor system for small satellites is also proposed by [30] as part of an investigation into its feasibility for deep-space CubeSat missions. After ground-based testing, they conclude that although no significant performance gains in energy storage are achieved over a standalone Li-ion battery system, there is a substantial peak current capability. This increase is attributed to the lower

#### 2.5. ELECTRONIC DESIGN AND FAILURE ANALYSIS

impedance of the hybrid system, a result of supercapacitors having a much lower ESR than Li-Ion batteries; their included test data shows, at a temperature of  $-40^{\circ}$ C, ESRs of 10 m $\Omega$ , 100 m $\Omega$  and 1000 m $\Omega$  for their supercapacitor assembly, a standalone Li-Ion, and a standalone LiPo battery respectively.

# 2.5 Electronic Design and Failure Analysis

The EPS is known to be one of the leading causes of spacecraft failures: while Wertz [2, p. 807] suggests that the EPS is the most common system in a CubeSat to fail, Tafazoli [37], in a study of in-orbit spacecraft failures, concludes that the power system accounts for 27% of all spacecraft failures<sup>2</sup>. This is behind a 32% failure rate of the Attitude and Orbital Control System (AOCS). However, seeing that a spacecraft may well continue to operate with the loss of the AOCS albeit with reduced capabilities, a loss of the EPS would most certainly result in loss of the mission, and could thus indeed be argued to be the leading cause of satellite failure.

Tafazoli's study reviews data from 156 in-orbit spacecraft failures (i.e. discounting launch failures) that occurred between 1980 and 2005, and includes a few interesting statistics on EPS-related failures: In addition to a 27% failure rate of power systems, 45% of all failures are electronic-related, with a less significant 6% related to software errors. Software errors include erroneous commands sent to the spacecraft, along with programming errors within on-board software. Another significant statistic is that 48% of failures occur within the first year of operation which he postulates to be a result of inadequate ground testing. Finally, failure of the solar array is attributed to 49% of power system failures, and 22% a result of battery failure. Noted however is that solar array failure is predominantly due to failed deployment of external panels (arguably a mechanical fault rather than electrical), thus making the expected failure rate for body-mounted panels far lower.

These statistics highlight the importance of careful electronic design and perhaps a greater emphasis on reliability and redundancy than is currently practised.

$<sup>^{2}\</sup>mathrm{It}$  should be noted that CubeSats started to appear only towards the end of this study (1980–2005).

## 2.5.1 Electronics Failures in Spacecraft

Failure of actual electronic components is a subset of electrical failures described above and deserves a closer analysis. In terms of the actual failure rate of individual parts, Sarsfield [38] states, in 1998, that component quality issues account for 11% of spacecraft failures. While outdated, what is notable is his assessment of the decline of this figure, down from 26%, over the period from the 1970s to the 1990s. Of more interest, however, is that the failure rate of standard commercial components/parts has reduced so dramatically, that it appears to be on-par with so-called 'space-rated' components [38, pp. 135-141]. Note that this is not referring to radiation-hardened versus unhardened parts, but rather the grade and screening of standard parts.

Nevertheless, it is evident that the selection of high-quality parts is paramount to improving the survivability of systems: even if standard-grade parts have a comparable overall failure rate to those that are mil-spec or even space-grade, the "time to first failure" is far more important than the Mean Time Between Failures (MTBF) [38, pp. 135-141].

The popularity of using COTS components in harsh operating environments with a high degree of risk could be linked to the creation, in 2005, of the Aerospace Qualified Electronic Component Standard (ANSI/GEIA STD-0002-1); this standard qualifies components to meet minimum requirements for use in aerospace and other rugged operating environments. Although adoption of the standard appears limited, Texas Instruments offers a so-called "Enhanced Products" range that qualifies components to meet this standard [39].

# 2.5.2 Radiation Effects

There are two separate radiation-induced phenomena that are spoken of, those being the prolonged effect of an electronic device within a radiation environment, and the direct effect that a single, highly-energetic particle can have on a device. The former is known as the Total Ionising Dose (TID), while the latter is referred to as a Single Event Effect (SEE) [12, 40].

Single event effects or phenomena manifest themselves primarily as Single Event Upsets (SEUs), Single Event Latchup (SEL) and Single Event Burnout (SEB) [2,

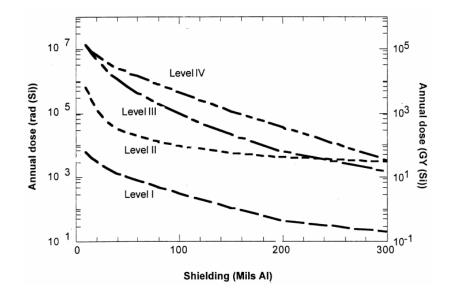

Figure 2.6: Annual total dose versus shielding for different qualification levels. Taken from [41].

p. 137]. SEUs are discussed within this section in relation to digital memory, while SELs and SEBs are discussed later on in their effect on MOSFET devices.

#### Survivability

An electronic device's survivability in a radiation environment is dictated by its radiation hardness, quantified by a total dose rating (typically measured in the non-SI unit rad(x) or krad(x), where x is the material of interest, usually Silicon (Si)).

Although outdated, the IEEE Standard for Spaceborne Computer Modules [41] provides useful data on anticipated total dose levels as a function of shielding, expressed as an effective thickness of aluminium in the units mil. Avery *et. al.* [42] assume an effective shielding of 10 mil for a CubeSat with a weight-optimised structure that offers little shielding. Fig. 2.6 shows this graph of annual dose vs. shielding thickness for various qualification levels, with level I corresponding to a satellite in LEO at an altitude of < 500 km. The annual dose is stated to include contributions from all sources<sup>3</sup>, made conservative through adding two times the standard deviation in the data and a safety margin of two.

$<sup>^{3}</sup>$ See Sec. 2.2.1

#### 2.5. ELECTRONIC DESIGN AND FAILURE ANALYSIS

From Fig. 2.6, a total dose of 4 krad(Si)/yr should be allowed for, giving 10 krad(Si) as a good target for a typical CubeSat mission. This data also shows the exponential effect that shielding has on minimising the total dose requirements; however, excessive shielding is usually not feasible on a CubeSat with strict weight requirements. Furthermore, shielding is ineffective at blocking the very-high energy particles that cause SEEs [43] and thus the effects of radiation can never be entirely negated.

#### Single Event Upsets

SEUs correspond to a change in memory state in logic devices, also known as a "bit-flip". This phenomenon is most commonly associated with RAM (both DRAM and SRAM), but is also seen in non-volatile technologies such as flash and EEPROM [2, p. 608] [44]. SEUs are "soft errors" and do not result in permanent damage; however, the detection of errors is important to prevent runaway code and/or invalid control outputs.

The use of Error Correction and Detection (EDAC) is a common practice for mitigating the effects of SEUs. In microcontrollers, an EDAC implementation commonly relies upon Error Correcting Code (ECC), stored alongside blocks of data, that enable the detection and, potentially, correction of bit errors. The length of the ECC determines how many bit errors can be reliably detected, but one fewer error can ever be corrected than detected: eg., commonly seen is Single Error Correction, Double Error Detection (SEC-DED).

When a hardware EDAC is not available, there exist techniques to implement an EDAC in software (see eg. [45]). Hardware implementations are by far preferable however for reasons of complexity and efficiency [2, p. 609]. Furthermore, software EDACs will usually be unable to function on flash memories: seeing that micro-controllers would typically run the EDAC code out of flash, the architecture would need to allow for concurrent flash read and writes, or read-while-writes (RWW).

# 2.5.3 Points of Failure

Analysing the reliability of a system typically involves identifying single points of failure; although any component or aspect of a system *can* fail, it may not necessarily cause entire system failure. These failure points usually find themselves on single-string elements, those being components or subsystems that are relied upon for useful operation of the system. The concept of redundant strings then emerges, in which elements are placed in parallel (not necessarily in the electrical sense) to ensure backup functionality exists. Consideration does, however, have to be given to ensure failed redundant strings cannot have adverse effects on the remaining strings, thereby negating their purpose.

In addition to complete failure of a system element, partial failures may also occur. These might not cause direct failure of the system, but the combination of multiple partial failures, occurring over time, may indeed reduce system capabilities to the extent that it can no longer operate usefully.

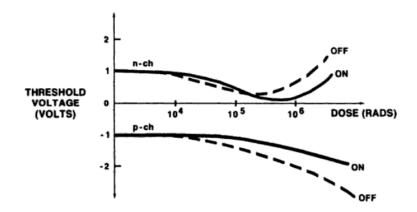

# 2.6 MOSFETs in a Radiation Environment

Metal Oxide Field-Effect Transistors (MOSFETs) are universally used in power electronics and other switching applications; their high voltage and current-carrying abilities combined with very low 'on' resistance makes them close to ideal switches. Their use is further inherent to all CMOS ICs, encompassing practically every electronic device. However, their inherent semiconductor structure — that of layers of n- and p-type substrates — lends itself to radiation-induced effects: ionised particles, entering the device structure, mobilise electrons and create so-called 'holes' that can not only cause unintended operation, but also permanent damage [46].

The TID effects and SEEs cause different failure modes; while the full physics behind the interaction of ionised particles with the internal semiconductors is outside the scope of this work, a sufficient overview of the aforementioned failure modes, in order to make suitable design choices and predict system failures, is presented here.

## 2.6.1 Structure Types

The first MOSFETs were very low current devices, running in the order of tens of milliamps. It was only in the late 1970s that an introduction of a different internal structure allowed for MOSFETs with high current and voltage ratings, dubbed "power MOSFETs" [47].

A vertical structure characterised the first power MOSFETs (known as VDMOS or simply DMOS), which was a change from the lateral structure of the low-power MOSFETs. Different structure designs have subsequently evolved, with the most common being trench MOSFETs (UMOS or TMOS) and HEXFETs [47, p.159].

Galloway [48], in his review of radiation-induced degradation on UMOS transistors, notes similar failures to those of VMOS devices. He does however caution that enough is not yet known and further experimentation should be done. While this topic is not investigated here, this remains an interesting section to be explored in order to maximise reliability from non-hardened devices through choice of device structure<sup>4</sup>.

## 2.6.2 Single Event Effects

MOSFET-related SEEs are almost always destructive events, occurring at any time within a system [43]. Of interest to a power subsystem are SEL, SEB and Single Event Gate Rupture (SEGR) effects; while SEL affects CMOS devices, SEB affects n-channel power MOSFETs (biased off) and SEGR affects both n- and p-channel power MOSFETs [43, 49, 50]. The inevitable use of these devices motivates a brief look at these effects and corresponding mitigation strategies.

#### Single Event Burnout

SEB is a catastrophic failure mode that sees a permanent short circuit forming between the drain and source. A heavy ion entering the device through the source (drain) of an n-channel (p-channel) MOSFET generates a transient current that

<sup>&</sup>lt;sup>4</sup>This is further corroborated by [49] who states that failure mechanisms in MOSFETs may indeed be affected by different design, process and operating parameters.

#### 2.6. MOSFETS IN A RADIATION ENVIRONMENT

triggers the parasitic BJT within; when the device is biased off, and thus blocking a high drain-source voltage, regenerative feedback causes the BJT's collector currents to increase to the point where secondary breakdown occurs, resulting in the drain-source short circuit [50].

Although done in 1996, [50]'s review of the literature at the time indicates that there are no reports of SEB occurring in *p*-channel MOSFET's, under normal operating conditions, with others making the same conclusion [43, 51]. [50] does however suggest that SEB *may* occur in *p*-channel devices, although far less probable than that for *n*-channel devices. This paper can be referred to for the specifics behind the reasoning.