The copyright of this thesis vests in the author. No quotation from it or information derived from it is to be published without full acknowledgement of the source. The thesis is to be used for private study or non-commercial research purposes only.

Published by the University of Cape Town (UCT) in terms of the non-exclusive license granted to UCT by the author.

# SIMULATING RAID STORAGE SYSTEMS FOR PERFORMANCE ANALYSIS

A DISSERTATION SUBMITTED TO THE DEPARTMENT OF COMPUTER SCIENCE, FACULTY OF SCIENCE AT THE UNIVERSITY OF CAPE TOWN IN FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE

By Sameshan Perumal November 2007

> Supervised by Dr P. S. Kritzinger

© Copyright 2007 by Sameshan Perumal

# Acknowledgements

To my family, Mom, Delisha and Marlan, for believing in me. To my friends for their valiant efforts at keeping me sane. To Thamaray, for being there.

University

i

### Abstract

Redundant Array of Independent Disks (RAID) provides an inexpensive, fault-tolerant storage solution using commodity hard-drives. RAID storage systems have recently surged in popularity amongst enterprise clients, as they provide economical, scalable, high-performance solutions for their storage requirements.

The performance of RAID systems is negatively affected by the overhead required to manage and access multiple drives, and multiple disk failures can result in data loss. As RAID has developed, various improvements have been devised by both academia and business to address these short-comings. These improvements have suggested improved architectures to increase performance and new coding techniques to protect against data loss in the case of drive failure.

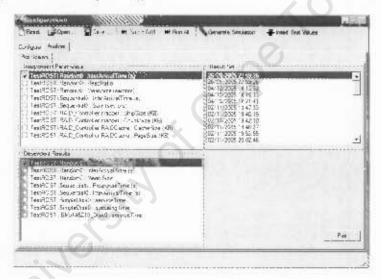

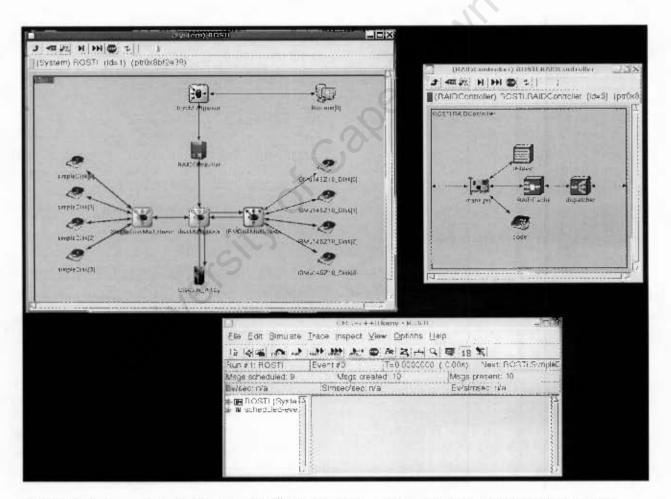

Evaluating the effect on performance of these improvements is greatly simplified by the use of discrete-event, software simulations. The RAID Operations Simulator for Testing Implementations (RÖSTI) was developed to support such simulation experiments. RÖSTI is a modular, extensible, RAID-focused simulation environment, built on the OMNet++ framework, and able to run on both the Microsoft Windows<sup>TM</sup> and GNU/Linux<sup>TM</sup> platforms.

In this environment, RAID storage systems can be modelled using the graphical tools provided by OMNet++. The RAID model adopted by RÖSTI is modular in nature, with the intention that extensions can be added transparently. The configuration of these models, once specified, is also achieved through the RÖSTI graphical user interface. The configured simulation models can then be executed, and the results analysed from within RÖSTI.

The work of Courtight et. al. [CGHZ96b] on representing RAID operations as Directed Acyclic Graphs (DAGs) served as the basis on which extensive validation of RÖSTI was performed. This validation was also extended to the various caching schemes that are implemented in RÖSTI. Test runs of the system were performed and the results compared against expectations as additional verification of RÖSTI.

RÖSTI currently supports modelling of RAID 5, RAID 6 and SPIDRE protection schemes, as well as LRU, LFU and ARC caching schemes.

# Contents

| A | cknov          | wledgements                              | i  |

|---|----------------|------------------------------------------|----|

| 1 | Intr           | oduction                                 | 1  |

| Ι | Ba             | ckground                                 | 4  |

| 2 | $\mathbf{Red}$ | undant Array of Independent Disks (RAID) | 5  |

|   | 2.1            | Terminology                              | 5  |

|   | 2.2            | RAID Implementation                      | 6  |

|   | 2.3            | RAID Taxonomy                            | 9  |

|   | 2.4            | Issues with RAID                         | 14 |

|   | 2.5            | RAID Caching                             | 18 |

| 3 | $\mathbf{Sim}$ | ulation of Systems                       | 22 |

|   | 3.1            | Introduction                             | 22 |

|   | 3.2            | Evaluating the Benefits of Simulation    | 23 |

|   | 3.3            | Simulation Fundamentals                  | 24 |

|   | 3.4            | Developing a Simulation Study            | 32 |

|   | 3.5            | Choosing a Simulation Environment        | 33 |

| 4 | Pre            | vious Work                               | 39 |

|   | 4.1            | Measurement tools                        | 39 |

|   | 4.2            | Tools for designing RAID systems         | 41 |

|   | 4.3            | RAID performance modelling tools         | 45 |

| II | In                         | plementation                      | 51  |  |  |  |

|----|----------------------------|-----------------------------------|-----|--|--|--|

| 5  | 5 Building the Simulator   |                                   |     |  |  |  |

|    | 5.1                        | RÖSTI and IBM                     | 52  |  |  |  |

|    | 5.2                        | UML                               | 53  |  |  |  |

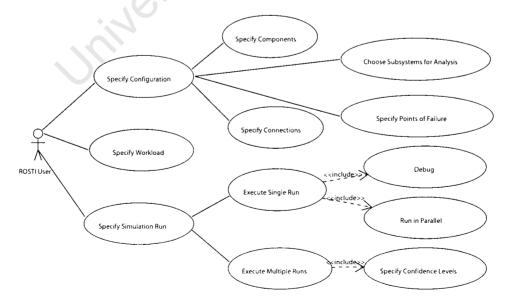

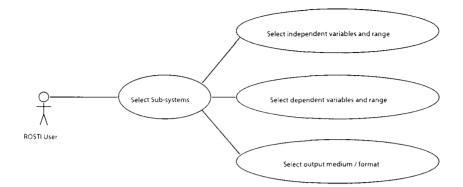

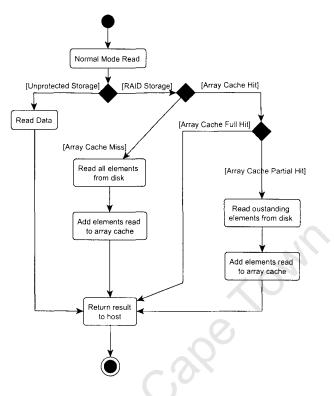

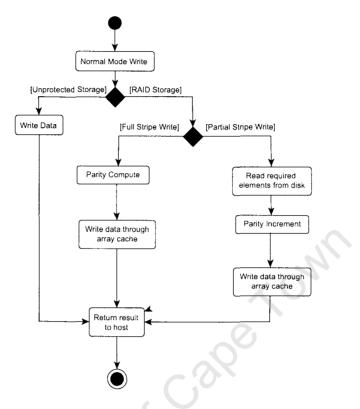

|    | 5.3                        | User Requirements Specification   | 53  |  |  |  |

|    | 5.4                        | Architecture                      | 60  |  |  |  |

|    | 5.5                        | Design and Implementation         | 70  |  |  |  |

|    | 5.6                        | Functionality                     | 74  |  |  |  |

|    | 5.7                        | Implementation Issues             | 80  |  |  |  |

| 6  | Cor                        | afiguring the simulation          | 85  |  |  |  |

|    | 6.1                        | Motivation                        |     |  |  |  |

|    | 6.2                        | Approach                          | 86  |  |  |  |

|    | 6.3                        | Implementation                    |     |  |  |  |

| 7  | Ana                        | alysing Simulation Results        | 91  |  |  |  |

|    | 7.1                        | Motivation                        | 91  |  |  |  |

|    | 7.2                        | Utilising the Partitioned Results | 91  |  |  |  |

|    | 7.3                        | Implementation                    | 92  |  |  |  |

| Π  | III Testing 95             |                                   |     |  |  |  |

| 8  | 8 Validating the Simulator |                                   |     |  |  |  |

|    | 8.1                        | Validating the Disk Models        | 96  |  |  |  |

|    | 8.2                        | Validating the Data Sources       | 96  |  |  |  |

|    | 8.3                        | Validating the RAID Controller    | 97  |  |  |  |

|    | 8.4                        | Validating Cache Operation        | 111 |  |  |  |

| 9  | Tes                        | t Case                            | 117 |  |  |  |

|    | 9.1                        | RAID Simulation Model             | 117 |  |  |  |

|    | 9.2                                                                                                                             | Workload                                                                                                                                                                             |  |

|----|---------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|    | 9.3                                                                                                                             | Disk Drives                                                                                                                                                                          |  |

|    | 9.4                                                                                                                             | Definitions                                                                                                                                                                          |  |

|    | 9.5                                                                                                                             | Simulation Expectations                                                                                                                                                              |  |

|    | 9.6                                                                                                                             | Simulation Results                                                                                                                                                                   |  |

|    | 9.7                                                                                                                             | Simulation Analysis                                                                                                                                                                  |  |

| 10 | Sum                                                                                                                             | 100                                                                                                                                                                                  |  |

| 10 |                                                                                                                                 | nmary 122                                                                                                                                                                            |  |

|    |                                                                                                                                 | Overview                                                                                                                                                                             |  |

|    |                                                                                                                                 | Outcomes                                                                                                                                                                             |  |

|    | 10.3                                                                                                                            | Future Work                                                                                                                                                                          |  |

| IV | A                                                                                                                               | ppendices 132                                                                                                                                                                        |  |

| A  | Forr                                                                                                                            | malising Controller Operation 133                                                                                                                                                    |  |

|    |                                                                                                                                 |                                                                                                                                                                                      |  |

|    | A.1                                                                                                                             | Raid Layout Specification                                                                                                                                                            |  |

|    | A.1<br>A.2                                                                                                                      | Raid Layout Specification133Specifying Protection Groups134                                                                                                                          |  |

|    |                                                                                                                                 |                                                                                                                                                                                      |  |

|    | A.2<br>A.3                                                                                                                      | Specifying Protection Groups                                                                                                                                                         |  |

| в  | A.2<br>A.3<br>A.4                                                                                                               | Specifying Protection Groups                                                                                                                                                         |  |

| В  | A.2<br>A.3<br>A.4                                                                                                               | Specifying Protection Groups    134      Deriving Array Operations    134      Correctness of Operation    134                                                                       |  |

| В  | A.2<br>A.3<br>A.4<br><b>RÖS</b>                                                                                                 | Specifying Protection Groups    134      Deriving Array Operations    134      Correctness of Operation    134      STI Messages    135                                              |  |

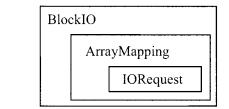

| в  | A.2<br>A.3<br>A.4<br><b>RÖS</b><br>B.1                                                                                          | Specifying Protection Groups134Deriving Array Operations134Correctness of Operation134STI Messages135IORequest135                                                                    |  |

| в  | <ul> <li>A.2</li> <li>A.3</li> <li>A.4</li> <li><b>RÖS</b></li> <li>B.1</li> <li>B.2</li> <li>B.3</li> </ul>                    | Specifying Protection Groups 134   Deriving Array Operations 134   Correctness of Operation 134   STI Messages 135   IORequest 135   IOResponse 136                                  |  |

| в  | <ul> <li>A.2</li> <li>A.3</li> <li>A.4</li> <li><b>RÖS</b></li> <li>B.1</li> <li>B.2</li> <li>B.3</li> </ul>                    | Specifying Protection Groups 134   Deriving Array Operations 134   Correctness of Operation 134   STI Messages 135   IORequest 135   IOResponse 136   ArrayMapping 136               |  |

| в  | <ul> <li>A.2</li> <li>A.3</li> <li>A.4</li> <li>RÖS</li> <li>B.1</li> <li>B.2</li> <li>B.3</li> <li>B.4</li> <li>B.5</li> </ul> | Specifying Protection Groups 134   Deriving Array Operations 134   Correctness of Operation 134   STI Messages 135   IORequest 135   IOResponse 136   ArrayMapping 136   BlockIO 137 |  |

|    | <ul> <li>A.2</li> <li>A.3</li> <li>A.4</li> <li>RÖS</li> <li>B.1</li> <li>B.2</li> <li>B.3</li> <li>B.4</li> <li>B.5</li> </ul> | Specifying Protection Groups134Deriving Array Operations134Correctness of Operation134STI Messages135IORequest135IOResponse136ArrayMapping136BlockIO137BlockIOResponse137            |  |

# Chapter 1

# Introduction

Over the recent history of computer systems, there has been a phenomenal increase in both raw processing power (as predicted by Moore's Law) and primary memory (RAM) capacity, but this has not been adequately matched by the performance of secondary memory (disk drives). Neither capacity nor transfer rates have experienced serious improvements, yet disk requirements are soon anticipated to reach PetaByte<sup>1</sup> levels [KBC<sup>+</sup>00].

Single Large Expensive Disks (SLED) have previously been the solution of choice amongst organisations with large storage requirements, as the Mean Time to Failure<sup>2</sup> (MTTF) is high, and reliability and persistence of storage is of utmost importance to most organisations. They do suffer from problems however. SLEDs are expensive and can require large amounts of power to operate. More importantly SLEDs have limited bandwidth, which means recovering a backup from tertiary storage<sup>3</sup> to secondary storage could take prohibitively long. This last factor is especially important for online applications, where constant availability is essential, and the non-accessibility of backed-up data could be crippling.

A solution to this problem is provided by the widespread availability of commodity hard disk drives for personal PCs. They offer a number of benefits: they are cheap, with a lower cost per Megabyte (MB) than SLEDs; an individual disk now has a MTTF comparable to most SLEDs; they require far less power; they conform to a uniform access standard, typically SCSI (Small Computer Systems Interface), IDE (Integrated Drive Electronics) or SATA (Serial Advanced Technology Attachment); and they have built in controller logic which performs both error detection and correction functions.

The concept of a Redundant Array of Inexpensive Disks (RAID) was introduced to harness the potential of these commodity hard drives: Patterson et. al. [PGK88] established the RAID taxonomy in 1988. RAID overcomes the capacity limitations of commodity disks by exposing an array of such low-capacity disks as a virtual SLED.

Such arrays offer flexibility over SLEDs, in that capacity can be increased incrementally, and as desired, by adding more disks to the array. Since each individual disk in a RAID system consumes little power, and the cost of replacement of a single disk is small compared to the overall cost, RAID systems have low associated running costs. Finally, given the fact that each disk in the

$<sup>^{1}1</sup>PB = (1024)^{6} B$

<sup>&</sup>lt;sup>2</sup>The average time for a single disk in a group to fail.

<sup>&</sup>lt;sup>3</sup>High capacity, low performance storage solutions, such as Tape Drives

array can perform transfers independently of the others, due to the built-in controllers, there exists the possibility of increased I/O bandwidth due to parallelism.

All these advantages are not without a significant problem: reliability. The Mean Time To Failure (MTTF) of an array of disks is inversely proportional to the number of disks in the array, given by [PGK88]:

$MTTF of RAID = \frac{MTTF of Single Disk}{Number of Disks in Array}$

To illustrate the effect of this, consider an array of 100 disks, each with a MTTF of 30 000 hours. The MTTF of any one disk in the array is then 300 hours or 12.5 days. Ensuring that data loss does not occur in a RAID is thus essential. Almost all current RAID architectures focus on preventing data loss from a single disk failure. They are generally susceptible to data loss if a second failure occurs before the first is repaired. The two main strategies employed are mirroring [BG88] and striping with parity [LKB87]. Both these approaches utilise redundancy information to achieve reliability.

The applications for RAID (Redundant Array of Independent Disks) [PGK88] in Enterprise Storage Systems (ESS) continue to grow as applications demand ever more secondary storage. New protection schemes are being used in commercial systems to meet this demand.

These schemes increase the number of disk failures that are tolerable before data loss occurs. In organisations with large arrays of disks, this is of particular importance, since the Mean Time To Failure (MTTF) of the array decreases as the number of disks increase. The increased number of disks across which data can be distributed can also improve data transfer rates for certain types of I/O operations, as well as allowing multiple operations to occur in parallel.

The benefits offered by these new schemes are offset by a number of factors: write operations take longer, since more protection information must be updated on each operation; certain schemes reduce the level of parallelism possible; a greater proportion of the available storage space is used to store protection information; rebuilding lost data after a disk failure is a longer and more complicated procedure; and the complexity of the associated controller increases, which introduces a greater possibility for errors in operation.

### Motivation

Our work here came about as a result of collaboration with the IBM Zürich Research Lab, which is involved in developing new, more effective schemes for RAID storage. These schemes aim to decrease the potential for irrecoverable data loss with a minimal increase in capacity and processing overhead. The first such scheme under development is **Sector Protection through Intra-Drive REdundancy** (SPIDRE), described in Section 2.3.6 (p. 13).

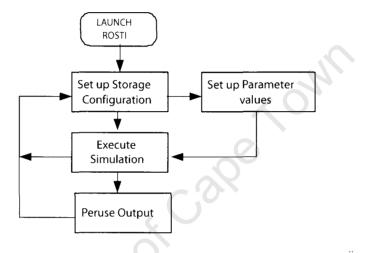

The goal of developing the **Raid Operation Simulator for Testing Implementations** (RÖSTI) was born out of the desire to implement and test the performance of these new RAID schemes using a common, extensible simulation environment. This simulator allows for advanced RAID schemes, such as those under development by IBM, to be performance tested prior to implementation, thus allowing for more cost-effective development. The extensibility of the simulator is thus essential to this goal.

Our secondary goals are to ensure that RÖSTI is configurable in a simple, graphical manner to allow inexperienced users access to its capabilities. A further goal is to assist in first-order analysis<sup>4</sup> of results produced by RÖSTI, thus allowing simulations to be fine-tuned as part of the simulation process.

### Contribution

Our contributions to the area of RAID storage system research are as follows:

- Development and validation of a RAID simulation environment (RÖSTI) that allows RAID simulation models to be specified, configured, executed and analysed. RÖSTI supports the RAID 5, RAID 6 and SPIDRE protection schemes<sup>5</sup>, and the LRU, LFU and ARC caching algorithms<sup>6</sup>. This simulation environment was further designed to be modular and extensible<sup>7</sup>.

- Provision of a Graphical User Interface (GUI) to this simulation environment, thereby allowing inexperienced users to utilise the functionality provided without requiring a detailed knowledge of the system internals<sup>8</sup>.

- Creation of a validation strategy for RAID implementations focused on high-level behaviour rather than low level implementation<sup>9</sup>. This strategy uses the extensive work done by Courtright et. al. [CGHZ96a] on formalising RAID Controller operations, and applies it to ensuring the correctness of a particular implementation.

- Outlining a possible avenue of research into a formalisation strategy for RAID Controller operations<sup>10</sup>. This strategy would allow the individual disk operations required for a given array operation to be automatically inferred from a high-level description of the RAID scheme (RAID 5, RAID 6, etc.) in use.

<sup>&</sup>lt;sup>4</sup>Initial examinations of results that are used to refine or redefine a simulation experiment.

$<sup>{}^{5}</sup>$ Section 5.6.3 (p. 78)

<sup>&</sup>lt;sup>6</sup>Section 5.6.3 (p. 79)

<sup>&</sup>lt;sup>7</sup>Section 5.4 (p. 60)

<sup>&</sup>lt;sup>8</sup>Figures 35 (p. 88), 63 (p. 118), and Chapter 7 (p. 91)

<sup>&</sup>lt;sup>9</sup>Section 8.3 (p. 97)

<sup>&</sup>lt;sup>10</sup>Appendix A (p. 133)

# Part I Background

# Chapter 2

# Redundant Array of Independent Disks (RAID)

Describing the nature of a RAID system requires the use of specialised terminology, covered in Section 2.1. These systems are composed of a number of individual components, that frequently interact in complex ways. Section 2.2 provides an overview of this aspect of RAID. A taxonomy of the various RAID schemes available is presented in Section 2.3 and their associated drawbacks are discussed in Section 2.4. Finally the issue of caching, its impact on RAID systems and an overview of some widely implemented caching policies is presented in Section 2.5.

## 2.1 Terminology

RAID technology usually requires the distribution of data across a number of disks. We define here those terms used to more clearly describe the various ways in which this can be accomplished.

|       |       |       |       |       | →<br> |

|-------|-------|-------|-------|-------|-------|

| Chunk | Chunk | Chunk | Chunk | Chunk |       |

| Chunk | Chunk | Chunk | Chunk | Chunk |       |

| Chunk | Chunk | Chunk | Chunk | Chunk |       |

| Chunk | Chunk | Chunk | Chunk | Chunk |       |

| Chunk | Chunk | Chunk | Chunk | Chunk |       |

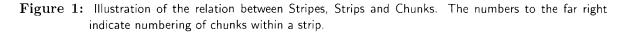

Restricting ourselves to one-dimensional arrays<sup>1</sup>, we term the ordered set of all disks participating in a RAID configuration an **Array**. Referring to Figure 1, each column (outlined in thick black) represents a single disk in the array.

<sup>&</sup>lt;sup>1</sup>See Section 2.2.4 (p. 8)

Each row represents a **Stripe**, such that a **Stripe** spans all disks in the **Array**. A **Stripe** represents the smallest unit of protection in an **Array**– any lost data within a **Stripe** can be recovered using only the surviving data within that **Stripe**.

A **Stripe** consists of a sequence of **Strips** corresponding to the disks in the **Array**. A **Strip** is the smallest unit of data that will be accessed on a disk, and the *strip size* is thus chosen to match the normal size of a physical disk sector, usually 512KB. For most common RAID schemes (RAID 1 - 5), these are the only terms that are necessary.

For more complex schemes, such as SPIDRE<sup>2</sup> and EvenOdd [BBBM94], it is necessary to introduce one additional term. Each **Strip** can be logically segmented into a contiguous series of one or more **Chunks**. A **Chunk** represents the smallest unit of data on which a RAID Controller can operate. The purpose and size of each chunk is dependent on the RAID scheme used.

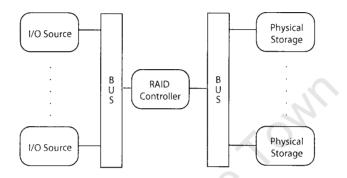

### 2.2 RAID Implementation

RAID implementations can exist in either software or hardware, with some occasional implementations using hybrid combinations. The majority of commercial implementations utilise a dedicated hardware implementation, however, since the overhead imposed on the CPU by having to handle RAID logic diminishes the performance gains of RAID significantly. The majority of such systems are connected to a single host system using either a commodity disk interface (IDE, SATA or SCSI) or enterprise level storage interfaces (Fibre Channel, iSCSI). Whichever solution is chosen, the RAID appears as a single disk to the host system which is accessed normally over the given channel.

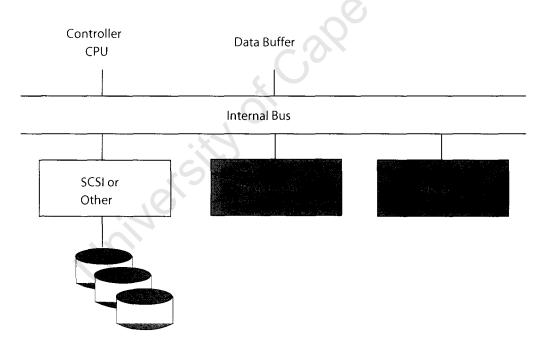

### 2.2.1 Hardware

In a hardware RAID system, all processing and management of the RAID array is offloaded to a dedicated processor in hardware, referred to as the RAID Controller. This controller performs parity checking, management of recovery from disk failures, and the physical striping of data across multiple disks. Internally, drives are attached using IDE, SATA or SCSI interfaces. Hardware solutions present the RAID array to the host system as a single disk. Configuration of various RAID parameters (such as stripe size, strip size, RAID mode) is handled by external utilities that interface with the hardware. Parallel performance of such a system is effectively equivalent to a single server, with a single large disk, serving requests from multiple clients.

### 2.2.2 Software

In a software RAID system, a software driver performs all necessary operations to treat an array of drives as a RAID. The CPU load increases because of this overhead, and can thus present a performance bottleneck in multitasking situations. Drives in the array are connected via one of the commodity disk interfaces mentioned above. The software driver allows the the Operating System to access the array as a single, large disk.

<sup>&</sup>lt;sup>2</sup>See Section 2.3.6 (p. 13)

### 2.2.3 Parallelism in RAID

Since clients are connected to the RAID via a serial access channel, parallel access by multiple clients is not explicitly supported. Some implementations offer multiple access channels, but each channel can only access a designated part of the RAID. This is achieved by partitioning the RAID and allowing each channel exclusive access to a subset of the partitions. If the partitions are on physically separate volumes, true parallel access is supported, since each channel can independently access its associated partitions as exclusive disk access is possible. If all disks are shared by all partitions, this is not possible.

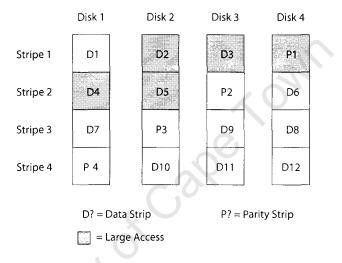

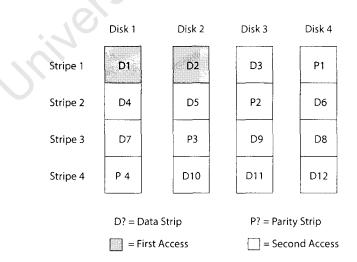

Figure 2: A single large I/O request that accesses all disks in the array. No other request can be executed while the large request is being serviced.

Figure 3: Two small I/O requests that do not require shared access to any disk, and can thus be executed in parallel.

The extent to which parallelism is possible in an array is thus primarily a question of how queued requests are scheduled to run in parallel. This can be answered by examining the nature of I/O requests presented to the system. In particular, a distinction can be made between large requests (that require access to at least a full stripe) and small requests (which require access to only a subset of strips within a stripe).

All large accesses must be performed in serial, whereas most small accesses can be parallelised. Large accesses can only be serviced one at a time, since all disks are necessarily involved in the transfer and disks are themselves serial. Hence, none of them can be used until the transfer is complete, as illustrated in Figure 2.

Small accesses, on the other hand, can be serviced in parallel if each access addresses different disks, as illustrated in Figure 3. It follows that the smaller the accesses, the greater the degree of parallelism possible, with the maximum number of simultaneous accesses determined by the number of disks in the array.

### 2.2.4 Logical to Physical Mapping

As described previously, data in RAID arrays is divided into discrete blocks (*strips*) that are then *striped* across a series of drives in the array. This striping requires a well defined system to determine where each strip will be physically stored. The only requirement of such a system is that each strip in a given stripe must be placed on physically independent disks.

Given this criteria, the most commonly used system matches the number of strips in a stripe to the number of available physical disks, as illustrated in Figure 2. This system has the advantage of requiring the minimal number of parity strips for a given array size. A significant downside, however, is that rebuild operations<sup>3</sup> on the array cannot take advantage of parallelism as each stripe reconstruction uses all disks in the array.

Figure 4: Parity Declustering mapping a logical array mapping (Figure A) to a physical array mapping (Figure B). Note that the physical independence of data and parity strips in a stripe is maintained, since each is located on an independent physical disk.

An alternate solution to this problem was presented by Holland et. al. in their work on Parity Declustering [Hol94]. In this solution, the number of disks in the array is greater than the number of strips per stripe. The array layout is then logically identical to the previous case in Figure 2. However at a physical level, the strips can be mapped to the individual disks in a variety of ways. The most straightforward of these is illustrated in Figure 4. Each disk is partitioned into a series

<sup>&</sup>lt;sup>3</sup>See Section 2.4.2 (p. 17)

of equal sized blocks, as in a normal RAID array, and the stripes are then laid out in a sequential, rotating pattern across them.

The important aspect of this layout is that related data and parity strips are still kept on separate disks, thus ensuring that the normal RAID recovery procedures can be applied. The primary advantage such a layout offers is a much higher maximum bandwidth during rebuild operations. This follows since there are more disks in the array, and not all are utilised to rebuild a given stripe. This also allows for the possibility that multiple stripes can be rebuilt in parallel. The major disadvantage is the reduced data capacity of the array compared to a traditional layout, due to the extra parity strips.

### 2.3 RAID Taxonomy

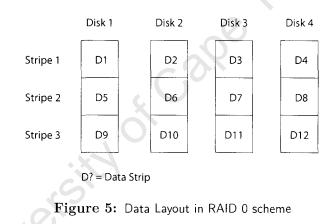

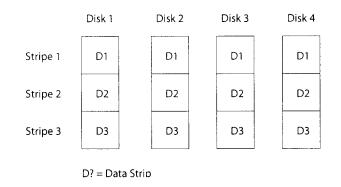

### 2.3.1 Non-Redundant arrays - RAID Level 0

The scheme illustrated in Figure 5 has come to be known as RAID 0, though it is generally acknowledged that is not a true RAID. A single failure will render the data across the entire array useless, since each disk stores part of every file. It is thus necessary to store error correcting information, so that it is possible to recover from at least one disk failure.

### 2.3.2 Mirroring - RAID Level 1

In the case of mirroring<sup>4</sup>, reliability is achieved by simply duplicating all data across two or more disks. This provides complete reliability with minimal repair and recovery time - in the event of a single failure, any of the duplicates can be used for reads, while writes can be mirrored across the remaining disks. This scheme offers the possibility of greater bandwidth through parallelism, since two reads of different sectors can be assigned to two different disks - both reads occur at the same time, effectively doubling the bandwidth. With more than two disks, multiple reads can be scheduled simultaneously.

Mirrored disks also suffer the smallest write penalty, since the cost of any write is simply the maximum cost for any of the individual disk writes. If the disk spindles and heads are synchronized<sup>5</sup>,

<sup>&</sup>lt;sup>4</sup>Initially referred to as disk shadowing by Britton et. al. [BG88]

<sup>&</sup>lt;sup>5</sup>At any given moment, the heads of each disk are over the same logical sector

Figure 6: Data Layout in RAID 1 scheme

there is no write penalty, since all disks move in unison, acting as one large disk. Mirroring has the highest overhead of all (100%), however, since each disk in addition to the primary disk is used solely for redundancy - none of its capacity is available for useful storage.

Another issue is that recovering a failed disk involves copying the entire disk to a replacement - this is not only time consuming, it also reduces the performance of the RAID during reconstruction, which may not be acceptable in certain real-time applications. However, if more than 2 disks are used, one of the clones can simply be taken off line and used to recover the failed disk in a short period of time.

### 2.3.3 Striped Data with Parity - RAID Levels 2 - 4

Figure 7: Data Layout in RAID 4 scheme

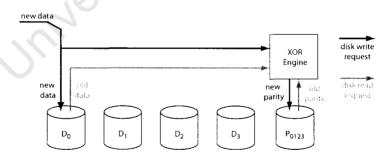

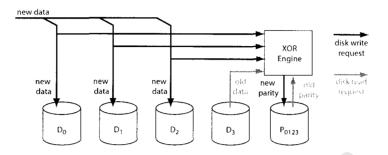

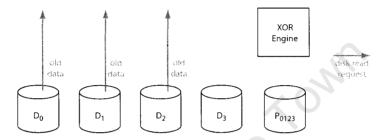

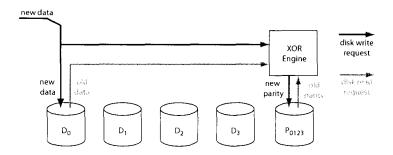

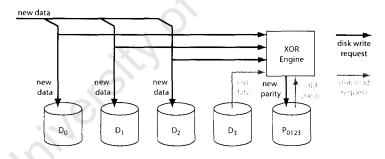

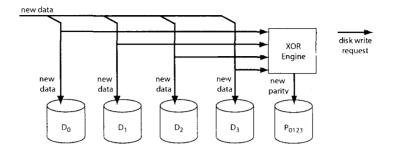

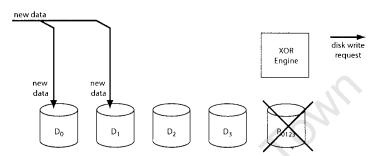

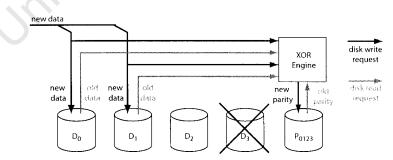

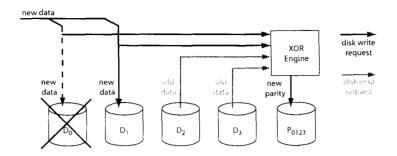

In order to prevent data loss in RAID systems, other than level 1, it is necessary to incorporate some sort of redundancy into the system. The simplest and most widely adopted scheme provides single error correcting parity [PGK88] using XOR operations, and is able to prevent single disk failures. This technique forms the basis of RAID 2-4.

RAID level 2 uses additional disks to store Hamming Code data, which is used to determine which disk in the array failed. However, most modern drive controllers can detect which disk in the array has failed, thus eliminating the need for these extra redundancy disks. This allows more of the total capacity to be utilised for data storage versus redundancy.

Since disk failure can now be detected by the controller, parity can be stored on a single separate

disk, and a single failed disk (parity or data) can be reconstructed from the remaining disks. This is referred to as RAID 3 in the taxonomy. The two possible failure scenarios are illustrated in Figure 8.

| Data        | Parity | 1       | Data       | Parity   | Data     | Parity |

|-------------|--------|---------|------------|----------|----------|--------|

| $0 \ 1 \ 0$ | 1      | 0       | 1 0        | ?        | 01?      | 1      |

| $1 \ 1 \ 1$ | 1      | 1       | 1 1        | ?        | 1 1 ?    | 1      |

| $1 \ 1 \ 0$ | 0      | 1       | 1 0        | ?        | 1 1 ?    | 0      |

|             |        |         |            |          |          |        |

| Normal I    | Fa     | iled Pa | arity Disk | Failed E | ata Disk |        |

Figure 8: Illustration of the 2 possible failure scenarios

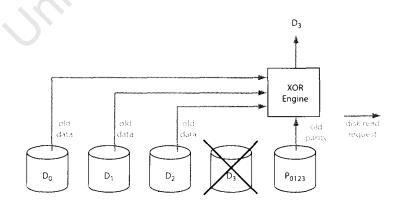

The reconstruction simply involves reading the data from all the undamaged disks for each stripe, calculating the parity of that data, and then writing this value to the replacement disk. If the failed disk was the parity disk, the recovery is done by simply recomputing the parity. If the failed disk was a data disk, the scheme still works since the XOR operator is commutative. Figure 9 illustrates this using the state represented by the Failed Data Disk scenario in Figure 8.

| Old | lData | Parity      | Recovered Data |

|-----|-------|-------------|----------------|

| 0   | 1     | $\square$ 1 | 0              |

| 1   | 1     |             | 1              |

| 1   | 1     | 0           | 0              |

Figure 9: Reconstruction of lost data

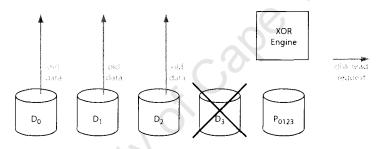

RAID 4 still distributes data across disks, with a parity disk for redundancy, but now data is partitioned across the disks in strips. The new parity must be computed and written to disk to complete a write request. Hence, each write must access the parity disk before it completes. Since multiple write requests will be queueing for this single parity disk, a bottle neck is created in RAID levels 3 and 4.

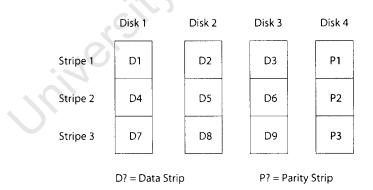

### 2.3.4 Rotating Parity with Striped Data - RAID Level 5

Figure 10: Data Layout in RAID 5 scheme

thus reducing the bottleneck created by a single parity disk. This scheme allows multiple simultaneous writes if the writes are to different stripes, and there are no common clusters between the writes.

RAID 5 is the most common scheme used commercially, as it offers the best balance between data integrity, storage performance and overhead (the amount of total free space that must be devoted to storing redundant parity information).

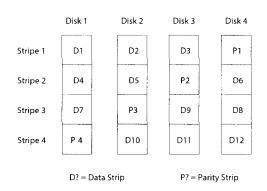

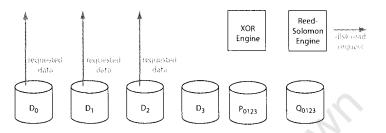

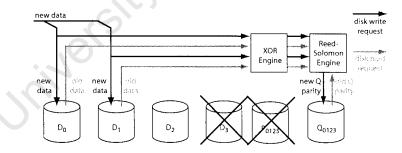

### 2.3.5 Dual Disk Failure Protection - RAID Level 6

All the RAID levels described thus far offer protection from only a single disk failure. These schemes work well in deployments where data integrity must be balanced against storage performance, but are in insufficient in situations where data integrity is of primary importance. RAID 6 addresses this by providing protection from up to two disk failures.

Figure 11: Data Layout in RAID 6 scheme

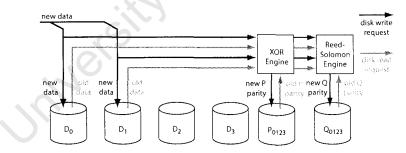

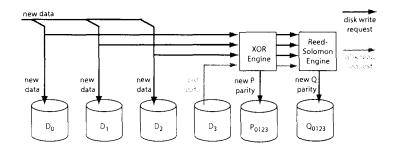

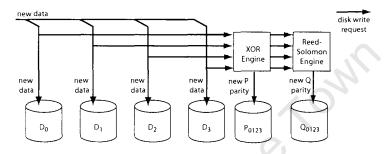

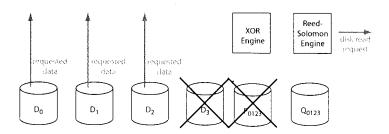

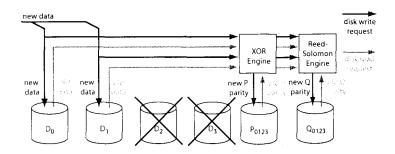

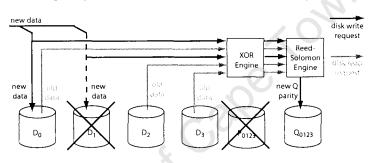

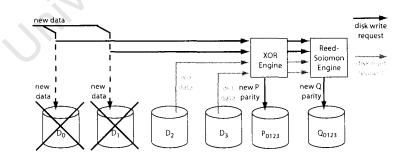

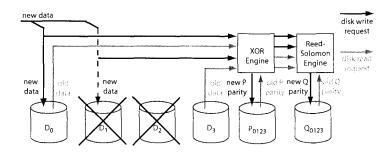

RAID 6 achieves this using two different, independent parity strips per stripe. The first parity strip is the same XOR parity used in RAID level 5. The second is a Reed-Solomon code across the data strips within the stripe. Like RAID 5, the parity strips are rotated to reduce bottleneck effects caused by concurrent accesses to these strips.

### **RAID 6 Reed Solomon Coding**

The Reed Solomon Code used to provide the parity protection for the second disk in RAID 6 is the result of work by Reed and Solomon [RS60]. Their coding technique is based on the algebra of Galois fields [Anv07], specifically the  $\mathbf{GF}(2^8)$  Galois field. This is a finite field with  $2^8$  elements<sup>6</sup> with several important properties:

- 1. Addition (+) is represented by the bitwise XOR operator.

- 2. Multiplication is represented by boolean polynomial multiplication modulo the irreducible polynomial  $x^8 + x^4 + x^3 + x^2 + 1$ , which is equivalent to the operation of a linear feedback shift register.

<sup>&</sup>lt;sup>6</sup>The size of the field is chosen so as to no limit the maximum number of usable drives (255), while still ensuring reasonable bounds on the computations required.

- 3. The normal algebraic commutative, associative and distributive laws of addition and multiplication apply.

- 4. Raising an element to a power is congruent mod 255.

- 5. Field generators,  $g^n$ , exist that generate elements of the field without repetition until all elements have been exhausted with the exception of the identity element.

Consider each strip in a given stripe as a vector of bytes, with  $\mathbf{D}_0, \mathbf{D}_1, \mathbf{D}_2, \ldots, \mathbf{D}_{n-1}$  representing the data strips, **P** representing the RAID 5, XOR parity and **Q** representing the RAID 6, Reed-Solomon parity. We can then compute **P** and **Q** for *n* data disks as follows:

$$\mathbf{P} = \sum_{i=0}^{n} \mathbf{D}_{i} \tag{1}$$

$$\mathbf{Q} = \sum_{i=0}^{n} g^{i} \cdot \mathbf{D}_{i}$$

(2)

where g is any generator of the field.

In the event that 1 data disk and the  $\mathbf{P}$  drive are lost, the lost data can be recomputed through the equation:

$$\mathbf{D}_x = (\mathbf{Q} + \mathbf{Q}_x)/g^x \tag{3}$$

In the event of 2 data disk failures, the following set of equations can be used to recover the missing data  $\mathbf{D}_x$  and  $\mathbf{D}_y$

$$\mathbf{D}_y = \mathbf{P} + \mathbf{P}_{xy} + \mathbf{D}_x \tag{4}$$

$$\mathbf{D}_{x} = \frac{g^{-x} \cdot (\mathbf{Q} + \mathbf{Q}_{xy}) + g^{y-x} \cdot (\mathbf{P} + \mathbf{P}_{xy})}{g^{y-x} + \mathbf{I}}$$

(5)

where I is the multiplicative identity element.

In all other cases, lost data can be recovered as in the equivalent RAID 5 case.

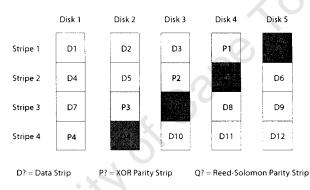

### 2.3.6 Sector Protection through Intra-Drive REdundancy (SPIDRE)

SPIDRE is a RAID protection scheme developed at the IBM Zürich Research Lab. SPIDRE addresses the real-world problem of strip-failures in disks. A strip-failure occurs when a small contiguous surface area of a disk platter becomes unreadable. This area is usually smaller than a RAID strip<sup>7</sup>, and since the rest of the disk is still operational, it is only a single RAID stripe that is compromised. This type of burst failure is differentiated from the atomic failure of an entire disk, in that some portion of the data on the disk is recoverable.

In a RAID 5 array operating in degraded mode, such a failure would result in immediate data loss in the array. The only way to prevent this would be to utilise a RAID scheme designed to protect against more than a single disk failure, such as RAID 6. However, this introduces additional overhead, both in terms of number of disks and in storage performance. SPIDRE provides an compromise solution by recovering strip-failure related burst errors with minimal overhead.

<sup>&</sup>lt;sup>7</sup>See Section 2.1 (p. 5)

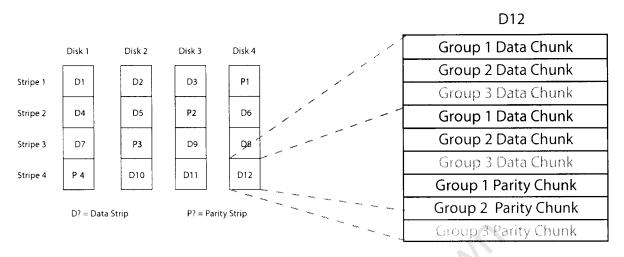

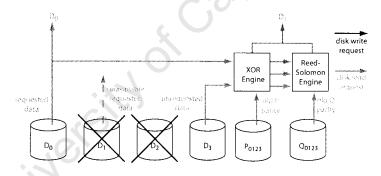

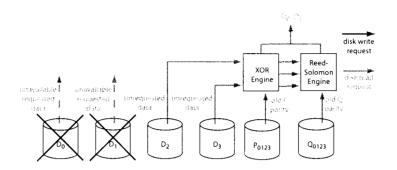

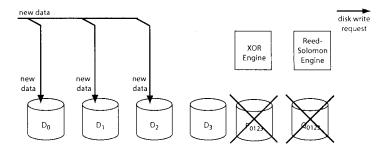

Figure 12: Illustration of the SPIDRE parity scheme applied to a RAID 5 array.

SPIDRE proposes an alternate solution to this problem. Instead of using an extra parity disk, SPIDRE adds XOR parity information to each strip in a stripe. This parity is arranged as in Figure 12 and can be used to recover lost data chunks in a strip.

The important part of this scheme is that there are several XOR protection groups (labeled as such in the diagram), that are interleaved. Without interleaving, only a single missing chunk could be recovered, as is the case with RAID 5. Interleaving allows for recovery from strip-failures that span several chunks.

In the illustrated SPIDRE configuration, the loss of any 3 consecutive chunks in a given strip (due to strip-failure) can be recovered using the same recovery algorithm used in RAID 5. The number of groups per strip, as well as the number and size of chunks are determined by examining strip-failure data from real-world disks.

The storage efficiency of SPIDRE is directly related to the number of sequential bytes that can be recovered and the size of a strip. For instance, given a strip size of 64KB and a maximal strip-failure length of  $256B^8$ , we would require a 256 interleaved protection groups, each with  $\frac{64 \times 1024}{256} = 256$  chunks. This would provide protection against any strip failure of less than 256 bytes within that strip, while requiring an overhead of only 256 bytes. Thus the focus on burst-failures within a strip allows the SPIDRE overhead to be minimised to exactly the number of recoverable consecutive bytes in a strip required.

### 2.4 Issues with RAID

Within RAID systems, there are a number of problematic areas: the physical layout of data across the array; improving reliability; recovery and repair after disk failure; design and correctness of RAID controllers and architectures; and performance of RAID architectures in specifically problematic areas. A summary of these issues, and related work in these areas, follows.

<sup>&</sup>lt;sup>8</sup>This would be established from real-world data.

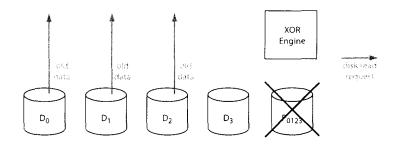

### 2.4.1 The Small Write Problem

A significant problem with RAID systems arises in their application to On-Line Transaction Processing (OLTP) systems. These systems have disk access patterns that typically consist of read-modify-write cycles. With the exception of RAID 1, this causes several problems for a RAID system. Firstly, a write in a striped array requires reads of both data and parity blocks, computation of a new parity, and writes of both new data and new parity - 4 times more accesses than for a single disk. Another problem is that these accesses are small, and hence only a few blocks within a specific stripe are altered, yet the parity disk for the entire stripe is unavailable during the update - this effectively reduces the performance of the array, by reducing the parallelism possible.

This problem was initially tackled by [SCO90], who proposed a scheme wherein writes were buffered until a sufficiently deep queue had developed to minimise the write penalty. The problem with this approach is that a disk failure could lead to data loss unless the buffers used are fault tolerant.

The work of Menon et. al. [MM92] attempts to solve this problem using a technique referred to as *Floating Data and Parity*. Each cylinder in a disk is set to contain either data or parity, and for each such cylinder, an empty track is set aside. During the update cycle, rather than overwrite the old data, the new data is instead written to the rotationally closest free block. This allows the read-compute parity-write to be executed without an extra rotational delay. The main problem with this approach is that undermines large block reads, since logically sequential data need not necessarily be stored sequentially on the disk.

The overhead required by this scheme is very low, but fault tolerant array controller storage is required to track data and parity locations. Variations on this technique are the log structure filesystem (LFS) [RO91] and the distorted mirror approach [SO91], which uses the 100% overhead of mirroring to maintain a copy of each block in both fixed and floating storage. All the above schemes require significant amounts of controller memory to handle buffering and store location information.

The most promising solution thus far arises from the work of Holland and Stodolsky et. al. [SGH93, SHG93]. They present a system wherein parity updates are buffered, then written to a log when sufficient are accumulated to allow for efficient disk transfer - data updates are written immediately. This log is then periodically purged, with all parity updates in it being written to disk. This scheme ensures data reliability, since: if a data disk fails it can be recovered from the parity and remaining data disks; if the parity or log disk fails, then the parity disk can be reconstructed from the remaining data disks, and the log disk can be emptied.

One problem with this approach is that unless the array controller has fault tolerant buffers, a failure could result in data loss. Another is that the log disk could easily become a bottleneck in the system - this can be solved by distributing the log disk across all disks, much as is done with the parity disk in RAID 5. The most problematic aspect of this approach, and one that does not appear to have been addressed, is how user response will degrade during reconstruction of a failed disk. Various schemes to address this for other RAID configurations are presented in Section 2.4.2.

A fairly recent solution presented by Haruo [YG99], *Fault-tolerant Buffering Disks*, uses disks to provide double buffering, which increases write speed, as well as backup for fault tolerance and

read speed improvements. The system does not scale well, and has a higher overhead than other systems, but for small arrays increases both throughput and response time.

### 2.4.2 Reliability

Due to their decreased MTTF, preventing data loss in RAID systems is a very important consideration. Redundancy is the primary fail safe, and many schemes exist to achieve this. Immediately after a failure, it is necessary to perform some form of recovery. Finally, the failed disk needs to be replaced and reconstructed to restore the system to full working efficiency. This section covers advances in these areas.

### **Redundancy Schemes**

In order to prevent data loss in RAID systems, other than level 1, it is necessary to incorporate some sort of redundancy into the system. The simplest, and most widely adopted, system uses single error correcting parity [PGK88], using XOR operations, and is able to prevent single disk failures.

EVENODD [BBBM94] is an alternate scheme that prevents two disk failures, and is efficiently implementable in hardware. The layout described to prevent bottlenecks restricts the array to a maximum of 259 disks, however.

Other schemes include balanced incomplete block designs (BIBD) [HG92], which attempt to uniformly distribute data and parity across a disk, and coding methods proposed by Gibson [HGK<sup>+</sup>94] which protect against arbitrary numbers of failures, but have overheads that increase exponentially w.r.t. prevented failures. Additionally, the schemes are fairly restrictive on array dimensions for optimal redundancy usage.

Finally, a scheme proposed by Alvarez [ABC97], DATUM, allows for recovery from an arbitrary number of disk failures, using an optimal amount of redundant storage, whilst still allowing flexible array configurations, and ensuring both parity and data are evenly distributed across the disks.

### Recovery

Recovery is necessary immediately after a disk failure, to ensure that operations in progress at that time are not lost completely. There are currently three approaches to this problem. The first and most prevalent solution, forward error correction, attempts to handle errors dependent on the current state of the system and the state of execution of the requested disk operation. This method requires enumeration of all possible states of the system, and handcrafting execution paths for each. This is both time-consuming and error prone.

An alternate approach, backward error recovery [CG94], uses an approach popular in transactional systems which are required to support atomicity of operations. The approach is to set out a small number of execution paths for each of the possible states of the system (error-free, disk failed, etc.). Each execution path is composed from a set of simple, reversible operations, which are logged as they execute. When a failure occurs during execution of one of these paths, the execution is rolled-back by executing the inverse operations in reverse order. When the original state is

recovered, an alternate execution path, appropriate to the current state of the system, is used to retry the failed operation.

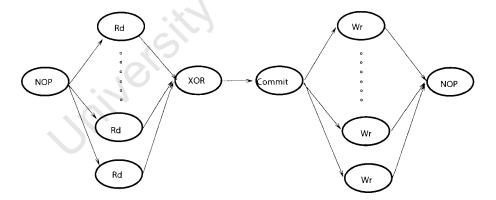

The final alternative, roll-away error recovery [Cou97], uses a similar scheme to backward error recovery, but adds commit barriers to simulate two-phase commit in transactional systems. The idea is that when a failure occurs, execution is allowed to continue up to a commit barrier, but not beyond. If the completed state is not reached by this, then an alternate execution path is chosen, and the operation is reattempted. This style of error recovery is popularised by the RAIDframe system [CGHZ96a], which is discussed in Section 4.2.1 (p. 42).

### Reconstruction

A major consideration when recovering from a failed disk is the effect on user response times, i.e. does the reconstruction of the failed disk degrade the performance of the RAID? In the usual case this is very true, since reconstructing any single disk requires access to all the other disks to reconstruct every stripc, effectively rendering the RAID inaccessible during each such access. While stripe reconstruction can be interleaved with user requests to allow the RAID to continue operation, access latency will rise unacceptably and the Mean Time to Repair (MTTR) will increase. The longer it takes to repair the RAID, the more likely it is a second disk will fail before the first is recovered, resulting in data loss.

An innovative solution to this is presented in [HG92, HGS93, HGS94, Hol94]. The authors suggest that performance degradation during reconstruction can be reduced by sacrificing some of the data capacity of the RAID toward redundancy. The crux of their work is the idea of a virtual topology that is mapped to the physical disk topology of the system. Assuming that there are 7 disks available, the normal, intuitive solution would be to treat all 7 as a large array with striping across all 7, and distributed parity. An alternative would be to treat this as an array of 4 disks, in a RAID 5 configuration. The authors discuss ways of mapping such a virtual topology to the physical one<sup>9</sup> to allow this behaviour.

The benefit of this approach is that if a single disk fails, only particular stripes in the virtual array will be affected. Importantly, since each stripe only consists of 4 virtual disks, reconstructing affected stripes only requires read accesses to 3 other real disks. This greatly diminishes the bandwidth required for reconstruction, and allows accesses to the other 3 disks<sup>10</sup> to occur simultaneously. Additionally, the mapping scheme mentioned above ensures that the virtual sectors are uniformly distributed, thus ensuring that no single disk gets overburdened during reconstruction. The only requirement is increased redundancy overhead, since instead of a ratio of 6:1 of data to parity sectors, the ratio is now 3:1.

The latest development in this field has been *data-reconstruction networks* [Yok00]. The idea is that disks are connected in subnetworks which are then interconnected to form one large network. Reconstruction of a single failed disk is localised to a subnetwork, hence reducing the impact on the whole network. Additionally, the overlapping of subnetworks allows the recovery of more than 1 failed disk, dependent on the architecture.

Other considerations during reconstruction are how to handle user requests. If a read is requested of an as yet unreconstructed sector, the sector can recovered on the fly using parity and the

<sup>&</sup>lt;sup>9</sup>See Section 2.2.4 (p. 8)

<sup>&</sup>lt;sup>10</sup>Remember that 1 disk has failed, and is in the process of being reconstructed

remaining data disks. However, once this data is calculated, the option arises to store it (which requires buffering), write it to disk (which could upset the scheduling algorithm in use) or discard it (which entails having to recalculate it later during the reconstruction). The choice of which approach to take is dependent on the implementation.

If a write is requested during reconstruction, then this new value is simply written to the replacement disk, and the appropriate stripe is excluded from the rebuild list, which reduces reconstruction time. Alternatively, all stripes are reconstructed in order, and new data is simply overwritten - this has the advantage of significantly less bookkeeping, but there is a lot of unnecessary work performed.

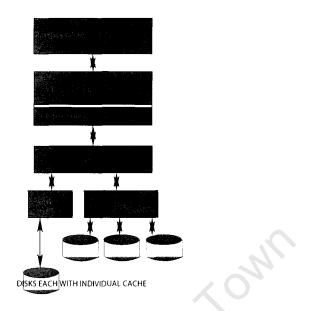

### 2.5 RAID Caching

Due to the relatively slow access and transfer times of secondary storage systems in general, caching plays an important role in improving the performance of these systems. The most important function of a cache is to store recently accessed data in memory. Subsequent requests for this data can then be served from memory much faster than accessing it on disk.

As the cache is finite in size, its contents must be managed so as to ensure sufficient space for new additions whilst still retaining data which is most likely to be accessed in future. The various techniques for achieving this are discussed in Section 2.5.1 (p. 18).

The cache can also perform a predictive function, by examining the list of recently accessed data and requesting adjacent data from disk to store in memory. This predictive behaviour leverages the spatial locality of most workloads, where data is generally accessed in physically adjacent groups.

As in all connected systems with a speed disparity, the cache can also act as a buffer to mask the speed differential. This can be accomplished by allocating a section of the cache to buffer data that is being sent faster than it can be processed by the RAID system. This section can also be used to hold intermediate results until a sufficiently large amount has been accumulated to efficiently send to the host in one transmission.

### 2.5.1 Caching Schemes

A cache is finite in size and divided into a number of equal-sized, contiguous sections, referred to as *pages*. These pages are atomic and form the basis of all cache operations.

When a cache is initialised, it is empty and all pages are available to hold data. As data is added to the cache, the number of free pages decreases until the cache is full and no pages are available. From this point on, whenever new data is added to the cache, it is first necessary to free one or more pages that contain data before the new data can be successfully added.

The process of freeing pages is referred to as destaging. If a page to be destaged has been marked as  $dirty^{11}$ , its value is first written to disk. The page's entry in the cache page table (which holds a list of all pages in the cache) is then modified to reflect that it is free and available to store

<sup>&</sup>lt;sup>11</sup>See Section 2.5.2 (p. 21)

data. Note that the data in the page is not actually deleted, as the value stored therein will be overwritten when the page is next used.

The method used to determine which cache page to free when the cache is full is referred to as the *cache policy*. There are a variety of cache policies that are tailored to specific uses, but all derive to some extent from either the LRU or LFU policies, which are discussed below. We also present the ARC policy, which attempts to synthesise the best aspects of LRU and LFU to provide a very good, general purpose policy. For a detailed overview of some of the operational details of these schemes, refer to Section 8.4 (p. 111).

### **Optimal Page Replacement Policy**

The optimum efficiency criteria for a cache is the rate at which pages are recycled. In other words, the more infrequent the need to destage a cache page, the better the policy is performing. This arises from the desire to minimise the number of slow disk accesses necessary, which are incurred whenever a page of data must be brought into the cache from disk.

Early research into page replacement algorithms that maximised this criteria, particularly the First-In-First-Out (FIFO) algorithm<sup>12</sup> led to the discovery of **Belady's anomaly**: For certain page replacement algorithms, increasing the cache size could increase the page recycle rate.

This led to the definition of an optimum cache replacement policy (OPT) [SGG02], which is characterised by the following algorithm:

Replace the page that will not be used for the longest period of time.

Clearly, this algorithm is not practically implementable since it requires knowledge of future workload behaviour. It does, however, provide a baseline against which other policies can be compared.

### $\mathbf{LRU}$

The Least Recently Used (LRU) policy is an attempt to approximate the OPT policy by using the events of the *recent past* to predict events in the *near future*. Under LRU, each page has associated with it the time it was last *accessed*. An access here is defined as a read or write request that alters the contents of that page without requiring it to be destaged.

When a page must be chosen for replacement, the LRU policy picks the cache page with the *earliest* access time, i.e. the page that has not been used for the longest period of time. This scheme then works under the presumption that a page that has not been used for a long time will not be required in the near future.

One of the problems with the LRU scheme is that the possibility of thrashing exists. Thrashing occurs when a page that has just been destaged is then requested and has to be read back into the cache. It occurs with workloads that repeatedly access a working set of data that is just

$<sup>^{12}</sup>$ Where the first page added to the cache is the first page freed.

larger than the cache size. In this case, LRU is very inefficient as the page recycling rate increases greatly.

LRU is also susceptible to cache pollution by sequential workloads. In this scenario, the sequential workload causes all pages in the cache to be destaged and replaced by the sequential data. As long as the sequential stream lasts, existing pages (that should potentially remain in the cache) are destaged on each request. In addition, once the sequential stream transitions to some other access pattern, the cache is left devoid of any useful recency information with which to determine policy behaviour.

### LFU

The Least Frequently Used (LFU) policy takes a different approach to LRU in that it considers recent behaviour rather than recent history. This utilises the assumption that if a page has been used frequently in the past, it is likely to be used again even if it has not been used recently.

Under LFU, each page has associated with it a counter of the number of times it has been accessed since being read in from disk. When a page must be chosen for replacement, the LFU policy chooses the page with the smallest frequency count.

A major weakness in LFU is also related to the occurrence of thrashing, though under different circumstances. A workload that comprises a large number of frequently accessed pages, together with an equal number of random requests will experience cache starvation as the cache becomes filled with the frequently accessed pages.

In this situation, none of the frequently accessed pages are eligible for destaging, and so the recently used, random accesses must be continuously swapped into and out of a single cache page. Once again this is not ideal, as the page recycling rate increases here too.

### ARC

The Adaptive Replacement Cache (ARC) policy was developed by IBM [MM03b]. It attempts to strike a balance between the characteristics of LRU and LFU by dynamically adapting to the workload presented.

An ARC cache uses a page table that is twice the size of the actual number of pages in the cache. This page table is split into two equal sized lists: L1 which contains those pages that have been accessed exactly once; and L2 which contains pages that have been accessed more than once.

L1 and L2 are further divided into T1, B1 and T2, B2 respectively. T1 and T2 contain information related to the actual pages in the cache, and as such the total size of T1 + T2 is always equal to the cache size. B1 and B2 are used to record historical data, and do not reference actual cache pages. ARC also uses a target size target\_T1, which represents the optimum size of L1 and is updated constantly during execution.

The replacement policy for ARC uses the LRU criteria:

Replace the LRU page in T1, if T1 contains at least target\_T1 pages; otherwise, replace the LRU page in T2. The adaptive nature of cache is achieved by varying target\_T1 in response to the observer workload. The adaptation rule, which is applied whenever a new page is added (ie. an actual cache miss), is:

> Increase target\_T1, if the new page exists in the history B1; similarly, decrease target\_T1, if the new page exists in the history B2.

By applying these two rules to the cache, ARC is able to adapt to changing workloads and hence avoids the pitfalls inherent in both LRU and LFU. It is scan-tolerant, in that sequential workloads do not pollute the cache, and it is less susceptible to thrashing as the target\_T1 metric attempts to ensure there is enough space for both frequently and recently used pages. For a more in-depth explanation of ARC, refer to [MM03b, MM03a].

### 2.5.2 Write Caching

Across all caching schemes a distinction can be drawn between Write-Back and Write-Through caching. Both these terms refer to the situation where a write operation is requested and the data to be written is sent by the host to the RAID Controller.

In a Write-Back cache, this data is added to the cache and the relevant pages flagged as dirty. A signal is immediately sent to the host indicating the success of the requested write. At some later time, usually when pages are flushed from the cache, the updated data is actually written to disk. This scheme has the advantage that multiple updates to the same data will result in a single disk access that reflects only the last, correct value.

By reducing the overall number of disk accesses required, this increases performance in the system, but at the cost of reliability. Unless the cache is implemented in non-volatile RAM<sup>13</sup> (NVRAM), any data not written to disk will be lost in the case of a power failure. This scheme also proves problematic when used in multi-level RAID schemes<sup>14</sup> as cache coherency cannot be guaranteed.

In a Write-Through cache, the data is added to the cache and immediately written to disk. Only once the disk request has succeeded is the host signalled to indicate a success. Since this scheme requires more disk accesses that Write-Through caching, it performs poorly by comparison. It does have the advantage of offering much better reliability across power failures, as writes are always persisted immediately to disk.

21

$<sup>^{13}</sup>$  RAM that can persist its contents across power failures, such as NAND flash RAM.  $^{14}$  See Section 5.4.4 (p. 68).

# Chapter 3

# Simulation of Systems

In this chapter, we present an overview of the discipline of simulation. We introduce the discipline, and evaluate both it benefits and shortcomings. We further present the fundamental aspects of simulation and outline the principles of conducting a simulation study. Finally, we discuss the use of simulation environments, present a number of available simulation environments, and justify the choice of one for the development of our simulator.

### 3.1 Introduction

In areas such as operations research and management science, simulation is a tool that allows business processes to be analysed and optimised without disrupting the daily activities of the business. In engineering disciplines, simulation allows products to be developed and tested before investing in the manufacturing process. In scientific disciplines, theoretical models can be simulated to determine their validity and future behaviour.

A simulation attempts to imitate the behaviour or operation of some process for the purpose of studying some aspect of it. The process being simulated is referred to as a system, and in order to correctly mimic its operation it is necessary to develop a model of this system. This model usually takes the form of mathematical relationships, which calculate observable outputs based on input parameters, and logical relationships, which determine which portions of the model are exercised at a particular point in time [LK82].

In order to develop this model of the system, it is necessary to make a set of assumptions regarding the operation of the system. These assumptions may be based on a theoretical idea of how the system should work, or may be derived from an empirical investigation of the system. These assumptions seek to approximate the system, which is usually too complex to model in its entirety. by concentrating on areas of particular interest or importance. The results produced by a simulation are thus only estimates of the true behaviour of the system.

For certain models that are sufficiently simple, it is possible to determine an analytical solution for the system model. This solution is obtained by using mathematical methods<sup>1</sup> to obtain exact results from the system model. This is obviously a significant improvement over the estimated

<sup>&</sup>lt;sup>1</sup>Such as algebra, calculus or probability theory

results produced by simulation, but such analytic solutions are usually not possible for realistic system models, due to associated complexity.

For most other models, simulation is necessary to obtain information from a system model. Simulation, in our context, involves using a computer to numerically evaluate a given model over a stipulated time period. This evaluation involves a number of steps, and at each step data is gathered that is later used to estimate the desired characteristics of the model[LK82]. These estimates can then be used to refine the model, change the simulation parameters or implement changes in the corresponding real-world system.

### 3.2 Evaluating the Benefits of Simulation

Simulation and analytic solutions are the most common approaches to analysing a given system model. Each has their own advantages and drawbacks, as outlined by Law and Kelton [LK82]. Given our focus on simulation of systems, we present first the advantages that simulation of system models provide:

- 1. Most mathematical models of real-world systems are too complex to evaluate analytically, thus simulation is often the only viable option.

- 2. Simulating an existing system allows hypothetical operating conditions to be applied and the performance of the system to be estimated.

- 3. Simulation is best suited to evaluating alternative designs of a single system (or alternative operating parameters for a single system) against a given set of requirements to determine the most suitable.

- 4. It is possible to maintain much tighter controls over experimental conditions while conducting a simulation of a system when compared to experimentation with the system itself.

- 5. Simulation allows us to manipulate time within an experiment. Thus we can compress time for long simulations, allowing for results to be obtained sooner. Conversely, it is possible to dilate time for processes that occur over a very short time, allowing a detailed study of their operation in expanded time.

Simulation is not a magic cure, however, and there are a number of drawbacks that must be carefully considered. In many situations, an approximated analytic solution of a simplified model may be of more use, simpler to construct and less expensive than the equivalent complex simulation. The considerations against simulation are:

- 1. Simulation models can be time-consuming to develop, and complex simulations require large amounts of computation time and power, which can prove expensive.

- 2. A simulation that uses stochastic models<sup>2</sup> produces only estimates of the true behaviour of a system, whereas an analytic solution can produce exact results. It thus stands to reason that if an analytic solution is possible, it would be preferable to simulation. However, analytic solutions are not always possible.

<sup>&</sup>lt;sup>2</sup>See Section 3.3.1 (p. 24)

3. Stochastic models that produce estimates of a model's characteristics require several simulation runs to be executed for each set of input parameters, to allow statistical analysis of the results. This requirement means that simulations are better suited to comparing a finite set of alternatives, rather than optimising over a range of parameter values.

### 3.3 Simulation Fundamentals

### 3.3.1 Systems and Models

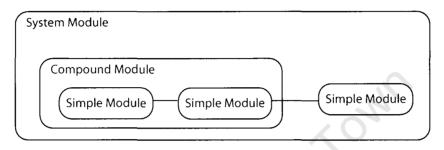

A system is defined by Schmidt and Taylor [ST70] to be a collection of entities (components), e.g. people or machines, which act and interact toward the accomplishment of some goal. A simulation of a system requires a model of the system to be developed. This model describes the functions of the various components of the system, as well as the interaction between these components. The granularity of this model is highly dependent on the particular objectives of the study, as well as the accuracy of results required. For instance, a simulation of a commodity computer hard disk drive would model the various components of the drive, such as the drive arm, the platters and the read/write head. However, in a simulation of a storage system, the disk drive would form one small component within the overall model.

A model of a system usually involves a number of variables whose values changes over time. These variables are referred to as state variables, and the state of the system is then defined to be the values of all state variables at a given time. In the simulation of a storage system, examples of such variables would be: the number of I/O requests being processed; the time of arrival of each request: and the collection of data stored in the cache.

### **Continuous and Discrete Systems**

Depending on the areas of interest and the model employed, a system may be classified as either continuous or discrete in nature. For a continuous system, the state variables change continuously with respect to time. In a discrete system, the state variables change only at a finite number of points in time.

For example, a model of storage systems that is interested in investigating the Quality of Service of the system will be continuous, as variables such as the throughput, bandwidth utilisation and failed requests change continuously. Conversely, a model that focuses on the actual requests in the system and how they are processed is discrete in nature, since each individual request is simulated atomically. Hence, the state variables only change when commands are executed to satisfy each request.

### **Deterministic and Stochastic Simulations**

A further distinction can be made between deterministic and stochastic models. A deterministic model given a set of initial conditions will always produce the same resultant state at a given instant in time. A deterministic model contains no random variables, hence the results it produces are always the same.

For the same set of initial conditions, a stochastic model will produce different states for the same time instant dependent on the random number seeds chosen<sup>3</sup>. Since a stochastic model contains one or more random variables, the output data it produces are also random and serve only as an estimate of the true behaviour of the system. Consequently, the results of a stochastic simulation require more interpretation than those for a deterministic one.

The simulation models we present in this work are discrete and stochastic. They model the processing of individual I/O requests, over a period of time, using random variables.

### 3.3.2 Advancing Simulation Time

The state of a dynamic discrete simulation model changes over time, and hence the state variables must be periodically updated at specific times. The concept of simulation time must thus be introduced to determine when to update individual variables. This simulation time is stored in an independent variable, and must be updated over the course of the simulation. The units in which simulation time is measured is determined by the simulation environment. There is also usually no relationship between the length of the simulation time required to complete a simulation to (the period of time under investigation) and the actual time required to run the simulation to completion on a computer system (the execution time).

There are two main approaches to advancing simulation time: *fixed-increment time advance* and *event-driven time advance*. Each method is responsible for incrementing the value of the simulation time by a specific amount, which in turn determines when and how simulation variables are updated.

### **Fixed-Increment Time Advance**

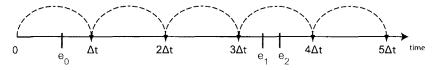

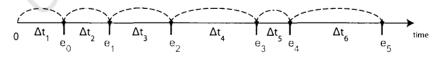

In this approach, a fixed time interval  $\Delta t$  is chosen at the start of the simulation. This interval represents the value by which the simulation time will be advanced after each update. After each time increment, the simulation must check whether any events were scheduled to occur during the elapsed interval of length  $\Delta t$ . All such events are then assumed to have occurred at the end of the interval, and the routines associated with these events are executed as though this were the case. This scheme is illustrated in Figure 13.

Figure 13: In the Fixed-Increment time advance approach, events are only processed at fixed increments. Events occurring between increments must be moved to an appropriate boundary. In the figure above, both events  $e_1$  and  $e_2$  will be processed as though they had originated at time  $4\Delta t$ . (Figure adapted from [LK82])

The requirement that events be processed as though they had occurred at the end of an interval has a number of disadvantages. Multiple events that occur in a given interval are treated as

<sup>&</sup>lt;sup>3</sup>See Section 3.3.6 (p. 31)

having occurred at the same simulation time, which ignores the actual ordering of events within the interval. This requires that the simulator must have some method of determining in which order to execute these apparently simultaneous events. Calculations that are dependent on the time an event occurred will hence be incorrect.

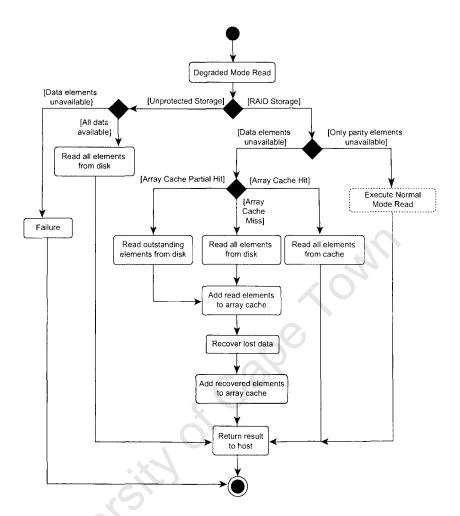

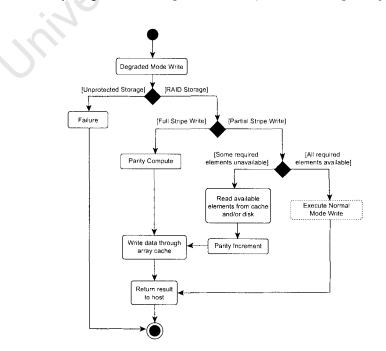

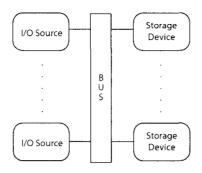

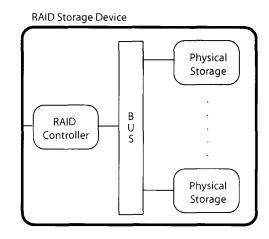

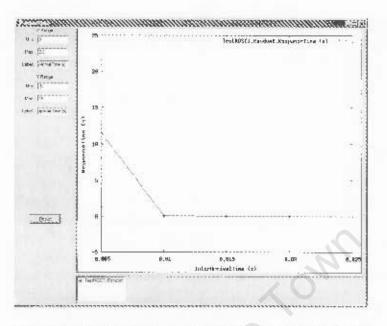

The interdependence between events may also be disrupted by these simultaneous occurrences. For example, a computation associated with event A may rely on the elapsed time since the last occurrence of event B. If both A and B occur in the same interval, but at different times, the computation for A may be incorrect.