The copyright of this thesis vests in the author. No quotation from it or information derived from it is to be published without full acknowledgement of the source. The thesis is to be used for private study or non-commercial research purposes only.

Published by the University of Cape Town (UCT) in terms of the non-exclusive license granted to UCT by the author.

# AAL2 Switching Node to Support Voice Services in 3rd and 4th Generation Networks

6

Prepared by: Sven E. Shepstone

Supervised by: Neco Ventura

Department of Electrical Engineering University of Cape Town 2002

This dissertation is submitted to the University of Cape Town in fulfilment of the academic requirements for the Degree of Master of Science in Engineering

30 August 2002

#### Declaration

I declare that this thesis is my own work. Where collaboration with other people has taken place, or material generated by other researchers is included, the parties and/or material are indicated in the acknowledgements or references as appropriate.

This work is being submitted for the Master of Science Degree in Electrical Engineering at the University of Cape Town. It has not been submitted to any other university for any other degree or examination.

### Signed by candidate

30/08/2002

Sven E. Shepstone

Date

### Acknowledgements

I wish to thank for following individuals and organisations for their invaluable assistance:

- Neco Ventura, for agreeing to supervise this research.

- Telkom, Siemens and the Department of Trade and Industry for their generous sponsorship towards this work.

- Jon Turner, John Lockwood, Tom Chaney, John de Hart, Berkley Shands, Fred Kuhns and Ken Wong from Washington University in St. Louis, for their on-going support.

- Stuart Doyle, for providing a great deal of assistance, especially in the arena of highperformance networks and suggestions on improving the AAL2 switch design.

- Andre van Zyl, for his assistance an numerous aspects of the AAL2 technology.

- Jeanine Mc Gill, for kindly proofreading a portion of this thesis.

- My LyX document processor, for being so loyal every step of the way, and not losing a single character.

- My colleagues at the Communications Research Group at UCT, for their technical support and feedback.

### Synopsis

The research community and industry alike have, over the past decade, been showing considerable interest in packet-switching networks to support voice services as well as data services. A technology that was standardised to accommodate these delay-sensitive requirements is Asynchronous Transfer Mode (ATM), which deals particularly well at transporting uncompressed voice and data. However, due to the exponential increase in wireless applications and their supporting access technologies, a need has arisen for an infrastructure in the wide area network to support and maintain the QoS requirements of low-bit rate, compressed voice. An adaptation layer known as AAL2 was re-standardised to support these specialised voice services. However, a severe side-effect of using AAL2 with traditional ATM switches results in inefficient routing and waste-age of resources.

In this study, a design for an AAL2 switching node will be proposed to address the abovementioned issues. The design is comprised of modules that perform the following functions: Buffering, payload interrogation, protocol translations, packet classification, packet rerouting, timing, scheduling and support for signalling and management interfacing. The supporting architecture is targeted towards an embedded x86-based computing system, which itself is overlaid upon one or several ports of a high-speed, research-oriented ATM switch, known as the Washington University Gigabit Switch (WUGS).

In order to evaluate the operation and performance of the AAL2 switch architecture, a testbed is proposed and implemented, comprising the AAL2 switch at the core, with a supporting infrastructure to emulate the generation and analysis of low bit-rate voice traffic over an AAL2 connection. By conducting a set of experiments, a series of operational and performance results will be presented. Particular focus will be placed on the performance and efficiency of the AAL2 layer over ATM, as well as the ability of the switch to route packets from multiple sources to a set of output connections in the correct manner.

## Contents

| D  | eclar | ation i                                  |

|----|-------|------------------------------------------|

| A  | cknow | vledgements ii                           |

| Sy | nops  | is iii                                   |

| Li | st of | Figures ix                               |

| Li | st of | Tables xii                               |

| G  | lossa | ry xiii                                  |

| 1  | Intr  | oduction 1                               |

|    | 1.1   | Introduction                             |

|    | 1.2   | Thesis Objectives                        |

|    | 1.3   | Scope and Limitations                    |

|    | 1.4   | Thesis Outline                           |

| 2  | Lite  | rature Review and Background Theory 14   |

|    | 2.1   | Introduction                             |

|    | 2.2   | Voice Characterisation                   |

|    | 2.3   | The AAL2 Specification and AAL2 Trunking |

|    | 2.4   | AAL2 Switching                           |

|   | 2.5  | Evaluation Metrics                                            | 31 |

|---|------|---------------------------------------------------------------|----|

|   | 2.6  | ATM Switch Requirements                                       | 32 |

| 3 | Syst | tem Design for the AAL2 Switch                                | 35 |

|   | 3.1  | Introduction                                                  | 35 |

|   | 3.2  | Switching Node Functional Requirements                        | 37 |

|   | 3.3  | System Definition                                             | 40 |

|   | 3.4  | System Design                                                 | 44 |

| 4 | wu   | GS Architecture                                               | 50 |

|   | 4.1  | Introduction                                                  | 50 |

|   | 4.2  | WUGS Base Switch Overview                                     | 52 |

|   | 4.3  | APIC NIC                                                      | 53 |

|   | 4.4  | The Smart Port Card                                           | 55 |

|   | 4.5  | NetBSD Operating Environment                                  | 56 |

|   | 4.6  | Integrating the WUGS Components with the AAL2 Switch          | 57 |

| 5 | The  | AAL2 Switch Architecture                                      | 62 |

|   | 5.1  | Introduction                                                  | 62 |

|   | 5.2  | System Overview                                               | 62 |

|   | 5.3  | Operation of the SPU and Processing of Events                 | 66 |

|   | 5.4  | Operation of the CCU                                          | 69 |

|   | 5.5  | Static (single-instance) and Dynamic (multi-instance) Modules | 70 |

|   | 5.6  | Functions and Organisation of the ADU                         | 70 |

|   | 5.7  | The PSU and Scheduling                                        | 74 |

|   | 5.8  | Operation of the ARU                                          | 76 |

|   | 5.9  | The Timer Unit                                                | 79 |

|   | 5.10 | Development Notes                                             | 82 |

|   |      | v                                                             |    |

| 6 | Eva | luation      | n of the AAL2 Switch                         | 83  |  |  |  |  |  |

|---|-----|--------------|----------------------------------------------|-----|--|--|--|--|--|

|   | 6.1 | Introduction |                                              |     |  |  |  |  |  |

|   | 6.2 | Source       | e Generator Requirements                     | 83  |  |  |  |  |  |

|   | 6.3 | Testbe       | ed Components                                | 85  |  |  |  |  |  |

|   | 6.4 | System       | n Calibration and Time-scale Normalisation   | 86  |  |  |  |  |  |

|   | 6.5 | End-to       | o-end Operational Evaluation of the AAL2 CPS | 87  |  |  |  |  |  |

|   |     | 6.5.1        | Maximum Efficiency Test                      | 90  |  |  |  |  |  |

|   |     | 6.5.2        | Standard Efficiency Test                     | 90  |  |  |  |  |  |

|   |     | 6.5.3        | Low Efficiency Test                          | 91  |  |  |  |  |  |

|   | 6.6 | AAL2         | Switch Evaluation                            | 91  |  |  |  |  |  |

|   |     | 6.6.1        | AAL2 Forwarding Test                         | 92  |  |  |  |  |  |

|   |     | 6.6.2        | AAL2 Path Compression Test                   | 93  |  |  |  |  |  |

|   |     | 6.6.3        | AAL2 Path Expansion Test                     | 95  |  |  |  |  |  |

|   |     | 6.6.4        | Signalling Packet Receive Test               | 97  |  |  |  |  |  |

|   | 6.7 | AAL2         | Performance Metrics                          | 100 |  |  |  |  |  |

|   | 6.8 | PDU          | Output Analysis                              | 101 |  |  |  |  |  |

|   |     | 6.8.1        | PDU Reduction with Small Packet Sizes        | 101 |  |  |  |  |  |

|   |     | 6.8.2        | PDU Reduction with Standard Packet Sizes     | 104 |  |  |  |  |  |

|   |     | 6.8.3        | PDU Reduction with Large CPS Packets         | 105 |  |  |  |  |  |

|   |     | 6.8.4        | Summary                                      | 106 |  |  |  |  |  |

|   | 6.9 | The P        | DU Efficiency Distribution                   | 107 |  |  |  |  |  |

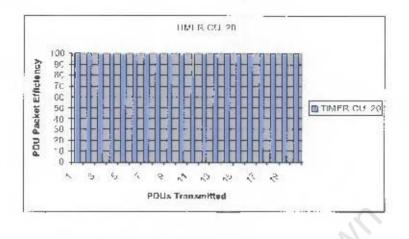

|   |     | 6.9.1        | Distribution with Small CPS Packets          | 108 |  |  |  |  |  |

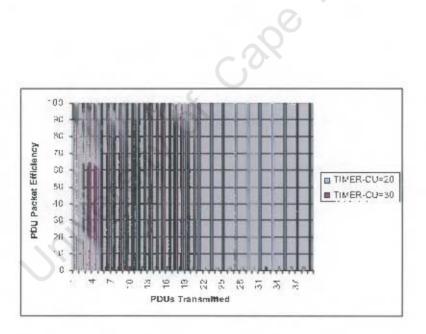

|   |     | 6.9.2        | Distribution with Standard-size CPS Packets  | 109 |  |  |  |  |  |

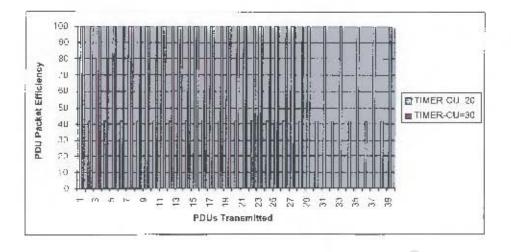

|   |     | 6.9.3        | Distribution with GSM-FR Packets             | 110 |  |  |  |  |  |

|   |     | 6.9.4        | Distribution with 44-byte Packets            | 110 |  |  |  |  |  |

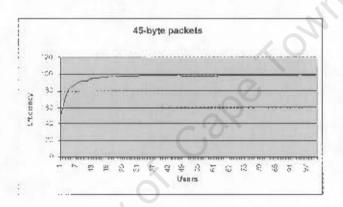

|   |     | 6.9.5        | Distribution with 45-byte Packets            | 110 |  |  |  |  |  |

|    |       | 6.9.6   | Distribution with Large CPS Packets                    | 112 |

|----|-------|---------|--------------------------------------------------------|-----|

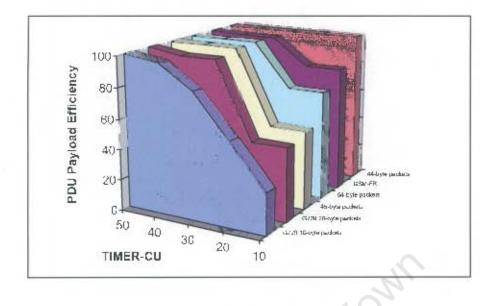

|    |       | 6.9.7   | Summary                                                | 112 |

|    | 6.10  | Multip  | le Users                                               | 113 |

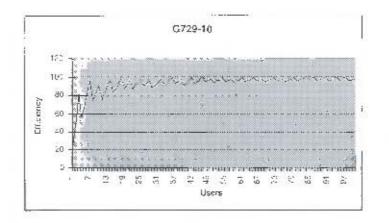

|    |       | 6.10.1  | Multiple Users Transmitting Small CPS Packets          | 114 |

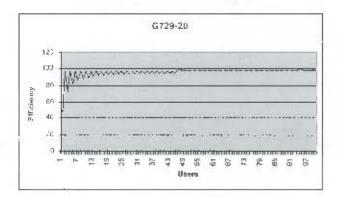

|    |       | 6.10.2  | Multiple Users Transmitting Standard-size CPS Packets  | 115 |

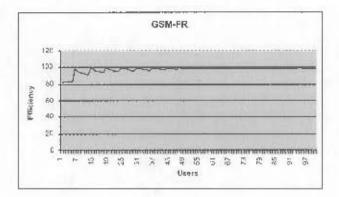

|    |       | 6.10.3  | Multiple Users with Large CPS Packets                  | 116 |

| 7  | Con   | clusior | IS                                                     | 119 |

| 8  | Rec   | ommer   | ndations                                               | 124 |

| Bi | bliog | raphy   |                                                        | 128 |

| A  | Trac  | litiona | l Methods for Transporting Voice in ATM and SSCS Exten |     |

|    | sion  |         |                                                        | 131 |

|    | A.1   | Introdu | uction                                                 | 131 |

|    | A.2   | Voice o | wer AAL1                                               | 131 |

|    | A.3   | Voice o | wer AAL5                                               | 133 |

|    | A.4   | SSCS I  | Extension to AAL2                                      | 133 |

| в  | SDI   | Nome    | enclature                                              | 135 |

|    | B.1   | Introdu | 1ction                                                 | 135 |

| С  | AAI   | L2 Swi  | tch Evaluation Test Suite                              | 137 |

|    | C.1   | Introdu | action                                                 | 137 |

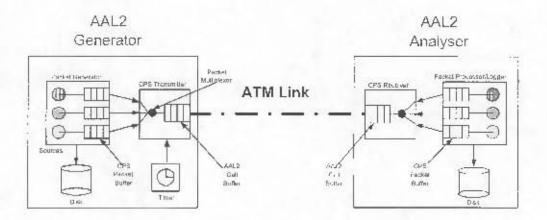

|    | C.2   | The A   | AL2 Generator                                          | 137 |

|    |       | C.2.1   | Implementation of the AAL2 Generator Timeout Mechanism | 141 |

|    |       | C.2.2   | Emulating Multiple Input AAL2 Paths                    | 143 |

|    | C.3   | The A.  | AL2 Analyser                                           | 144 |

ŧ

| D | Abs                                    | stract Data Type 14                                                                |                                       |                                                      |  |  |  |  |  |

|---|----------------------------------------|------------------------------------------------------------------------------------|---------------------------------------|------------------------------------------------------|--|--|--|--|--|

|   | D.1                                    | Introduction                                                                       |                                       |                                                      |  |  |  |  |  |

|   | D.2                                    | Generalised FIFO algorithm                                                         |                                       |                                                      |  |  |  |  |  |

|   |                                        | D.2.1 Functions for creating and destroying FIFOs                                  |                                       |                                                      |  |  |  |  |  |

|   |                                        | D.2.2 Standard Element Processing                                                  |                                       |                                                      |  |  |  |  |  |

|   |                                        | D.2.3                                                                              | Miscellaneous Options (non-mandatory) | 148                                                  |  |  |  |  |  |

|   | D.3                                    | Genera                                                                             | lised Linklist Algorithm              | 149                                                  |  |  |  |  |  |

|   |                                        | D.3.1                                                                              | Creating and Destroying Linklists     | 149                                                  |  |  |  |  |  |

|   |                                        | D.3.2                                                                              | Standard Linklist Operations          | 150                                                  |  |  |  |  |  |

|   |                                        | D.3.3                                                                              | Extended Operations                   | 151                                                  |  |  |  |  |  |

|   | D.4                                    |                                                                                    | Priority Heap                         | 152                                                  |  |  |  |  |  |

|   |                                        | D.4.1                                                                              | Initialisation                        | 153                                                  |  |  |  |  |  |

|   |                                        | D.4.2                                                                              | Standard Operation                    | 153                                                  |  |  |  |  |  |

|   |                                        |                                                                                    |                                       |                                                      |  |  |  |  |  |

| E | wu                                     | GS, AI                                                                             | PIC and SPC Usage Guide               | 154                                                  |  |  |  |  |  |

| E | <b>WU</b><br>E.1                       |                                                                                    | PIC and SPC Usage Guide               | <b>154</b><br>154                                    |  |  |  |  |  |

| E |                                        | Introdu                                                                            |                                       |                                                      |  |  |  |  |  |

| E | E.1                                    | Introdu<br>Setting                                                                 | action                                | 154                                                  |  |  |  |  |  |

| E | E.1<br>E.2                             | Introdu<br>Setting<br>Runnin                                                       | up of the WUGS Controller             | 154<br>154<br>155                                    |  |  |  |  |  |

| F | E.1<br>E.2<br>E.3<br>E.4               | Introdu<br>Setting<br>Runnin<br>Migrati                                            | up of the WUGS Controller             | 154<br>154<br>155                                    |  |  |  |  |  |

|   | E.1<br>E.2<br>E.3<br>E.4               | Introdu<br>Setting<br>Runnin<br>Migrati<br>L2 Swit                                 | up of the WUGS Controller             | 154<br>154<br>155<br>157                             |  |  |  |  |  |

|   | E.1<br>E.2<br>E.3<br>E.4<br>AAI        | Introdu<br>Setting<br>Runnin<br>Migrati<br>L2 Swit<br>Introdu                      | up of the WUGS Controller             | 154<br>154<br>155<br>157<br><b>160</b>               |  |  |  |  |  |

|   | E.1<br>E.2<br>E.3<br>E.4<br>AAI<br>F.1 | Introdu<br>Setting<br>Runnin<br>Migrati<br>L2 Switt<br>Introdu<br>AAL2 S           | up of the WUGS Controller             | 154<br>154<br>155<br>157<br><b>160</b><br>160        |  |  |  |  |  |

|   | E.1<br>E.2<br>E.3<br>E.4<br>F.1<br>F.2 | Introdu<br>Setting<br>Runnin<br>Migrati<br>L2 Switt<br>Introdu<br>AAL2 S<br>The AA | up of the WUGS Controller             | 154<br>154<br>155<br>157<br><b>160</b><br>160<br>160 |  |  |  |  |  |

# List of Figures

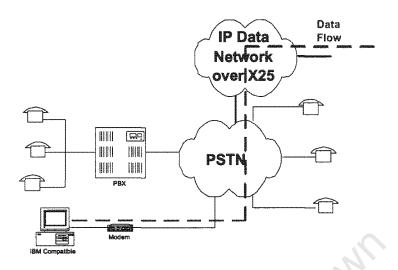

| 1.1 | Using the PSTN as an Access Network                                               | 4  |

|-----|-----------------------------------------------------------------------------------|----|

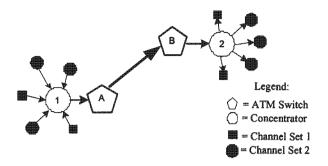

| 1.2 | The Benefit of Using AAL2 for Trunking Purposes                                   | 8  |

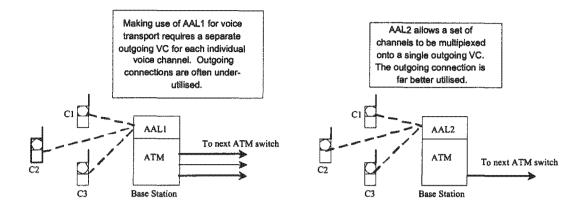

| 2.1 | Multiplexing Users onto an ATM Link using AAL1 and AAL2                           | 19 |

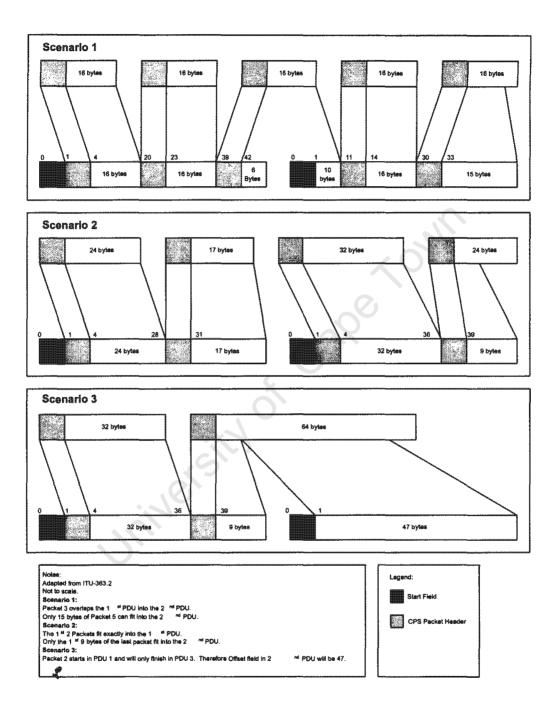

| 2.2 | Packing CPS Packets into 48-byte PDUs: Typical Scenarios                          | 22 |

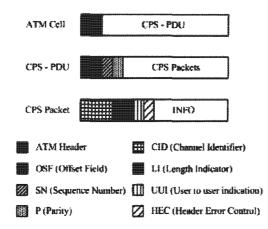

| 2.3 | CPS Packet Nomenclature                                                           | 23 |

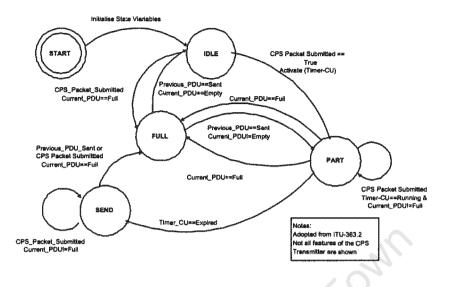

| 2.4 | CPS Transmitter State Machine                                                     | 25 |

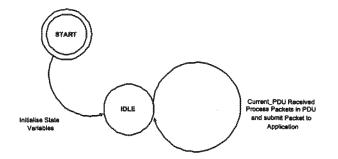

| 2.5 | CPS Receiver State Machine                                                        | 26 |

| 2.6 | Inefficient ATM structure for AAL2                                                | 27 |

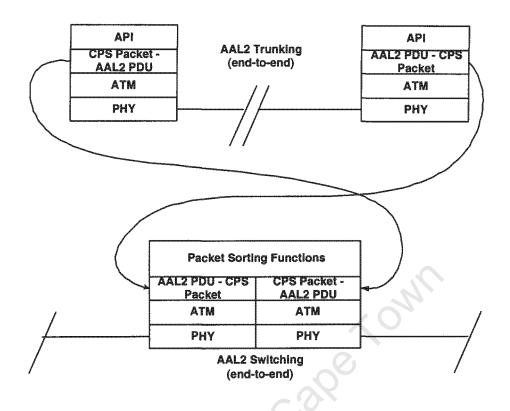

| 2.7 | The AAL2 Switch                                                                   | 28 |

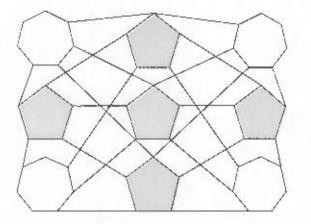

| 2.8 | ATM and AAL2 Switch Synergy                                                       | 29 |

| 3.1 | AAL2 Duality                                                                      | 36 |

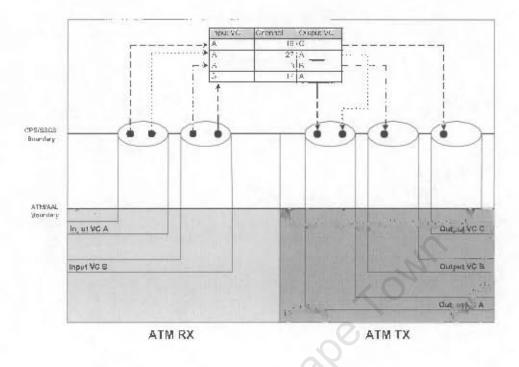

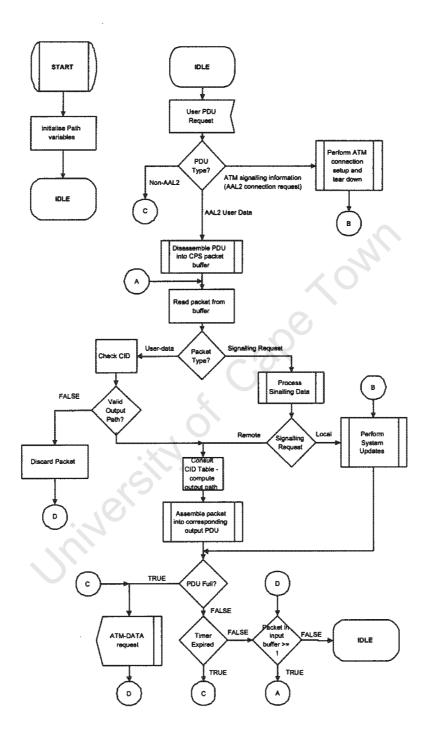

| 3.2 | SDL Representation of AAL2 Switching                                              | 41 |

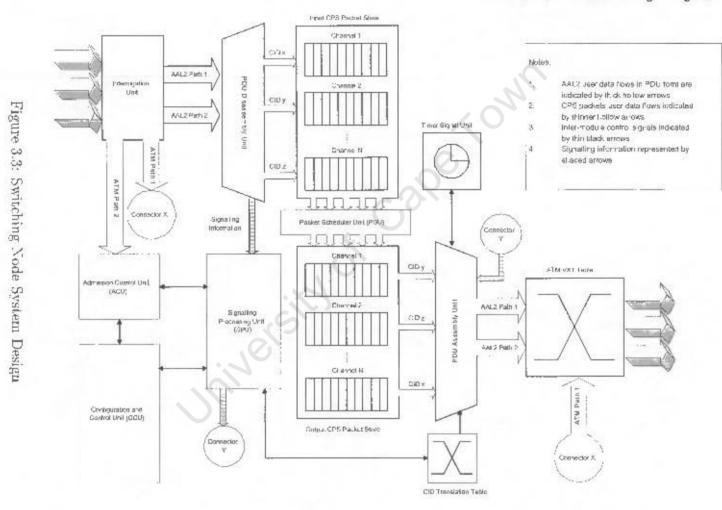

| 3.3 | Switching Node System Design                                                      | 46 |

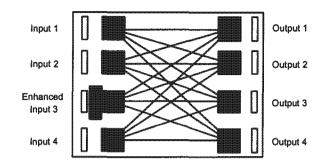

| 4.1 | Enhanced WUGS Port Functionality                                                  | 51 |

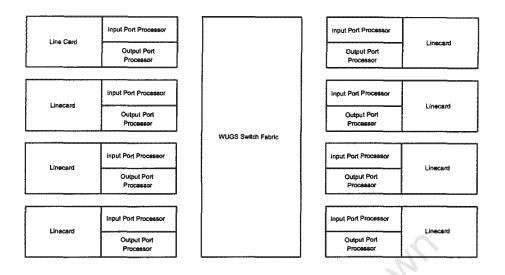

| 4.2 | WUGS Internal Organisation                                                        | 52 |

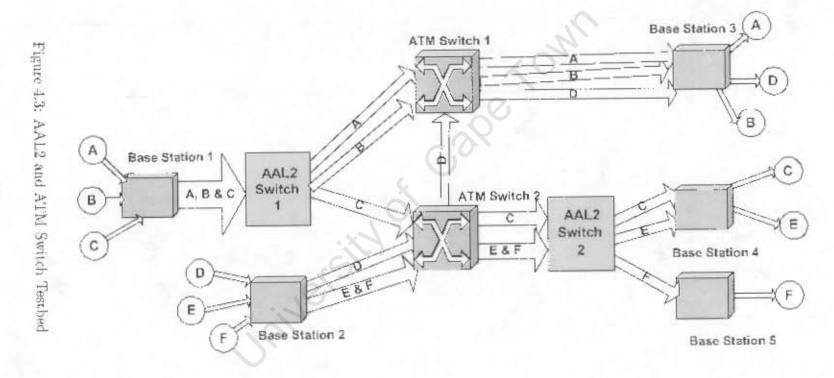

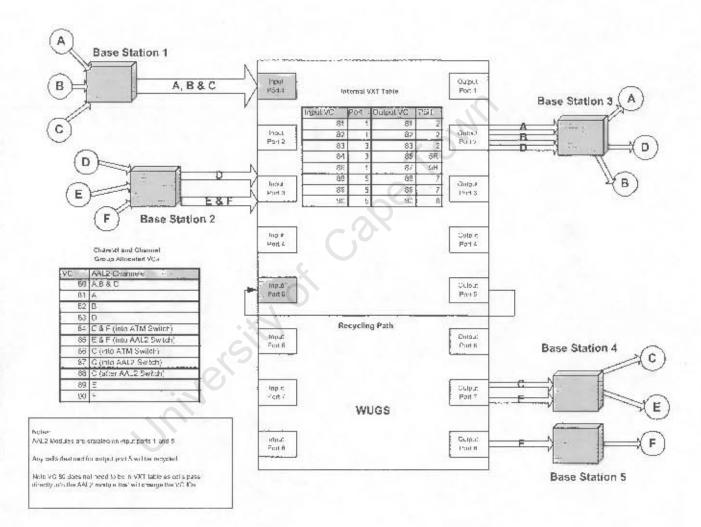

| 4.3 | AAL2 and ATM Switch Testbed                                                       | 60 |

| 4.4 | A Practical Solution for Creating AAL2 and ATM Switch Environments on<br>the WUGS | 61 |

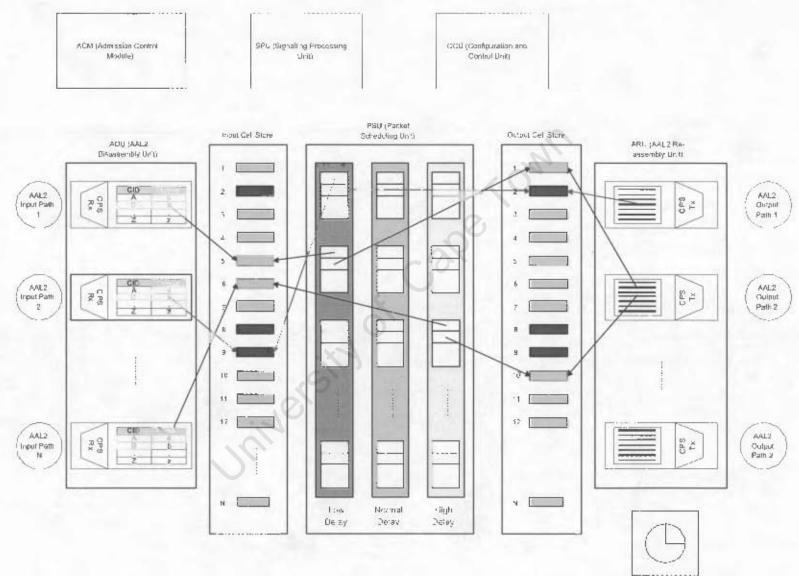

| 5.1 | Simplified AAL2 Switch Architecture                                               | 65 |

.

| 5.2  | Passing Message Ports as Events to the SPU                                             |

|------|----------------------------------------------------------------------------------------|

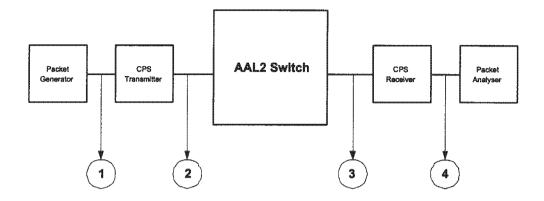

| 6.1  | Testbed Components to Evaluate the AAL2 Switch                                         |

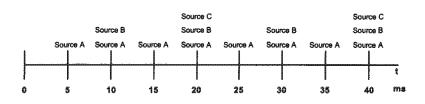

| 6.2  | Multiplexing Three Sources onto an AAL2 Link                                           |

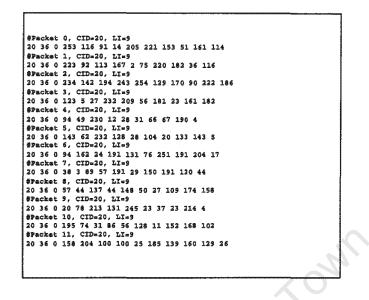

| 6.3  | CPS Packet Logfile showing 12 Packets, each of length 15 and CID of 17 $$ . 88         |

| 6.4  | CPS Packet Logfile showing 12 Packets, each of length 10 and CID of 20 $\therefore$ 89 |

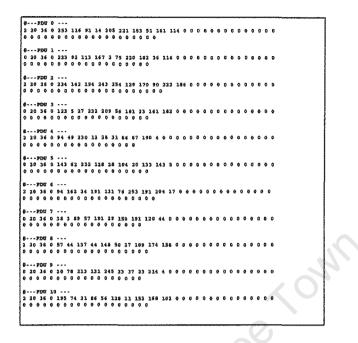

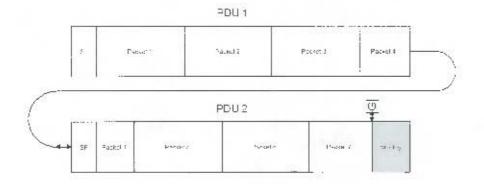

| 6.5  | PDU Contents for Large Timer-CU value                                                  |

| 6.6  | PDU Contents for Timer-CU of 20                                                        |

| 6.7  | PDU Contents for Timer-CU of 10                                                        |

| 6.8  | Analysing Data at Four Points                                                          |

| 6.9  | CPS Packet and AAL2 Traffic Logs from 2 Sources                                        |

| 6.10 | Routing AAL2 Traffic to Different Outputs                                              |

| 6.11 | Traffic Logs for 3 Sources                                                             |

| 6.12 | Concentrating 3 AAL2 channels on 2 AAL2 paths onto a single Output Path 99             |

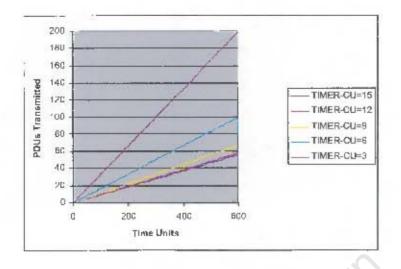

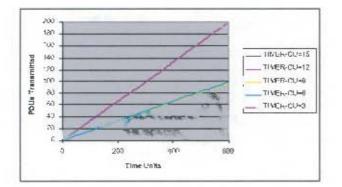

| 6.13 | Number of PDUs transmitted for 10-byte Packets 102                                     |

| 6.14 | 2 PDUs Required for Every 7 Packets Transmitted 103                                    |

| 6.15 | Number of PDUs transmitted for 20-byte Packets 104                                     |

| 6.16 | Number of PDUs transmitted for 40-byte Packets                                         |

| 6.17 | Efficiency Distribution for 20 G729-10 CPS Packets                                     |

| 6.18 | Efficiency Distribution for 20 G729-20 CPS Packets                                     |

| 6.19 | Efficiency Distribution for 20 GSM-FR CPS Packets                                      |

| 6.20 | Efficiency Distribution for 20 44-byte CPS Packets                                     |

| 6.21 | Efficiency Distribution for 20 45-byte CPS Packets                                     |

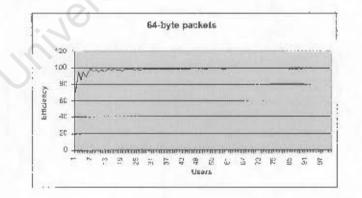

| 6.22 | Efficiency Distribution for 20 64-byte CPS Packets                                     |

| 6.23 | Efficiency Summary Graph                                                               |

| 6.24 | 100 users transmitting G729 10-byte Packets                                            |

| 6.25 | 100 users transmitting G729 20-byte Packets                                            |

| 6.26 | 100 users transmitting GSM-FR 36-byte Packets                       | 117 |

|------|---------------------------------------------------------------------|-----|

| 6.27 | 100 users transmitting 45-byte Packets                              | 117 |

| 6.28 | 100 users transmitting 64-byte Packets                              | 117 |

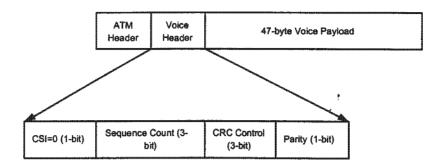

| A.1  | Encapsulation of Voice onto AAL1 Payload (Adapted from ATM Forum) . | 132 |

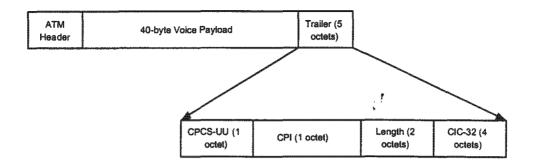

| A.2 | Encapsula | tion of | f Voice | onto | AAL5 | Payload | (Adapted | from | ATM | Forum) | ). | 133 |

|-----|-----------|---------|---------|------|------|---------|----------|------|-----|--------|----|-----|

|-----|-----------|---------|---------|------|------|---------|----------|------|-----|--------|----|-----|

university

## List of Tables

| 6.1 | Standard Compression Codecs                          | 85  |

|-----|------------------------------------------------------|-----|

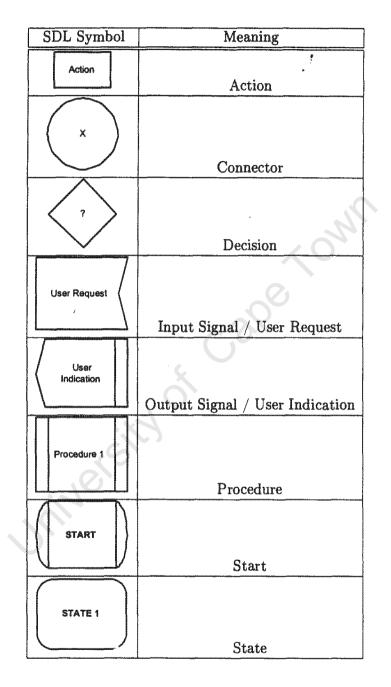

| B.1 | SDL Symbols used and their Meaning                   | 136 |

| C.1 | Source Inter-arrival Times                           | 142 |

| C.2 | Source Inter-arrival Times                           | 142 |

| E.1 | Commands to establish and tear down WUGS connections | 157 |

|     | University                                           |     |

### **Glossary of Terms**

For the convenience of the reader, this glossary is provided. These terms occur extensively throughout the text.

- ATM Asynchronous Transfer Mode. ATM is a cell-based technology that provides multiplexing gain, can utilise high-bandwidth carrier technologies and provides service guarantees.

- AAL2 ATM Adaptation Layer Type 2. AAL2 was re-standardised in 1997 for the multiplexing of short, variable length packets from various low-bit rate applications onto a single ATM connection.

- AAL2 Channel A unique AAL2 channel, characterised by a Channel Identifier (CID). Several AAL2 channels are multiplexed onto a single AAL2 path.S

- AAL2 Path Analogous to an ATM virtual connection when carrying AAL2-type traffic. An AAL2 path may contain up to 248 AAL2 channels.

- AAL2 Switching A specialised type of switching where a translation is performed based on the virtual path identifier (VPI), virtual channel identifier (VCI) and channel identifier (CID) of a packet, as opposed to the usual VPI / VCI translation that is performed in ATM switching.

- **APIC** ATM Port Interconnect Chip. A specialised ATM chip developed by Washington University in St. Louis for sending and receiving ATM cells.

- codec An algorithm capable of compressing or decompressing voice traffic. A codec may also be used to alter video streams if required.

- **CPS** Common Part Sub-layer. The sub-layer of AAL2 that is responsible for converting between CPS-packet format and AAL2 PDU format.

- **FPX** Field Programmable Port Extender. An FPX module contains a high gate-count FPGA on which designs may be implemented. An FPX resides between a line card and input port of the WUGS, and allows per-port packet processing to be achieved.

- **Packetisation Delay** The length of time taken to place information into the payload of an ATM cell. A large packetisation delay can adversely affect voice quality.

- **Poisson** A mathematical process used to model random arrivals. The probability of an arrival in a small interval of time depends only on the size of the time interval, and not on the past history of the process.

- **Socket** A logical abstraction mechanism, where a network device is represented as a single descriptor (value). Bidirectional data flow can occur by reading and writing to this descriptor.

- SPC Smart Port Card. An SPC is an embedded computer produced by Washington University for cell-based processing on a WUGS port. An SPC typically runs the NetBSD operating system and is equipped with an APIC for sending and receiving ATM cells.

- **Timer-CU** The timer mechanism used to ensure outgoing AAL2 cells are not stalled too long at the transmitter.

- **VXT** Virtual Circuit Translation Table. The internal WUGS table used to house ATM switch mappings.

- **WUGS** Washington University Gigabit Switch. An 8-port ATM research switch that has been open-sourced. A WUGS facilitates the development of cell and packet-based algorithms at both the hardware and software levels.

Univers

### Chapter 1

### Introduction

#### 1.1 Introduction

When communication networks began to emerge in the earlier half of the previous century, the primary form of communication that took place was in the form of speech, or what is commonly referred to as voice.<sup>1</sup> This was due to the fact that the technology to transmit information digitally simply did not exist at that time. However, being able to transmit voice from one location to another was soon regarded as a significant stepping stone, and soon resulted in voice-based transmissions forming an integral part of everyday life. Even in the modern-day world where other services such as video, text and data are present, being able to transmit and receive voice is still considered as the "number one" priority service by many, and hence voice based-applications have received their due share of attention. Therefore in the context of information transfer, voice has formed part and parcel of communication networks since their birth, and it is unlikely that it will become any less-entrenched in the future.

Voice, just like other services such as video and data, is generated from applications which reside at the access point to the network. This point of access need not be a physical link to the first switch in the network, but could well be, and usually is, an interface to a typical network-based Application Programming Interface (API) suited to that particular application. Applications that fall into almost any category have certain requirements (some more stringent than others) that must be met by the network technology, or else the

<sup>&</sup>lt;sup>1</sup>Strictly speaking, telegraphy was the first form of communication to exist.

application will perform poorly end-to-end and may even fail, and voice applications are certainly no exception to the rule. Obviously the most important requirement that must be satisfied for voice in a point to point call is somehow ensuring that the voice information reaches the other end in a certain time limit, which should never be violated. Such a time limit has in fact been suggested in the literature [29] to be no longer than 150ms. If the time it takes for voice to travel from the source to the destination, through a given network, exceeds this limit, such as in a typical telephone call for example, it may become uncomfortable and even disturbing to maintain the conversation for the parties affected at either end. Another phenomenon that can severely affect the quality of voice is known as jitter, where the voice information does not arrive in a constant form at the receiver, but instead the rate fluctuates, causing unwanted glitches. Further requirements do exist for voice applications, but it should suffice at this point to say that voice itself is quite evidently a sensitive application, and that a network technology that is deemed suitable for transferring such information should at least be able to conform to these basic requirements, namely meeting minimum delays and ensuring at the receiver that information is available and can be unpacked both on time and at a constant rate.

Traditional methods for encoding a voice stream take an analogue signal, in which the fluctuations are proportional to the amplitude of the user's speech, and digitise this information at fixed time intervals. The samples are then digitally encoded and transmitted, at a fixed rate of 64 kbps into the entry point of a synchronous network, today known commonly as the Public Switched Telephone Network, or PSTN. This method of encoding voice has been used for many decades and is in fact still in use today around the world.

In the early seventies, when the PSTN was already firmly entrenched and switching many telephone calls world-wide, parallel work had begun in North America by the Department of Defence to create a suitable redundant data network that would span the continent [1]. The protocols responsible for transferring data in this network later evolved into what is today known as the Internet Protocol (IP) and these data networks soon connected all continents on the globe to form the Internet. IP networks were, of course, originally intended for carrying data information. The intention of the IP protocol was to create a layer-3 logical inter-working technology, that would not depend on the underlying physical network architecture. These networks were vastly different to the traditional PSTN based networks in that the information (data in this case as opposed to voice) was carried in the form of asynchronous packets instead of frames filling up synchronous time-slots. Therefore these networks only transmitted data when it was necessary to do so and hence the total

bandwidth available could be allocated at all times to all the active connections, and not necessary all connections, both active and inactive. However, these networks could not operate for long before becoming congested, with the obvious result that applications' data would sometimes take longer to traverse the network than usual, and that the path taken each time through the network would not be the same. This shortcoming however, was not regarded as a problem for data as data does not have the same sensitive requirements that voice has. Two main constraints for voice that can be relaxed for data is firstly the endto-end maximum allowed duration that will be tolerated, as well as the constant manner in which traditional voice is required to be transmitted to avoid jitter. Latency and jitter are not factors of concern for non-real-time applications, such as data. However, data transmissions cannot tolerate lost information in the network. Therefore as voice and data are radically different applications, it is scarcely surprising that two separate transmission networks have evolved over the years.

As the PSTN was around many years before data networks emerged, and since almost all homes and offices have access to the telephone, it made sense to use the telephone connection as an access technology for data networks, such as X25 networks, as shown in Figure 1.1. It was simply not possible to provide each and every customer with a direct data pipe to their home. When the Internet started becoming common-place, it was not feasible at the time to provide a separate data connection for each customer. Therefore to gain access to this central data network, customers' data was converted to an analogue form before entering the telephone network, where the digital information would eventually reach the packet-based network as data.

As the resources provided by data networks advanced, particularly bandwidth, new applications were born that tried to use these resources to provide additional services such as speech and low quality video, and hence it was no longer suitable to use the PSTN as an access network. The ISDN model was therefore soon introduced which allowed the PSTN for the first time to be a carrier for these multimedia services at a rate of 128 kbps.

In the early eighties, work had already begun on a new cell-switching technology known as Asynchronous Transfer Mode (ATM) to provide a network model that would be entirely application driven. In Europe, the driving force behind this technology was J.P. Coudreuse, from the CNET Prelude Project, who wanted to see a tight integration between services and cell-based switching networks. In the United States, Jon Turner from Washington University had been conducting extensive research on cell-switches, and their practical deployment in the enterprise [3]. Jon Turner is considered by many to be the father of

Figure 1.1: Using the PSTN as an Access Network

ATM, not because he was the inventor of this technology, but because of his driving force behind ATM research [2].

ATM, the technology of choice for the broadband ISDN model, is able to guarantee the support of four primary classes of service, which represent all possible traffic types that may occur in the network. ATM technology is independent of the underlying physical technology. Although work has been done on supporting voice calls (uncompressed voice) over ATM, the PSTN still remains the primary technology to support telephone traffic.

Before ATM technology had been seriously considered for voice, researchers had already been investigating the feasibility of transporting voice over IP networks. The interest in pursuing research in this area was sparked by the pure economies of these networks. Due to the success of the Internet, the exponential increase in the total bandwidth of these networks to support data applications resulted in decreased costs for consumers. This reached the extent where it was considered a viable option to attempt voice transmissions over data networks, as bandwidth-hungry data applications had already surpassed voice bandwidth requirements. The first requirement to transmit voice over a packet-based network was to present the voice information in a suitable form, i.e. as packets offered to the network, carrying "chunks" of digitised voice. As indicated above, IP networks are capable of offering best-effort delivery of data, and the same would apply to the treatment of voice packets, as logically, the network cannot distinguish these two traffic types in their packetised form. One way of trying to avoid congestion in IP networks, that does not provide much guarantee, is to simply produce less data, or digital voice samples per second in this case. In order to provide voice as a lower bit-rate application than usual, compression techniques are required.

Compression algorithms usually manifest themselves as codecs at the originating and receiving end of the voice channel. The nature of voice itself makes it possible to implement highly effective compression algorithms, some that are capable of reducing the voice bitrate by a factor of eight. This is due to the fact that a large portion of speech contains silence (almost fifty percent [23]) and can be completely eliminated. The silence, or instead, comfort noise, is re-inserted at the receiving end. Reducing the rate at which voice enters an IP network can help to improve the network's response in propagating the voice information, but still nothing can be said about any guarantees that the network can provide. Furthermore, if the network does suffer somewhat from variations in delay for example, buffers can be inserted at the receiving end to allow a constant play-out of the voice information. Although it is possible to transmit voice over IP, IP networks are inherently incapable of providing hard real-time guarantees that voice requires.

Up to this point we have only considered the transport of voice in fixed networks. In the striving to make applications, particularly voice, as mobile as possible, extensive focus has been placed on so-called "last mile" or access technologies, particularly in wireless devices such as cell-phones, voice-enhanced PDAs and various wearable devices. There have already been reports of the number of mobile handsets in use exceeding that of fixed devices in certain geographical areas. One limitation these devices must all deal with is very limited bandwidth imposed by scarce spectrum resources. Spectrum is an expensive resource, where only a limited band can be allocated per operator, and hence it is critical that network operators make full use of their allocated bandwidth to get good returns on their investments. Radio access technologies are steadily improving and those already successfully implemented include TDMA and CDMA. A discussion of how these operate does not fall within the scope of this document. However, it is worth mentioning that the data rates portable devices are able to sustain have steadily been increasing. Second generation or GSM portables support a data rate of 9.6kbps, GPRS supports a data rate of 168kbps (currently implementations are closer to 21kbps) and 3rd Generation (3G) devices already offer data rates of 384kbps and are expected to offer 2Mbps data rates in the near future. To maximise the limited spectrum resources that are available, one again turns to compression techniques, but in a wireless medium, compression plays a far more important role and is mandatory. A highly effective algorithm that may be deployed in presentday 2nd Generation cellular networks is CS-ACELP (Conjugate Structure Algebraic Code Excited Linear Progression), that is capable of compressing a 64kbps voice stream into a mere 8kbps.

The drawbacks in utilising traditional synchronous networks for low bit-rate voice are obvious. There is a distinct mismatch of the information rate of the traffic source and the channel bandwidth of a network connection. Traditional multimedia services require large amount of bandwidth to operate effectively, and it is assumed the bandwidth exists to support these services. Low bit-rate services are quite different to these traditional services, and do not operate efficiently when trying to match them with existing network infrastructures. These differences help one to understand why existing network infrastructures are no longer suitable. Due to voice compression the parameters describing the traffic source entering the fixed network are vastly different to those of an uncompressed audio source. In the latter, information enters the network from a terminal at a constant bit rate (the inter-arrival time between samples is constant). Upon compression, redundant information is no longer transmitted, resulting in traffic exhibiting more variable bit rate characteristics. The burstiness of the traffic varies according to a number of factors, but is primarily affected by the codec that is utilised in the handset or traffic source. For example, as shown in [4], the GSM Full Rate (GSM FR) is a speech codec that produces a 36-bytes voice packet every 20 ms during the speech burst with a rate of approximately 13 kbps. For CS-ACELP, a 10 byte packet is produced 10 ms during the on period (during speech) at a rate of 8 kpbs. As the on and off times of speech are not deterministic, the traffic produced by these codecs is hence quite bursty in nature.

The VBR (Variable Bit Rate) nature of the source implies that as traffic is only sent for a portion of the time period, the waiting synchronous network must somehow insert redundant information into information payloads to ensure that framing constraints are not violated. Another issue that needs to be taken into account is the fact that in many networks, compressed data entering the network needs to be uncompressed in order to be transmitted effectively across the synchronous network. Each time compression or decompression takes place, further unwanted delays are introduced along the connection path, which is an undesirable effect. One not only requires a network that can provide statistical gain by operating asymmetrically, but also one that can form a good core technology, where services do not need to be further mapped onto an existing underlying physical network. For example, the frames from IP traffic are often mapped onto a frame-relay or ATM transport network while traversing the public network, as there are currently no wide area Ethernet infrastructures in place<sup>2</sup>. By continually having to alter the data structure by adding additional overhead to packets as they pass to the lower levels of the network, errors, delays and protocol-mismatch become common-place.

ATM, itself a cell based networking technology, offers good support for constant bit rate traffic as well as bursty traffic. ATM has always offered support for circuit switched voice over an Adaptation Layer known as AAL1. However, AAL1 is not efficient when transmitting lower bit rate voice, mainly due to the packetisation delay. The packetisation delay, the time it takes to create an ATM cell with voice information, grows inversely proportionally to the bit rate of the voice. Therefore it will take far longer to packetise voice data from a low bit-rate source, requiring some enhancement to be made to ATM<sup>3</sup>.

For this reason, the ATM Forum has devised a new adaptation layer known as AAL2, standardised by the ITU in 1997, that caters for delay-sensitive, bursty and low-bit rate traffic, particularly voice. Essentially, what AAL2 does is to multiplex several packets (sometimes called mini-cells [23]) of low-bit rate sources into a single ATM cell before transmission. By multiplexing packets into cells, the probability of traffic being available at a given instant is much higher, with the result that cells can be sent off more regularly, eliminating delays. In the event that an AAL2 cell payload does not fill up within a specified time period, a timer will expire and ensure that the current cell, full or not, is dispatched.

While ATM is certainly the most sensible choice when it comes to multiplexing the diverse traffic types that are characteristic of today's services, it does present its own problems. Firstly the transfer delay between source to destination of a cell (or frame) is not as small as that of most circuit switched networking architectures. Secondly, ATM may prove to be less efficient than traditional TDM systems due to the cell overhead imposed [6]. It is also for these reasons that telecommunications operators who want to use ATM have been so willing to try out AAL2 technology for voice - the multiplexing gain provided by AAL2 can reduce the above side-effects of traditional ATM-based voice transport quite substantially.

AAL2 was initially intended for trunking purposes as shown in Figure 1.2. Here the voice information from various sources is packetised and multiplexed into ATM cells along a single ATM virtual connection (VC). Two problems may occur with AAL2 trunking that will be covered in more detail in Chapter 2. The first problem is the inability of AAL2 to

$<sup>^{2}</sup>$ Resilient Packet Ring Technologies may extend Ethernet past the local area network, but their scalability is considered limited.

<sup>&</sup>lt;sup>3</sup>Efficiency comparisons in ATM will be covered in more detail in Chapter 2

Figure 1.2: The Benefit of Using AAL2 for Trunking Purposes

multiplex voice from the output of different codecs, e.g. multiplexing voice from a GSM Half Rate codec and a CS-ACELP codec<sup>4</sup>. The receiver will not know what codec to apply to the retrieved packets, as it will have no idea how they were formed. Secondly, if a single ATM VC carrying separate channels is copied to two destinations, all the AAL2 sub-channels will be carried in the VC for each direction, instead of sensibly carrying only the sub-channels that are required at the destination.

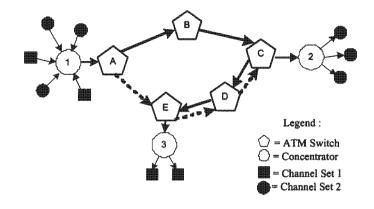

These problems have resulted in increasingly more focus being placed on AAL2 switching [23]. An AAL2 switch is capable of disassembling AAL2 cell payloads into the individual short voice packets, grouping those packets destined for each separate destination onto the appropriate queue, and finally recreating AAL2 cells from the re-grouped packets before dispatching them to the following node(s) in the network. This is made possible due to the fact that each voice packet in an AAL2 connection has an additional information field, viz. the CID or channel identifier. Since the goal of AAL2 is to multiplex several channels onto a single ATM connection, a scheme must exist whereby individual channels may be identified. The CID is therefore used to assign unique identifiers to each individual channel. Therefore it is possible to perform logical AAL2 switching at the VPI / VCI / CID level instead of ATM switching at the VPI / VCI level.

#### 1.2 Thesis Objectives

This study will focus on the design and implementation of an AAL2 switching node. It was made clear at an earlier stage that more emphasis needs to be placed on the core

$<sup>^{4}\</sup>mathrm{Suggestions}$  have been made to use the UUI field in CPS packet headers to attempt to address this issue

functionality of the network to suit the applications that will drive the network. Alongside W-CDMA and OFDM, AAL2 has been regarded as an excellent solution to the problems and challenges imposed by future UMTS/IMT-2000 and 4th generation systems [4, 6]. There have been investigations on how far AAL2 technology should extend towards the end-user along a possible access network, but these studies will focus on AAL2 purely at the core network level, and assume existing access protocols.

Most importantly at this stage though is the question of exactly which services the proposed AAL2 switch is expected to provide. Naturally, the switch should be able to perform the AAL2 switching discussed above. It should not only perform the switching correctly (header translation) but in addition it should be robust, scalable and efficient. The AAL2 switching level should be completely isolated from the ATM level. In other words, the AAL2 network and addressing should be logical. The AAL2 switch should appear as an ATM switch to other ATM switches. The switch should also be intelligent enough to distinguish between AAL2 cells and non-AAL2 ATM cells, which shall henceforth be referred to as standard ATM cells.

As the implementation of an AAL2 switching node is highly specialised, and given the fact that AAL2 is a relatively new technology, there were no commercial tools available when the project was initiated, that would have made it possible to implement a suitable design. Although it is possible to implement a simplistic design on a high-performance FPGA, the resulting design would be non-practical, and extensive expertise would be required to provide the supporting link interfaces to allow the system to operate. Furthermore commercial vendors are often unwilling to provide customisable hardware to the research community. For this reason, Professor Jon Turner at Washington University in St. Louis had initiated a programme in 1999, funded by the National Science Foundation and DARPA, to provide a high-performance eight-port research switch to a number of universities around the world. These switches to date have been used very successfully to implement a selection of highprofile research projects (some non-disclosed)<sup>5</sup>. Based on the success of the programme, and the suitability of the hardware, it was hence decided to purchase one of these research switches from this university, known as the WUGS (Washington University Gigabit Switch) to implement the AAL2 switching node design. Washington University have also designed and made available an embedded computer capable of intercepting ATM cells between a link interface and the ATM switch fabric, which allows one to implement an active pro-

<sup>&</sup>lt;sup>5</sup>Information on this programme can be found at the following URL: http://www.arl.wustl.edu/gigabitkits/

cessing module, in this case the system architecture for an AAL2 switching node. At a later stage, Washington University released an adapter card with a programmable FPGA and supporting link circuitry, which the author and colleagues are seriously considering for future work in this field. Chapter 4 will provide a more in-depth introduction on the WUGS and associated components.

Many papers have focused on performance metrics for AAL2 technology [7, 8] and have used both analytical methods and simulation to come to conclusions how various metrics are related to the performance of a design. The intent of these studies is to compare the functionality and performance of the switching node with results suggested in the literature which will aid in obtaining conclusive results. Of particular interest will be how well the AAL2 technology for the switch scales with an increase in the number of users for a given link bandwidth, the effects on varying the packet sizes from the incoming voice streams, the efficiency of attempting to send large data packets through the switch, and what effect the AAL2 timer mechanism will play on the efficiency of the outgoing traffic payloads.

The goal of designing and implementing an AAL2 switch on the WUGS will form the first phase of a five year project which may well be continued beyond that point. The design will take into account further extensions that are to be incorporated into the switching node to enhance its functionality. The primary enhancement, which is currently being researched by a colleague of the author, will be AAL2 signalling. AAL2 signalling is a separate signalling protocol that is used in the creation and tear-down of AAL2 connections, communication of AAL2 switches in a network, updating AAL2 routes in a network and various other essential services. AAL2 signalling is a logical signalling entity and does not exist at the ATM layer. It relies on reserved AAL2 channels that are made available at system startup. A good overview of AAL2 signalling requirements can be found in [4, 9].

### **1.3** Scope and Limitations

While the author realises that there are a large array of factors that can enhance the performance of the AAL2 switch at hand, these studies cannot address every issue that could impact on the performance of the design.

The operating system of choice for running software on the Washington University's embedded computer is NetBSD 1.4.1. This OS was not selected by the author, but instead by Washington University as a suitable operating system on which to implement active

💑 **A** 0

network designs for the Smart Port Card. Although NetBSD is a well-structured operating system and offers good performance, it is not a real-time operating system, and hence the mechanisms found in real-time systems, particularly scheduling mechanisms, which could enhance the performance of the switching node, are not possible to implement in this instance. The author has decided to use NetBSD in the implementation phase, as focus on implementing real-time mechanisms would require extensive further research and hence draw the attention away from the principle purpose of this study, i.e. of implementing a functional AAL2 switching system. However, the author is fully aware of the enhancements that a real time OS can provide, and will make recommendations at a later stage for a suitable OS.

The minimum timer resolution offered by NetBSD is only 10 ms. Although this does not affect the number of users that may be supported (a faster machine need only be supplemented to support more users), it certainly does play a role in what voice codecs may and may not be supported. To date, the codec with the shortest packet inter-arrival time is G729, which produces packets every 10 ms. However, codecs requiring better network response are continually being researched, and are likely to soon be available.

Although the WUGS is itself considered as a high performance ATM switch, it does have its limitations with regard to link speed at each port on the switch. For a very large scale implementation to support many users, the performance increase by placing the active networking modules at the input side of the switch could result in much improved performance, as the output of the module would have available of N x Link Speed, where N represents the number of ports on the WUGS (currently 8 ports). Fortunately however, the combined user bandwidth in the implementation and tests is expected to be small.

Due to internal constraints and design simplification, the ATM link chip known as the ATM Port Interconnect Chip (APIC) that is responsible for transmitting and receiving ATM cells can only carry a maximum of 256 separate channels or Virtual Connections (VCs) at any given moment. This will also have a direct influence on the number of AAL2 users that can be supported. As a maximum of 248 AAL2 users are allowed per connection, this will give a theoretical total of 65000 separate AAL2 connections that can be permitted on each port of the WUGS.

### **1.4** Thesis Outline

The remainder of the document is organised as follows:

- Chapter 2 begins with an overview of voice, the principle application to drive AAL2 technology. A short study of the nature of voice traffic is essential, to enhance the reader's understanding of the various real-time requirements that would be placed on a transmission network. The manner in which voice traffic can be multiplexed over an ATM connection using AAL2 is then discussed in further detail, with particular reference to the transformation phase between voice packets and AAL2 PDUs. Since AAL2 promises efficient voice transfer over an ATM network, its performance against AAL1 and AAL5 is compared. The limitation of using AAL2 as a trunking technology is then investigated, and why one ought to extend a given network to support AAL2 switching. AAL2 switch concepts, as proposed by various researchers in the field, are presented, as well as performance metrics that may be used to judge a switch's operation. As the AAL2 switch will be implemented as an integral component of a larger ATM switch, ATM switch performance principles are also covered, and how they would affect the transfer of real-time voice.

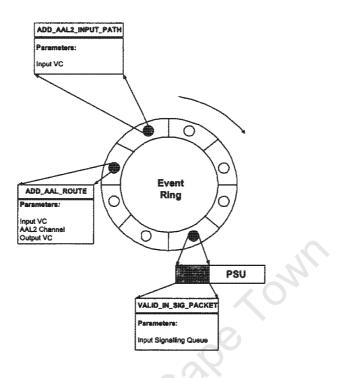

- In chapter 3, the focus is shifted towards the design of an AAL2 switch architecture. The requirements in terms of supporting the transfer of real-time voice over an AAL2 connection, with an extension framework for AAL2 signalling, are first mapped into a requirements specification. This specification will show the typical path through the AAL2 switch, that would be taken by AAL2 cells and CPS packets, and corresponding actions that would be taken at each stage. A full design is presented, showing how the overall switching system may be broken up into a series of modules that operate independently from one another, and how each one is responsible for a small switch function. Finally, the interface definitions between core modules will be discussed.

- Chapter 4 will discuss the WUGS architecture and the suitability of applying this architecture to an AAL2 switch. The reader will be shown how the proposed AAL2 module can be implemented onto an embedded computer, viz. the Smart Port Card (SPC) and how the SPC will integrate with the main Washington Switch. The interface chip for sending and receiving ATM cells, viz. the APIC, is discussed in detail and several of its advantages and drawbacks are highlighted, as well as the reason why certain APIC features were made use of. Finally, the reader will be

shown how a typical test environment that is comprised of multiple components may be mapped over to a single Washington Switch.

- Chapter 5 will focus on the implementation of the AAL2 switch. Implementation choices, such as the use of threads, are justified. Each module will be presented in detail, and how the organisation and function of the module will address a set of requirements, as presented in chapter 3. Relevant issues with regard to the development of the switch will also be presented.

- In chapter 6, it will be demonstrated how the AAL2 switch will be tested. First the requirements for external testbed components will be discussed. The testbed will consist of two components, viz. a source client to generate AAL2 traffic and an analyser to receive traffic. A sequence of tests will be conducted on the switch as traffic is passed through. These tests will include establishing routes through the switch, and configuring the switch to condense and expand AAL2 routes. Finally, a set of experiments will be conducted to evaluate the efficiency of the AAL layer, and how the various performance parameters are linked to one another.

- Chapter 7 will present a set of conclusions that were drawn from these studies. These conclusions will present the order in which components were implemented, and what limitations were found to exist.

- Chapter 8 will present recommendations, which may be used to prescribe future work for an improved AAL2 switch architecture.

- Finally, a set of appendices are presented to provide further background information, as well as development specific details.

### Chapter 2

# Literature Review and Background Theory

### 2.1 Introduction

At this stage, the motivation for implementing an active switch based on AAL2 networking technology ought to be clear to the reader. In active network elements such as intelligent ATM switches and IP routers, the elements are capable of playing a much larger role in the transport and distribution of the traffic they pass around the network. Unlike passive network elements, which are merely capable of storing and forwarding data through the network, active network elements go a step further by performing some type of network transfer function on the traffic. As an example, an IPv4 router may be capable of interrogating the payload in IPv4 packets, and determining whether any IPv6 packets are being tunnelled - these may then be extracted and forwarded onto an IPv6 backbone network instead. Similarly, in the AAL2 switch being considered, the primary function of this switch is to perform AAL2 switching, as opposed to ATM switching. The only way this can be made possible is to physically remove the AAL2 sub-channels from the ATM cell stream before performing the central switching function. This can be seen as an active function, and hence the AAL2 switch can be considered as an active network element.

Before a design of any network element can be tackled, two important questions should be addressed, viz. Do all the modules comprising the switch and the switch itself function correctly, and how well does the switch perform in various operating environments, particularly those that are likely to place the system under stress. A system may be considered operational, but perform poorly under even the slightest load variations. On the other hand, a quick response time, perhaps considered as good performance, may result in unwanted alterations to the traffic and mis-insertion (switching of data to the incorrect output ports).

If the AAL2 switch is ever to perform adequately in any networked environment, it is necessary to have a good understanding of the type of application that will reside at the end points of the AAL2 switching network, in this case, primarily low-bit rate voice. This is of particular importance to ensure that the required mechanisms can be made to conform to a certain specification. One cannot set standards for network elements where the traffic is only vaguely understood. Hence a more detailed overview of the characteristics of voice traffic will be covered to aid the reader in understanding why components must meet minimum application requirements.

In order to address the issue of functional correctness, a thorough understanding of the technologies upon which the switch will be based is mandatory. A significant portion of this chapter will therefore' be devoted to the AAL2 technology itself, and how AAL2 can be realised initially as a trunking technology, and later in a switching technology. Research in the academic community has significantly aided cellular operators in making decisions whether to try AAL2 technology for their core networks, due to its suitability in supporting voice applications [23]. It is therefore imperative that one takes a look at such research in this chapter, in order to determine the current status of AAL2 technology, and to show what areas in this technology still requires attention. Various papers in the literature have suggested suitable metrics on which to base the performance of a typical AAL2 switch, and it will be shown how the results of these will assist in the evaluation of the switch architecture at a later stage.

#### 2.2 Voice Characterisation

The previous chapter introduced voice as a sensitive real-time application. Voice is particularly sensitive to end-to-end delays imposed by the network as well as delay variation. Some have argued that mean delay for voice is not a meaningful QoS measure for end-toend voice transport [19]. Instead, it has been suggested that one should rather examine the tail of the voice delay distribution, and quantify the overall fixed delay at the  $K^{th}$  percentile. When one wishes to analyse the side-effects suffered by voice when passing through a network, what is often more of interest is the ratio of successful, or uncorrupted packets that reach the destination over the total number of packets transmitted. As delay is the main contributor to voice degradation, we are therefore concerned with what percentage of packets will suffer as a result of a given fixed delay in the network. Clearly, increasing the delay will result in more packets arriving late at the destination, which may be unusable by the application. If one wishes to maintain a certain success rate, it is possible to vary the delay in the network, until we find the success ratio we require.

To reduce jitter on voice networks, buffers can be inserted at the receiving end. The purpose of such a buffer would be to ensure clock-recovery at the receiving end. If the buffer is too small, the receiver will be unable to smooth out the traffic successfully. If the buffer is too large, cell delays are once again introduced. The rate at which information is played out at the receiver will depend on the voice codec that has been selected to decode the information.

A subjective metric has been developed to evaluate voice quality, known as Mean Opinion Score (MOS). Various subjects are requested to evaluate the quality of voice in a session, and give a score from 1 to 5, where 1 is considered unacceptable quality, while a score of 5 is given to excellent voice quality. A lower score naturally indicates that more effort is required by the subject to interpret what is being said. A MOS of 4 is regarded as toll-quality voice. The MOS scale is often used to indicate what quality is sustained in the network.

When a voice source is compressed, two additional requirements are placed on the network. Firstly the rate at which the voice enters the network now varies, as opposed to the previous constant bit-rate stream for uncompressed voice. We refer to such voice traffic as variable bit rate traffic or VBR traffic, as opposed to constant bit rate traffic, or CBR traffic. The reason for this VBR nature is simple: compression algorithms are designed to remove redundancies in voice. Therefore during a period of silence there is no need to transmit any information, and hence the traffic source will remain idle during the period [18]. This would imply that, if one were to look at the shape of the traffic source over time, it would look very irregular, i.e. the envelope would contain many peaks and troughs, and would not look even. When the bandwidth level of a source is at its lowest (corresponding to a trough), it would be consuming the least possible bandwidth of the link, and hence more bandwidth would be available for other sources. Therefore during silence intervals, the network can make use of multiplexing gain to transmit the voice information from another source. However, when a user suddenly speaks, the network will be required to respond much faster and have a large instantaneous bandwidth to handle this new talk spurt.

The second requirement placed on the network when compressing voice is that the network should be more intolerant of any loss of information. In uncompressed voice and video, the loss of a few bits of information will have a minimum effect on the perceived quality at the receiving end. However, if a compression algorithm compresses a voice stream by a magnitude of four, losing one bit of information will be significant to losing four times the amount than in the uncompressed case, and the results in loss of quality will be four times that at the receiver. Therefore, the higher the compression ratio being achieved, the higher the network should prioritise the voice traffic path.

In the literature, numerous comparisons have been performed with telephony over both best-effort IP and ATM networks [30]. The large number of hops a packet can experience in an IP network will affect the end-to-end delay. Furthermore, the non-deterministic path that packets follow through the network will contribute to the overall delay variation (jitter), hence making it impossible to guarantee the quality of service (QoS) required by voice applications. The best performance achieved with voice over IP occurs in an under-utilised IP network, where compression is performed to lower the bit rate. For small intranets, this may appear to be an acceptable solution (simply provide more bandwidth) but in a core networking environment this is clearly unacceptable.

### 2.3 The AAL2 Specification and AAL2 Trunking

AAL2 was initially named AAL-CU (Composite Users) but the original technology that had been suggested for the segmentation and re-assembly of voice had become unpopular over the years, particularly due to its inefficient handling of voice packets. The ATM Adaptation Layer Type 2, or AAL2 was initially proposed by the ATM Forum and soon standardised by the ITU-T in late 1997, to support the delivery of short packets from variable, low bitrate and delay-sensitive applications[15]. This newer technology has completely replaced AAL-CU, and over the last number of years, has been drawing widespread interest from the research and industrial community.

The traditional way to encapsulate voice into ATM cells makes use of AAL1. AAL1 was suggested as a suitable adaptation layer for ATM for supporting circuit switched voice connections. As frames or packets of voice are sequentially removed from the input source, the bits are placed into the 48 byte payload of the ATM cell. Once full, the ATM cell is dispatched. In this case, the cell only holds data from one source. For 64kbps voice, where samples are arriving relatively quickly, the time taken to fill the ATM cell would be relatively short, and hence the *packetisation delay* will be small. However, packetising information from lower bit-rate, compressed voice sources has a serious effect in increasing delay[21, 19, 6, 14]. This is due to the fact that the traffic is bursty, and hence periods of time exist during which no information is generated. Furthermore, on average, voice information is arriving at a much slower rate than before, and hence the time taken to the fill the ATM cell is extended. As an example, the time taken to fill an ATM cell from a 64kbps voice source using AAL1 is approximately 6ms [6]. However, when reduced to 8kbps, the packetisation delay is increased to 48 ms, eight times as much. The packetisation delay is therefore inversely proportional to the bit rate of the voice source being considered, thus rendering AAL1 for voice is actually less efficient than traditional circuit switched networks, due to the cell-header overhead [16].

AAL2 has been designed to alleviate this drawback by multiplexing several low bit-rate connections into the payload of a single ATM cell. The chance that three voice sources are idle at any given moment is far lower than that of a single source. This implies that the time taken to fill an ATM cell from more than one source will be significantly shorter. As one is multiplexing several voice channels on a single ATM VC, further information is required to distinguish these channels on an end-to-end basis from one another. For this reason, each channel is identified by a separate ID, known as the Channel Identifier (CID), that is stamped onto the header of each packet carrying traffic for this channel. The principle of carrying multiple voice channels over a single VC as opposed to the first generation scheme of one VC allocated per channel, is shown diagrammatically in Figure 2.1 below.

Although AAL1 and AAL5 are not primarily intended for transmitting low bit rate voice over an ATM connection, it is still interesting to compare the efficiencies of these adaptation layers to that of the AAL2 layer. Briefly, AAL1 is intended to support low-delay CBR applications that are typically synchronous in nature. If the source information is structured, it is capable of restoring this structure at the receiver. In addition to this, AAL1 includes clock recovery mechanisms at the receiver to ensure synchronous operation [1]. AAL5, on the other hand, is intended for the transport of VBR data frames, which are typically longer than the ATM cell payload size of 48 bytes. These frames may be

Figure 2.1: Multiplexing Users onto an ATM Link using AAL1 and AAL2

transmitted in either a streaming mode or message mode, depending on the application requirements. The reader should be aware that neither AAL1 nor AAL5 offer multiplexing mechanisms in the Common Part Sub-layer (CPS), as there is no way of uniquely identifying separate flows on the same virtual connection<sup>1</sup>.

Various simulation models have been proposed to analyse the efficiency of AAL1, AAL5 and finally AAL2 voice sources [19]. In this study, this author assumes homogeneous voice sources, of varying bit rates, which are then applied to the input of his model. In the paper, this author is interested in the number of voice sources that may be supported, without violating a specified quality of service, which is given as a bounded 95 % percentile of voice, as described above. These experiments are repeated for all three adaptation layers, by varying either the bit rate or voice packet size. The results from these experiments are interesting, but not surprising. [19] has found that for uncompressed voice of 64kbps, AAL1, AAL5 and AAL2 are equally efficient, but for low-bit rate voice of 8kbps, which can be obtained using CS-ACELP, AAL2 is approximately five times more efficient than both AAL1 or AAL5, and that for voice packets up to 40 bytes in size, AAL1 and AAL5 perform identically. Furthermore, this paper concludes that for low bit rates, the total number of users than may be supported is very sensitive to the packet size chosen, while for high voice coding rates, varying the packet size does not necessarily increase the number of users that can be supported.

Other papers have investigated the possibility of increasing the number of users on an AAL2 channel by implementing several techniques that may reduce the quality of the

<sup>&</sup>lt;sup>1</sup>Note that LLC may provide multiplexing facilities, but at a higher-layer than ATM.

voice somewhat. Analytical performance models and results for AAL2 multiplexors that implement bit dropping on certain voice packets have been presented [15]. The author has assumed 32 kbps voice that would be produced by a ADPCM codec as defined in ITU-T G-727. Bit dropping is possible with AAL2 firstly due to the fact that one has access to the individual voice packets in the channel and secondly, for each channel, the information is arranged with the least significant bits containing the information of least relevance to the quality of the traffic. Dropping the relevant bits in the packet is far superior to previous techniques of employing cell dropping, which introduces once again unwanted packetisation delays [4]. Furthermore it it not easy to work out how many packets are being dropped in a cell, or the significance of the information loss. The bit-dropping model of above has suggested significant higher capacity, e.g. for  $\frac{1}{4}$  T1 channel. Applying these techniques almost doubles the number of users that can be supported, and approximately 30 % more users can be supported on a full T1 connection [15]. It was shown that it is possible to implement the bit-dropping shown above, and yet still retain a MOS of 4.

Still others have examined the suitability of AAL2 for transferring data packets. When 3G networks utilising AAL2 technology in the core have acquired a critical mass of consumers, value added services (text, low bit-rate compressed video, file-transfer) are likely to come next. It may be more feasible to transport these data services over AAL2 to simplify channel provisioning and billing in the AAL2 network. Furthermore, the need for dynamically creating AAL2 connections has given impetus to AAL2 signalling, which itself can be regarded as AAL2 data<sup>2</sup>. For these reasons, simulation models to investigate the possibility of transporting data over AAL2 have also been presented [4]. They have found that although AAL5 has slightly less overhead for packets shorter than 500 bytes, the difference in percent overhead between AAL2 and AAL5 for packets larger than 750 bytes is constant. Therefore, provided a Service Specific layer exists above the Common Part Sub-layer (CPS) for AAL2, it would be possible to segment these large packets for AAL2, and yet not sacrifice too much efficiency.

These findings will be valuable to the author in evaluating the effectiveness of the AAL2 technology considered for the switch. One is particularly interested in how the switch will respond to the range of traffic types suggested in the above simulations, and for each traffic type or codec, the number of users that may be sustained. Although these authors have suggested suitable efficiency metrics, they have focused on simulation models and analytical

<sup>&</sup>lt;sup>2</sup>Some signalling messages can be 129 bytes long, which is more than twice the maximum payload length (64 bytes) that is supported by AAL2

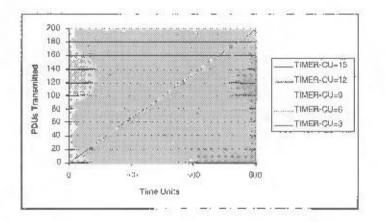

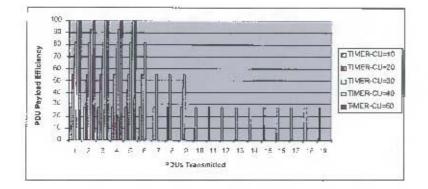

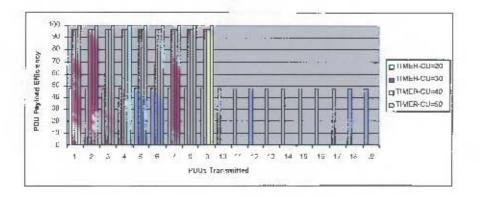

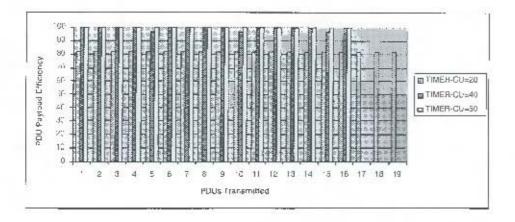

derivations. Traffic sources have either been Poisson [8] or Markov modelled [16], the talk period to total period ratio has been explicitly stated, processing delays in constructing AAL2 cells have been ignored, packets lengths and number of cells per packet are assumed constant [8] and in some cases queues for ATM cells are considered infinite. It is therefore of interest how real-world traffic and components will cooperate, and whether the efficiencies, delays and sustained load of a physical AAL2 switch will mimic these results or not. In a typical implementation, queues are expensive (memory may not always be available) and each queue adds unwanted delays. In addition, processing delays are very real in an AAL2 implementation, and if the wrong approach is opted for, this will impact no doubt on the performance.